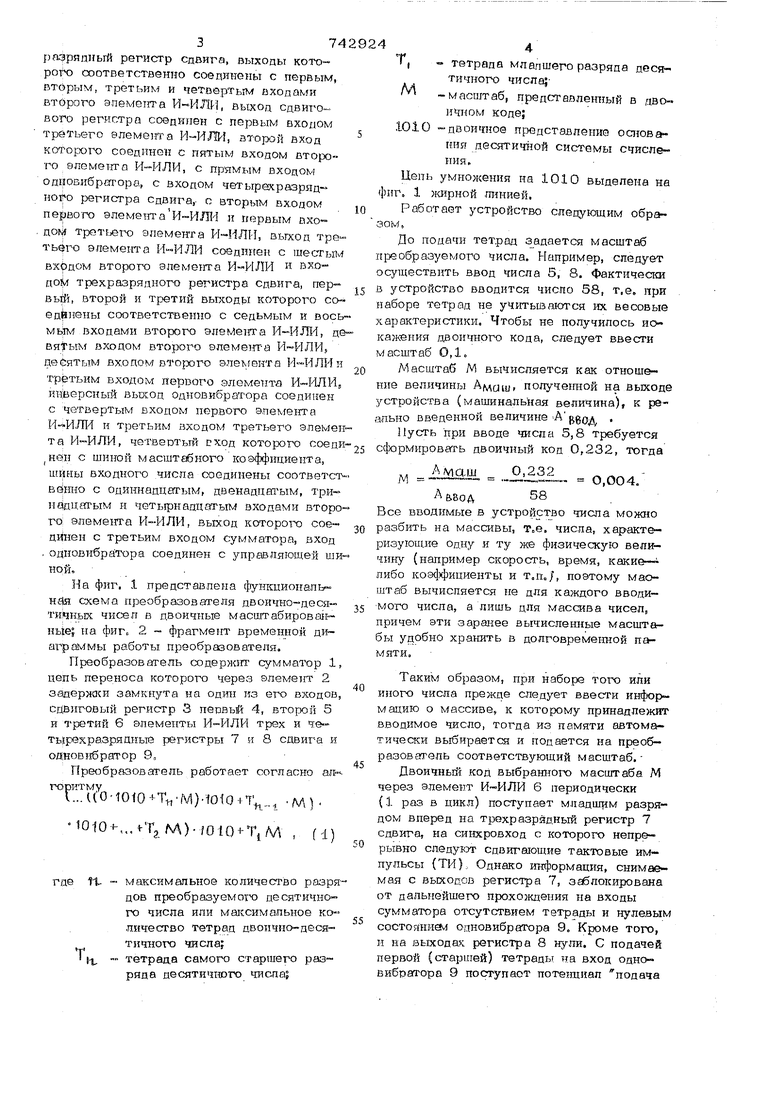

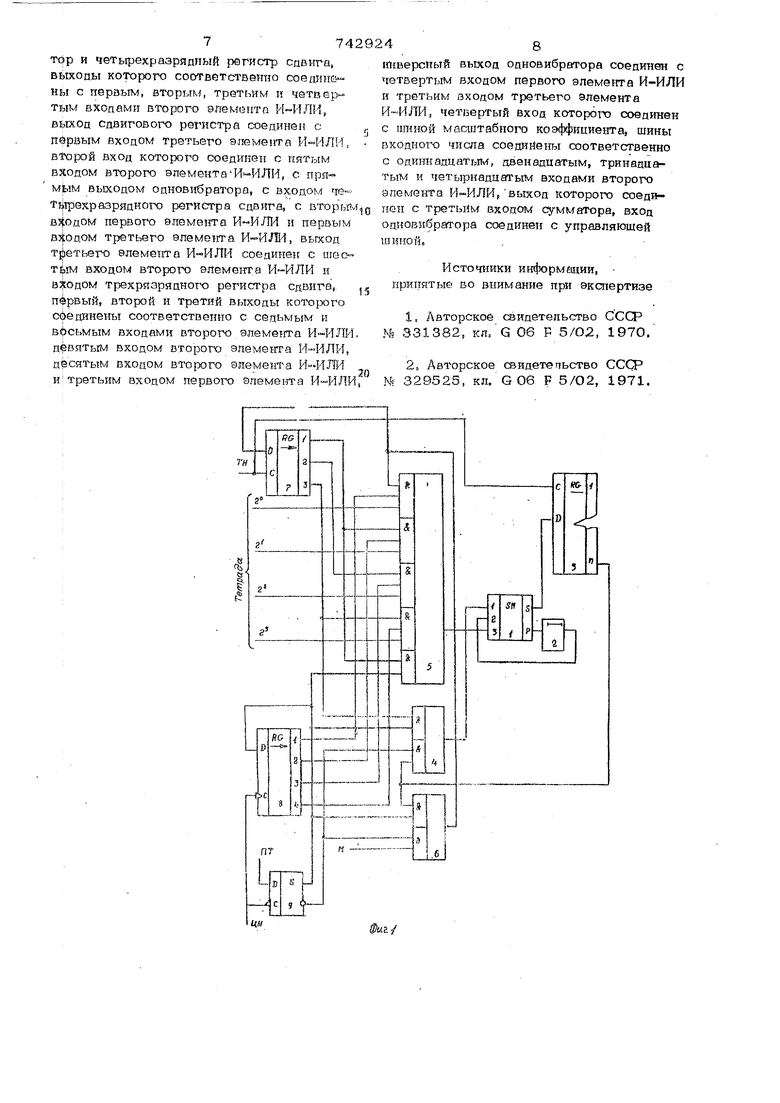

Изобретение относится к автоматике и вычислительной технике и может быть ио пользовано при построении цифровых yc ройств, осуществляющих преобразование информации. Известен преобразователь цвоичгно-десятичных чисел а двоичные, соцержащий бпок управления, распрецелитепь, переключ еггепь 8КВИВ апентов, запоминающее устройство пвоичных эквивалентов, регистр числа, двоичный сумматор и последовепгель но соединенный с ним регистр результата 11 . Недостатком этого преобразователя является отсутствие возможности масштйби роваиия двоичных чисел и большой объем необходимой аппаратуры. Наиболее близким по технической сущности к предлагаемому является преобразоватепь двоично-десятичных чисел в двоичные, содержащий регистр сдвига, сумма тор, первый элемент И-ИЛИ, элемент задержки, вход которого соединен с выходом переноса сумматора, выход суммы сумматора соединен со входом сдвигового регистра, выход которого соединен с первым входом первого элемента , выход которого соединен с первым входом сумматора, второй вход сумматора соединен с выходом, элемента задержки. Преобразователь содержит также регистр тетрады и элемент ИЛИ Ь . Недостатком этого преобразователя является невозможность производить преобразование с одновременным масштабированием преобразуемого числа. Кроме того, он преобразует лишь целые двоично-, десятичные числа. Цель изобретения состоит в расщирении функциональных возможностей за .5чет возможности масштабировании авончных 1исел и осуществления преобразоаания дробных чисел. Поставленная цель достигается тем, что преобразователь содержит второй и ретий элементы И-ИЛИ, трехразрядный егистр сдвига, одновибратор и четырех374разрядный регистр сдвига, выходы которотю соответственно соепниены с первым, вторым, третьим и четвертым входами второго элемент а И-ИЛН, выход сдвигового регистра совдипен с первым входом третьего эпемента И-ИШ, второй вход KOTopoiX) соединен с пятым входом второго е ламе тгг а И-ИЛИ, с прямым входом оипоБибрэтора, с входом четырехразрядного регистра сдвига,- с вторым входом иервото эпемеш-аИ-ИШ и первым вхо до тротшт-ю элемента И-ИЛ1-1, выход третьего элемеггга И-ИЛИ соедниеи с шестым вХрдом второго элемента И-ИЛИ и входом трехразрядного регистра сдвига, пер- вьйь второй и третий выходы которого соединены соответственно с седьмым и вось мш входами второго элемента И-ИЛ14, де вятым входом ВТО3.7ОГО эпемент-а , девятым входом второго элемента третьим входом первого элемента И..ИЛИ8 ич-шерсный выход одновибратора соединен с четвертым входом нервого элемента и третьим входом третьего эпемен та , четвертый сход которого соеди нен с шиной масштабного коэффициента, шины входного числа соединены соответст вйнно с одиннадцатым, двенаднатым, три надцагым и четырнадцатым входами второ го: элемента И-ИЛИ, вьпс.од которотх) соединен с третьим входом сумматора, вход . одновнбра;1.чзра соединен с управляющей ши ной. На фиг, 1 представлена функциональная схема преобразовгзггеля двоично™десятичных чисел в двоичные масштабирован™ ные| на фигр 2 - фрагмент временной диаграммы работы преобразователя. Преобразователь содержит сумматор 1, цепь переноса которого через элемент 2 задерхжи замкнута на один из его входов, сдвиговый регистр 3 иепвьй 4, второй 5 и третий 6 элементы трех и че Tbipexразрядные рэгистры 7 и 8 сдвига и оянов 1братор 9, Преобразователь работает согласно ая-горитмуt..UO-10iO+T M).10tO-it ,..1-Тз, A) , fi) где tt- - мшсснмапьное количество разря дов преобразуемотчз десятичного числа или максимальное количество тетрад двоичио-десятичного числа; Т| -„ тетрада самого старшего раз ряда десятичного числа « тетрада млапшего разряда десятичного чиспа;-масштаб, представленный в дао-. ичном коде; ,1010 -двоичное прмэдставление основания десятиадой системы счисления „ Цепь умножения на 1010 выделена на (})иг, 1 )ифной тенией. Работает устройство следующим обра ом, До подачи тетрад заедается масштаб эеобразуемого числа. Например, следует существить ввод числа 5, 8. Фактичеа-ш устройство вводится число 58, т.е. при наборе тетрад не учитьшаются их весовые арактеристики. Чтобы не получилось иокажеиия двоичного кода, следует ввести масщтаб 0,1. Масштаб М вычисляется как отнош&ние величины Амашр получе1гаой на выходе устройства (машинальная величина), к репьно введенной величине -А (д . Пусть при вводе числа 5,8 требуется сс1х1рмировать двоичный коп 0,232, тогда M ctili 1),23. д1 .;Ai.:i ..;.i::-:;™, о, 00 4. АЬВОД58 Все вводимые в устройство числа можно разбить на массивы, т.е. числа, характеризующие Одну и ту же физическую величину (например скорость, время, какие- либо коэ41фициенты и т., поэтому масштаб вычисляется не для кагкдого вводимого числа, а лишь для массива чисел, причем эти чзаранее вычисленные масштабы удобно хранить в долговремег-шой памяти. Таким образом, при наборе того или иного числа прежде следует ввести инфор мацию о массиве, к которому принадлежит вводимое число, тогда из памяти автоматически Выбирается и подается на преобразователь соответствующий масштаб,Двоичньп код выбранного масштаба М через элемент И-ИЛИ 6 периодически (1 раз в цикл) поступает младшим разрядом вперед на трехразрйдный регистр 7 сдвига, на синхровход с которого непрерывно следуют Сдвигающие тактовые импульсы (ТИ), Однако Иг х1зормация, снимаемая с выходов регистра 7, заблокирована от дальнейшего прохождения на входы сумматора отсутствием тетрады и нулевым состоянием одновибратора 9. Кроме того, и на /зыходак регистра 8 нули. С подачей первой (старшей) тетрады на вход одна вибратора 9 поступает потегщиал подача 574 тетрады (ПТ). Однако одновибраггор 9 срабатывает лишь по приходу циклическсго импульса (11И), который поступает в конце цикла. Длительность ЦИ может быт равной периоду следования ТИ. Одновибра тор выдает по заднему фронту ЦИ широки одиночный импульс, по длительности равный времени цикла. За время нахох декия одновибратора 9 в единичном состояш и происходит умножение содержиного сдвиго вого регистра 3 на 1О10, т.е. О х-1010 согласно алгоритму (1), По приходу следующего импульса, по его переднему фронту, на выходе 1 четырехразрядного регистра 8 появляется единиц а, а по окончании пропадает широкий импульс на выходе одновибратора 9 (см. фиг. 2). Единица на выходе 1 регистра В находится один цикл, за это время формируется частичное произведение Т ЛЛ Т.е. , которое тут же складывается с содержимым сумматора 1. Это происходит следующим образом. Масштаб М через эле мент И-ИЛИ 6 поступает на элемент И-ИЛИ 5, а так как четырехразрядный ре гистр 8 опрашивает в это время шнву 2 входного числа, то масштаб М проходит через элемент И-ИЛИ 5 на вход сумматора I лишь если по шине 2 нередаеч ся единица. Одновременно информация с . выхода Сдвигового регистра 3 {сейчас в регистре хранятся лишь нули) через элемент И-ИЛИ 6 поступает на второй вход суммаггора 1. Результат суммирования записывается в сдвиговый регистр 3, Перед началом нового цикла с приходом очередного импульса единица с первого выхода регистра 3 сдвига переходит на второй выход там она тоже сундествует 1 цикл, разрешая опрос шины 2 пе редаваемой тетрады. Теперь масштаб М через элемент И-ИЛИ 6-попадает на вход эпемелта И-ИЛИ 5, задерживаясь на один такт на регистре 7. Таким образом, если на шине 2 находится 1, на вход суммаггора 1 поступает величина 2М. Одновременно с выхода регистра 3 через элемент И-ИЛИ 4 на другой вход сумматора поступает величтш (ОЮЮ 4- М), Результат сложения записьшается снова в регистр 3. Возникающие при сложении переполнения, задержавшись на такт в линии 2 задержки, поступают на третий вхоц сум матора 1 Одновременно с приходом соответствующих разрядов слагаемых. Процесс проходит до тех пор, пока в регистре 3 оказьюается величина (0-1010+ T -M} 0-t010 LT M 242..2Л11- Т -Ш гт,|-8М(г) ,01 - т VL r-n. TH поступающие по сигналы, командные 2 2, 2 шинам 2, передаваемой приник акщие значения тетрады, или 1. Для этого требуется всего 5 циклов по числу слагаемых в выражении (2), До набора новой тетрады величина (0-1010 + Т М) циркулирует по цепи: сдвиговой регистр 3 - элеметст 4-сумматор1 - регистр 3. При НОВОЙ тетрады процесс происходит анапогично, т.е. в первом цикле содержиьюе регистра 3 умножается на 10 Ю, а еще через 4 ш{кла формируется величина (...(О 1010 + Тц-М) 1010 + Т.М) и т.д. Таким образом, после ввода всех тет рад в сдвиговом регистре 3 хранится двоичный код масштабированного числа. Применение предлагаемого устройства для преобразования двоичноцесятичных чисел в двоичные масшт ированные в специализированном вычислительном устройстве позволяет Вдвое сократить оборудование и потребляемую мощность блока преобразования информации по ср нению с известным устройством, работающим в комплексе со сзсемой умножения на масштабный коэффициент. формула изобретения Преобразователь двоично-десятичных чисел в двоичные, содержащий регистр Сдвига, сумматор, первый элемент И-ИЛИ, а,лемент задержки, вход которого соединен с выходом переноса сумматора, выход суммы сумматора соединен со входом сдвигового регистра, выход которого соединен с первым входом первого элемена И-ИЛИ, выход которого соединен с epBbiN) входом сумматора, второй вход сумматора соединен с выходом элемента адержки, отличающийся тем, что, с целью расширения функциональных возможностей за счет возможности маот ирования ДВОИЧ1ЫХ чисел и осущесгления преобразования пробных чисел, он одержит второй и третий элементы И-ИЛИ, рехразрядный регистр сдвига, оцновибр тор и четьфехразрядный регистр сдвггга Bbtxonb которого соответственно соеди е ны с первым, BTopbfM, третьим н четвер-тым входами второго эпемептя И-ИЛИ,, вьгхоц сдвигового регнст эа соединен с

первым входом третьего элемента И-ИЛИ, второй вход которого соединен с пятым входом второго элементаИ-ИЛИ, с при™ мМм вьосодом одновпйратора, с входом че твфехразрядного регистра сдвига, с BTopbRv первого элемента H-HJU-I н первьш третьего эпамеита , выход третьего элемента И-ИЛИ соединен с шееTiiNi входом второго эпементв И-ИЛИ н вводом трехрязряцного регистра сдвига,

ПфрВЫЙ, второй и третий выходы КОТЧЭ|Х ГО

соответственно с седьмым и восьмым входами второго элемента И-ИЛИ дфвятым входом второго элемента , десятым входом вто{х)го элемента И-ИЖ Hi третьим входом первого элемента И-ИЛИ

1тверсный выход одновибратора соединен с четвертым входом первого элемента И-ИЛИ и третьим входом третьего элемента И-ИЛИ, четвертый вход которого соед1тен с шнной масштабного коэффициента, шины входного числа соепийены сюответстаенно с одтлгадцатым, двенадцатым, тринадцатым н четырнадцатым входами второго эпемента И-ИЛИ,выход которотх) соединен с третьим вхоном сумматора, вход одновкбраггора соединен с управляющей шиной.

Источники информации, принят 1,16 во внимание при экспертизе

1,Авторское свидетельство СССР Hi 331382, кл/G 06 F 5/О2, 1970.

2,Авторское свидетельство СССР Kfc 329525, кл, G 06 F 5/02, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичных чисел в двоичные | 1962 |

|

SU717754A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Устройство для преобразования двоичныхчиСЕл B дВОичНО-дЕСяТичНыЕ | 1979 |

|

SU809153A1 |

| Преобразователь целых двоично- десятичных чисел в двоичные | 1978 |

|

SU750478A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1976 |

|

SU572781A1 |

Авторы

Даты

1980-06-25—Публикация

1978-04-10—Подача