Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано пр построении двоично-десятичных преобразователей. Известен преобразователь двоичног кода в двоично-дейятичный и обратно, с одержаддий реверсивные сдвиговые регистры, блоки коррекции, логические элементы И и ИЛИ ll . Недостаток такого преобразователя состоит в больших аппаратурных затратах и в невозможности использования динамических сдвиговых регистров, связанной с обработкой параллельных кодов. Наиболее близким по технической сущности к предлагаемому является преобразователь двоичного кода в двоично-десятичный и двоично-десятич ного в двоичный, содержащий первый ii второй сдвиговые регистры,первый,вто рой, третий и четвертый элементы И-ИЛ первый и второй 0-триггеры,0-входы которых соединены соответственно с выходами первых разрядов первого и второго сдвиговых регистров, а синхровходы О-триггеров соединены с первым входом тактовых сигналов преобразователя, чблок коррекции, информационные входы которого соединены соответственно с выходами четвер того и пятого разрядов первого сдвигового регистра, сумматор, первый и второй входы которого соединены с выходом блока коррекции и первого элемента И-ИЛИ соответственно, выход второго разряда второго сдвигового регистра соединен с первым входом второго элемента И-ИЛИ, первый и второй одноразрядные сдвиговые регистры, входы которых соединены с выходами третьего и четвертого элементов И-ИЛИ соответственно, а выходы соединены со вторыми входами первого и второго элементов И-ИЛИ соответственно, блок управления, выход разрешения приема которого соединен с третьим входом второго элемента И-ИЛИ, выход разрешения ц ркуляции соединен с третьим входом первого элемента И-ИЛЙ, выход разрешения коррекции блока управления соединен о первым управляющим входом блока коррекции, инфо{)мационный вход преобразователя соединен с четвертыми входами первого и второго элементрв . И-ИЛЙ, выходы первых разрядов первого и второго сдвиговых регистров соединены с вторыми входами третьего

И четвертого элементов И-ИЛИ,вторые входы которых соединены со вторым входом тактовых сигналов, выход первого О-триггера соединен-с пятым входом второго элемента И-ИЛИ, выход которого соединен со входом второго сдвигового регистра и третьим входом третьего элемента И-ИЛИ. Кроме того, известный преобразователь содержит элемент И-ИЛИ, подключенный ко входу первого сдвигового регистра Г2.

Недостаток известного преобразователя состоит в относительно больши аппаратурных затратах.

Цель изобретения - упрощение преобразователя.

Поставленная цель достигается тем что преобразователь двоичного кода в двоично-десятичный и двоично-десятичного в двоичный, содержащий первый и второй сдвиговые регистры, первый, второй, третий и четвертый элементы И-ИЛИ, первый и второй D-триггеры, D-входы которых соединены соответственно с выходами первых разрядов первого и второго сдвиговых регистров,а синхровходы D-триггеров соединены с первым входом тактовых сигналов преобразователя, блок коррекции, информационные входы которого соединены с выходами четвертого и пятого разрядов первого сдвигового регистра, сумматор, первы и второй входы которого соединены соответственно с выходами блока коррекции и первого элемента И-ИЛИ, выход второго разряда второго сдвигового регистра соединен с первым входом второго элемента, И-ИЛИ, первый и второй одноразрядные сдвиговь(е регистры, входы которых соединены с выходами третьего и четвертого элементов И-ИЛИ соответственно, а выходы соединены со вторыми входами первого и- второго элементов И-ИЛИ соответственно, блок управления/ выход разрешения приема которого соединен с третьим входом второго элемента И-ИЛИ, выход разрешения циркуляции соединен с третьим входом первого элемента И-ИЛИ, выход разрешения коррекции блока управления соединен .с первым управляющим входом блока коррекции, информационный вход преобразователя соединен, с четвертьпии входами первого и второго элементов И-ИЛИ, выходы первых разрядов первого и второго сдвиговых регистров соединены со вторыми входами третьего и четвертого элементов И-ИЛИ, вторые входы которых соединен со вторым входом тактовых сигналов преобразователя, выход первого Dтриггера .соединен с пятым входом второго элемента И-ИЛИ, выход которого соединен со входом второго сдвигового регистра и третьим входом третьего элемента И-ИЛИ,. дополнительно содержит пятый элемент

И-ИЛИ, выход которого является выходом преобразователя, первый и второй входы соединены с выходом разре}шения выдачи блока управления, а третий вход пятого элемента И-ИЛИ соединен с выходом первого разряда второго сдвигового регистра, выход сумматора соединен с четвертым входом пятого элемента И-ИЛИ, третьим входом четвертогоэлемента И-ИЛИ и входом первого сдвигового регистра, выход второго разряда которого соеди.нен с пятым входом первого элемента И-ИЛИ, четвертые входы третьего и четвертого элементов И-ИЛИ соединены со вторым входом тактовых сигналов преобразователя, выход второго D-триггера соединен с управляющим входом блока коррекции и шестым входом первого элемента И-ИЛИ.

При этом блок коррекции содержит блок преобразования унитарного кода в последовательный код, первый и второй D-триггеры, элемент И-ИЛИ,три элемента И, три элемента ИЛИ и.четырехразрядный сдвиговый регистр, выход первого разряда которого соединен с-первым входом элемента ИЛИ, выход которого соединен с синхров содами первого и второго D-триггеров, первым входом элемента И-ИЛИ, входом четырехразрядного сдвигового регистр и первым входом блока преобразования унитарного кода в последовательный код, выход которого является выходом блока коррекции, а второй и третий входы блока преобразования унитарного кода в последовательный код соединены соответственно с выходами второго и третьего элементов ИЛИ,, первый и второй входы второго элемента ИЛИ соединены с выходами первого и второго элементов И соответственно, первые входы которых соединены соответственно с прчМым выходом первого и инверсным выходом второго D-триггеров, прямой выход второго D-триггера соединен с первым входом третьего элемента И, выход которого подключен ко входу третьего элемента ИЛИ, вторые входы первого, второго и третьего элементов И и вторые входы второго и третьего элементов ИЛИ являются первым управляющим входом блока коррекции, D-вход первого О-триггера соединен с выходом, элемента И-ИЛИ, второй вход которого явля.ется вторым управляющим входом блока коррекции, 0-вход второго D-триггера и третий вход элемента И-ИЛИ являются информационными входами блока коррекции.

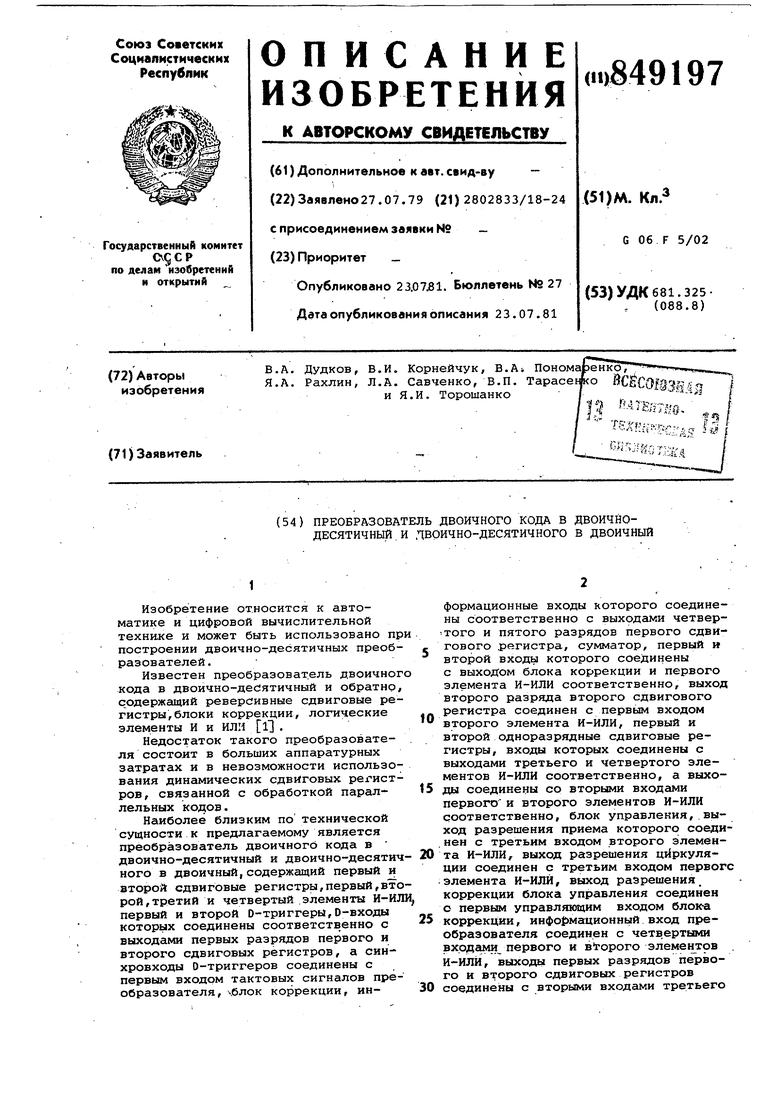

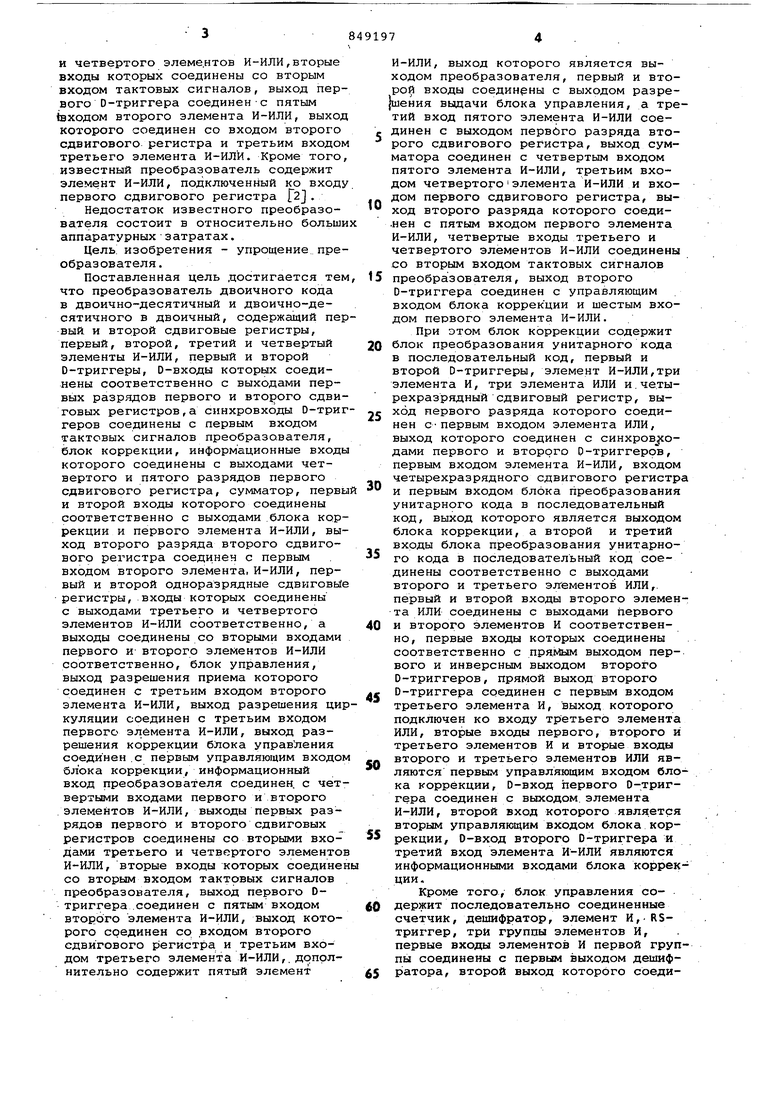

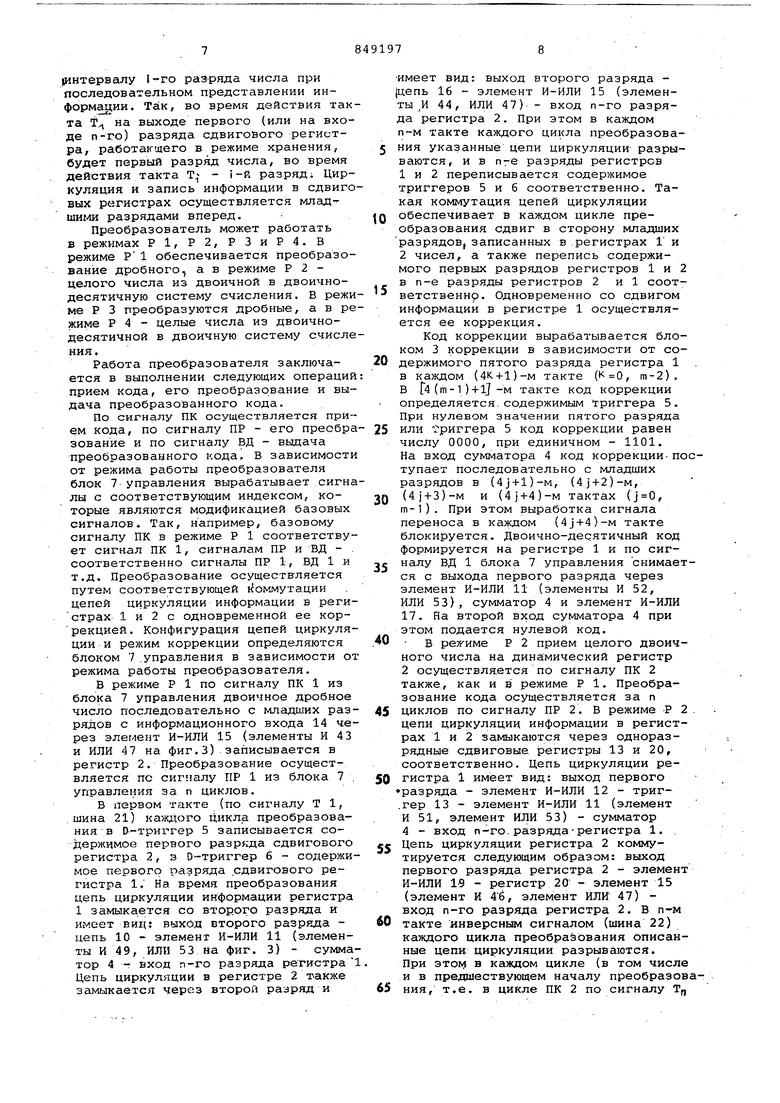

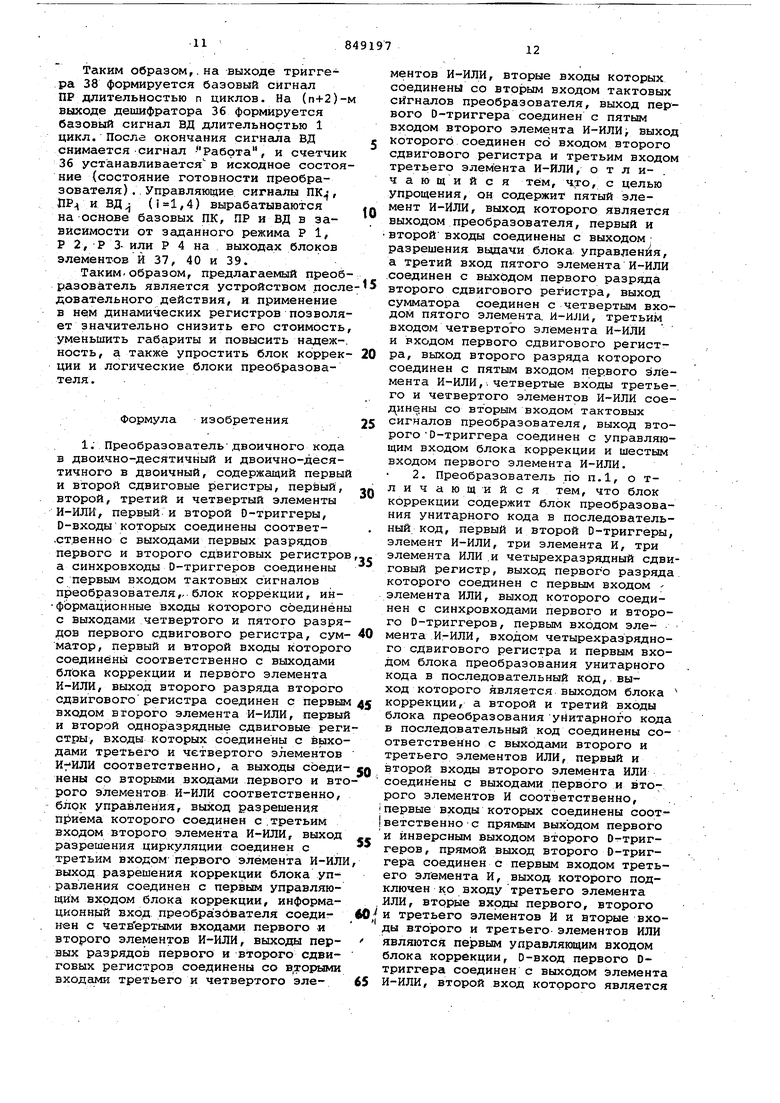

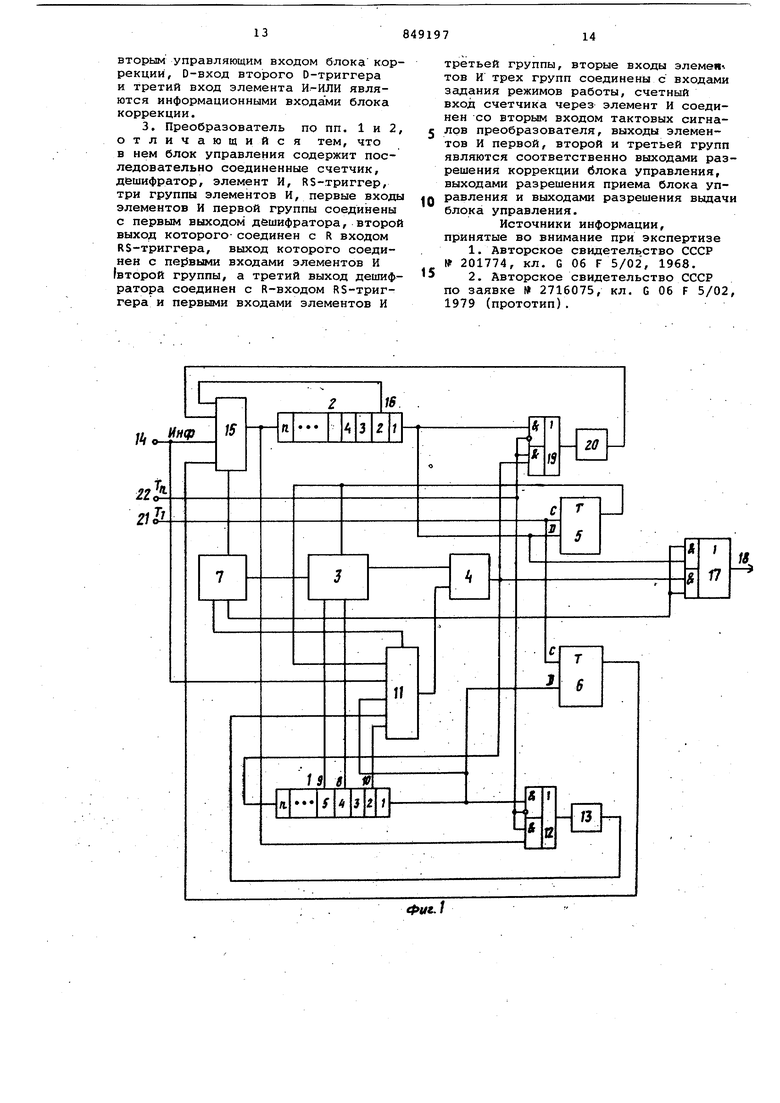

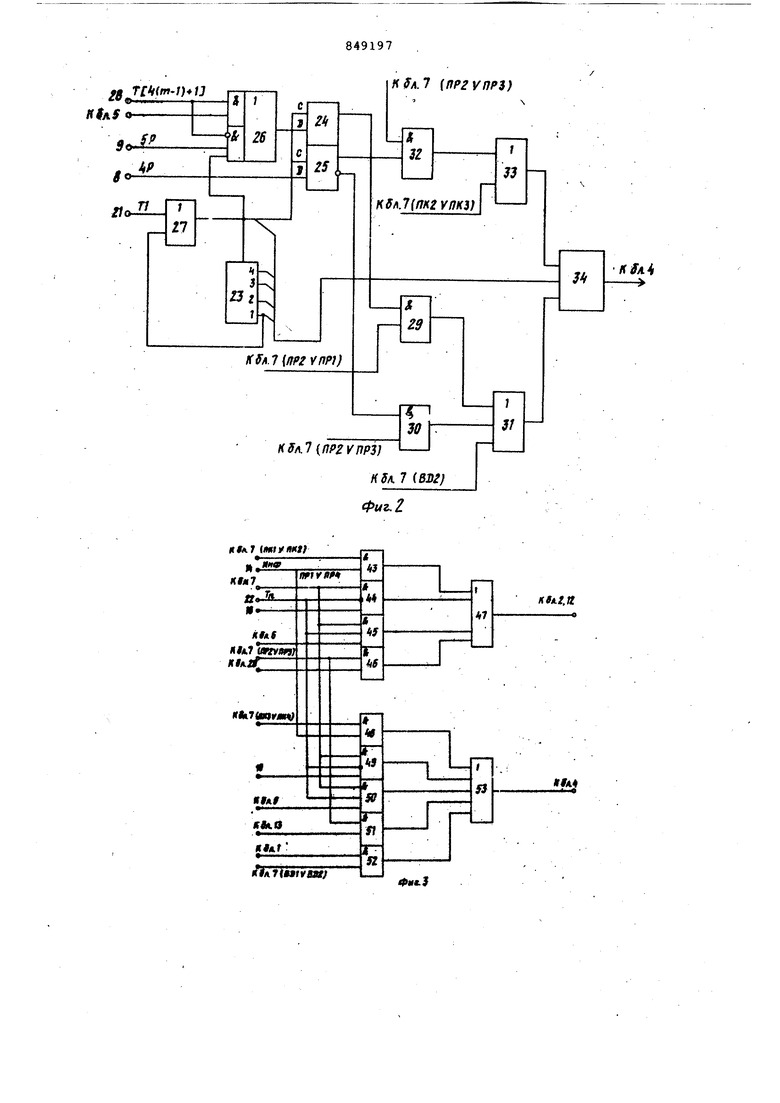

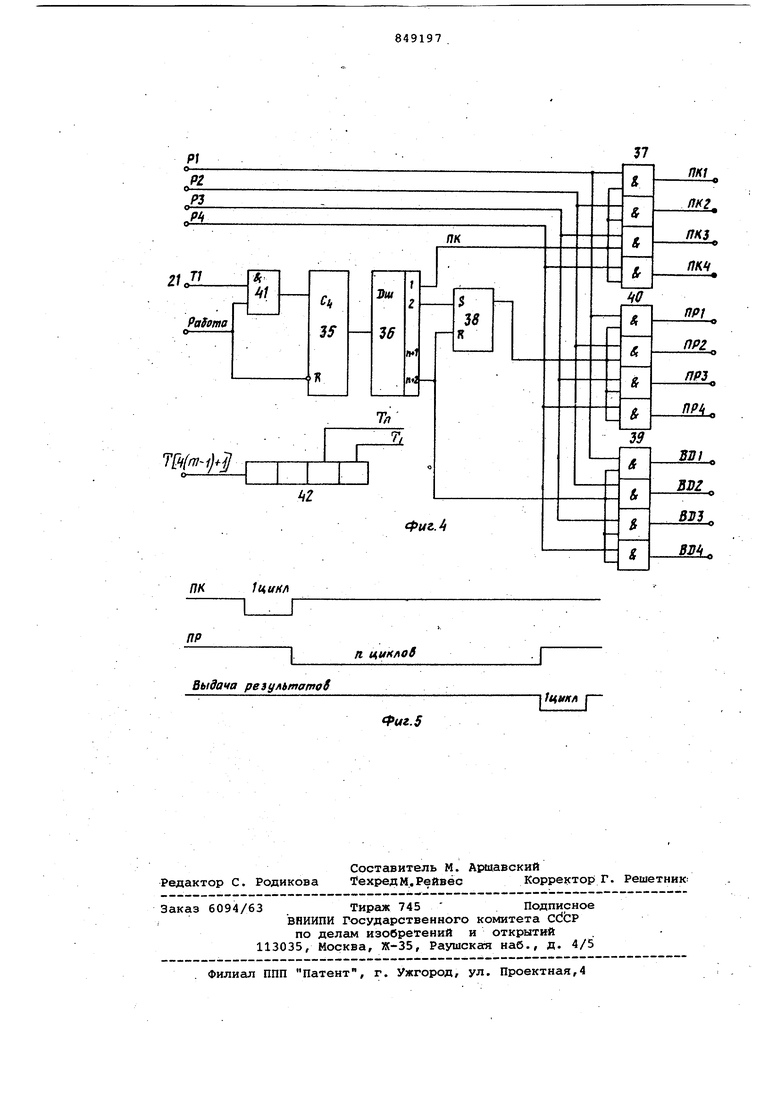

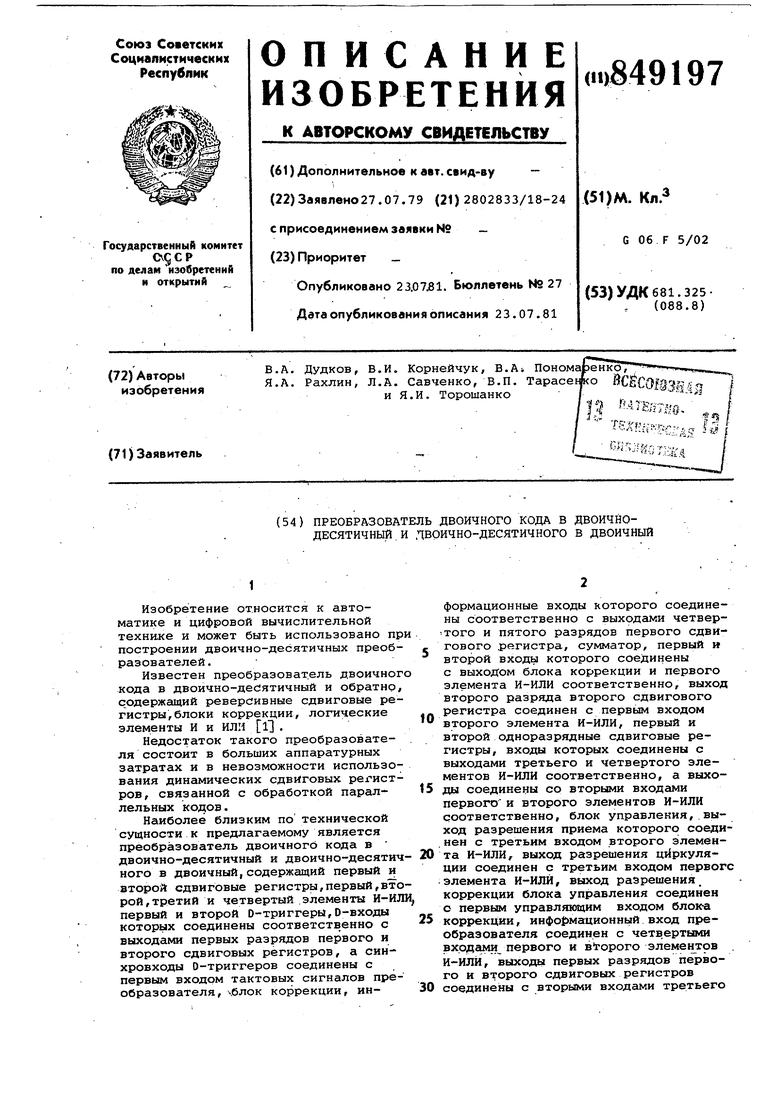

Кроме того, блок управления содержит последовательно соединенные счетчик, дешифратор, элемент И,.Л5триггер, три группы элементов И, первые входы элементов И первой группы соединены с первым выходом дешифратора, второй выход которого соединен с S-входом RS-триггера, выход которого соединен с первь 1и входами . элементов И второй группы , а третий выход дешифратора соединен с R-BXOдом RS-триггера и первыми входами элементов И третьей группы, вторые входы элементов И трех групп соединены с входами задания режимов работы, счетный вход счетчика через элемент И соединен со.вторым входом тактовых сигналов, выходы элементов И первой, второй и третьей групп. являются соответственно выходами разрешения коррекций блока управления , выходсми разрешения приема бло ка управления и выходами разрешения выдачи блока управления. На фиг. 1 изображена структурная схема предлагаемого преобразователя на фиг, 2 и 3 7 функциональные схемы соответственно блока коррекции первого и второго элементов И-ИЛИ; на фиг. 4 - функциональная схема блока управления; на фиг. 5 - временная диаграмма базовых управляющи сигналов преобразователя. Преобразователь содержит первый 1 и второй 2 сдвиговые регистры (число их двоичных разрядов , m - число десятичных разрядов преобразователя) , блок 3 коррекции (БК), сумматор 4, первый 5 и второй б D-триггеры, при этом входы блока коррекции соединены с выходами блока 7 упра.вления, триггера 5 и цепями 8 и 9 с выходами четвертого и пятого разряда регистра 1..Выход втор го разряда регистра 1 цепью 10 чере первый элемент И-ИЛИ соединен со входом сумматора 4. Выход первого разряда регистра 1 соединен со входом элемента И-ИЛИ 11, с О-входом D-триггера б и через последовательн соединенные третий элемент И-ИЛИ 12 первый одноразрядный сдвиговый регистр 13 - с входом элемента И-ИЛИ другие входы которого соединены с вы ходом D-триггера 5 и с информационной шиной 14 преобразователя и чере второй элемент И-ИЛИ 15 - со входом регистра 2. Выход второго разряда регистра 2 цепью 16. соединен со вторым входом элемента И-ИЛИ 15, а выход первого разряда - с D-входом триггера 5, через элемент И-ИЛИ 17 - с выходом пре образователя 18 и через последовател МО соединенный третий элемент И-ИЛИ 19 и второй одноразрядный сдвиговый регистр 20 - с третьим входрм элемента И-ИЛИ 15. Выход D-триггера 6 соединен с входом элемента И-ИЛИ 15 а его С-вход объединен с С-входоМ: триггера 5 и подключен к первому тактовому входу 21. Выход блока 3 коррекции подключен ко второму входу сумматора 4, выход которого подключен ко вторым входам элементов 17 и 19 и ко входу регистра 1. Вход эле мента И-ИЛИ 12 соединен со входом регистра .2, а прямые и инверсные входы элементов И-ИЛИ 12 и 19 объединены и подключены ко второму тактовому входу 22. Выходы блока 7 управления подключены к управлякнцим входам элементов 11, 15 и 17. Блок коррекции (фиг.2) содержит четырехразрядный сдвиговый регистр 23, вход которого подключен к С-входам третьего 24 и четвертого 25 D-триггеров, через элемент И-ИЛИ 26 - к О-входу D-триггера 24, через элемент ИЛИ 27 - к шине 21 и к выходу первого разряда регистра 23. D-вход триггера 25 цепью 8 подключен к регистру 1. Второй вход элемента И-ИЛИ 26 цепью 9 подключен к регистру 1. Инверсный вход первого элемента И-ИЛИ 26 и второй вход второго элемента И-ИЛИ 26 подключены к третьей . тактовой шине 28. Прямой выход третьего 24 и инверсный выход четвертого. 25 триггеров соответственно через элементы И 29 и 30 соединены со входами элемента ИЛИ 31. Прямой выход триггера 25 через элемент И 32 соединен со входом элемента ИЛИ 33. Выходы элементов ИЛИ 31 и 33 подключены ко входам кодопреобразователя 34, синхронизирующий вход которого подключен к выходам регистра 23, Вторые входы элементов 29,30, 32 и 33 и третий вход элемента 31 подключены к выходам блока 7 управления. Блок управления (фиг.4) содержит последовательно соединенные счетчик 35 и дешифратор 36,первый выход ко- торого подключен ко входам первой группы элементов И 37, второй вы- . ход - к 5-входу SR-триггера 38, третий выход - к R -входу триггера 38 и к входам элементов И 39 второй группы. Выход триггера 38 подключен ко . входам третьего блока элементов И 40 третьей группы. Счетный вход счетчика через элемент И 41 подключен к первой тактовой шине 21 и управляющему входу преобразователя, R-вход счетчика выполнен инверсным и подключен к управляющему входу преобразователя. Вторые входы блоков 37, 40 и 39 подключены к шинам задания . режимов работы. Вход регистра 42 соединен с шиной тактовых сигналов тГ4(т-Т)+1} , а два его выхода являются первой и второй шинами тактовых счетчиков Т, Тк,. Элемент И-ИЛИ 15 содержит элементы И 43-46 и элемент ИЛИ 47. Элемент И-ИЛИ 11 содержит элементы И 48-52 и элемент ИЛИ 53 (фиг.3). Работа преобразователя осуществляется по циклам. Кёйсдый цикл вы полняетея за п «актов. Длительность такта Tj равна периоду следования импульсов фазового Питания динамических регистров. Время действия такта Т соответствует временному

(интервалу 1-го разряда числа при последовательном представлении информации. Так, во время действия такта Т на выходе первого (или на входе п-то) разряда сдвигового регистра, работагщего в режиме хранения, будет первый разряд числа, во время действия такта Т - i-й разряд; Циркуляция и запись информации в сдвиговых регистрах осуществляется младшшли разрядами вперед.

Преобразователь может работать в режимах Р1, Р2, РЗиР4. В режиме Р 1 обеспечивается преобразование дробного, а в режиме Р 2 целого числа из двоичной в двоичнодесятичную систему счисления. В режиме Р 3 преобразуются дробные, а в режиме Р 4 - целые числа из двоичнодесятичной в двоичную систему счисления.

Работа преобразователя заключается в выполнении следующих операций прием кода, его преобразование и выдача преобразованного кода.

По сигналу ПК осуществляется прием кода, по сигналу ПР - его преобразование и по сигналу ВД - выдача преобразованного кода, В зависимости от режима работы преобразователя блок 1 управления вырабатывает сигналы с соответствующим индексом, которые являются модификацией базовых сигналов. Так, например, базовому сигналу ПК в режиме Р 1 соответствует сигнал ПК 1, сигналам ПР и ВД - . соответственно сигналы ПР 1, ВД 1 и т.д. Преобразование осуществляется путем соответствующей коммутации цепей циркуляции информации в рёгистрах 1 и 2 с одновременной ее коррекцией. Конфигурация цепей циркуляции и режим коррекции определяются блоком 7.управления в зависимости от режима работы преобразователя.

В режиме Р 1 по сигналу ПК 1 из блока 7 управления двоичное дробное число последовательно с младших разрядов с информационного входа 14 через элемент И-ИЛИ 15 (элементы И 43 и ИЛИ 47 на фиг.З) записывается в регистр 2. Преобразование осуществляется по сигналу ПР 1 из блока 7 . управления за п циклов.

В первом такте (по сигналу Т 1, шина 21) кащизго цикла преобразования в -триггер 5 записывается содери имое первого разряда сдвигового регистра 2, з О-триггер б - содержимое первого разряда .сдвигового регистра 1. На время преобразования цепь циркуляции информации регистра 1 замыкается со второго разряда и имеет виц: выход второго разряда цепь 10 - элемент И-ИЛИ 11 (элементы И 49, ИЛИ 53 на фиг. 3) - сумматор 4 - вход л-го разряда регистра1 Цепь циркуляции в регистре 2 также замыкается через второй разряд и

имеет вид: выход второго разряда (цепь 16 - элемент И-ИЛИ 15 (элементы ,И 44, ИЛИ 47)- - вход п-го разряда регистра 2. При этом в каждом п-м такте каждого цикла преобразования указанные цепи циркуляции- разрываются, и в п-е разряды регистров

1и 2 переписывается содержимое триггеров 5 и 6 соответственно. Такая коммутация цепей циркуляции

Q обеспечивает в каждом цикле преобразования сдвиг в сторону младших разрядов, записанных в регистрах 1 и

2чисел, а также перепись содержимого первых разрядов регистров 1 и 2 в п-е разряды регистров 2 и 1 соответственнр. Одновременно со сдвигом информации в регистре 1 осуществляется ее коррекция.

Код коррекции вырабатывается блоком 3 коррекции в зависимости от содержимого пятого разряда регистра 1 в каждом (4К+1)-м такте (, т-2) . В Г4(т-1)+1|-м такте код коррекции определяется.содержимым триггера 5. При нулевом значении пятого разряда

5 или риггера 5 код коррекции равен числу 0000, при единичном - 1101. На вход сумматора 4 код коррекции-поступает последовательно с младших разрядов в (4j+l)-M, (4j+2)-M,

0 (4j+3)-M и (4j+4)-M тактах (, m-1). При этом выработка сигнала переноса в каждом (4j+4)-M такте блокируется. Двоично-десятичный код формируется на регистре 1 и по сигC налу ВД 1 блока 7 управления снимается с выхода первого разряда через элемент И-ИЛИ 11 (элементы И 52, ИЛИ 53), сумматор 4 и элемент И-ИЛИ 17. На второй вход сумматора 4 при этом подается нулевой код.

0 в режиме Р 2 прием целого двоичного числа на динамический регистр 2 осуществля.ется по сигналу ПК 2 также, как и в режиме Р 1. Преобразование кода осуществляется за п

5 циклов по сигналу ПР 2. в режиме Р 2 . цепи циркуляции информации в регистрах 1 и 2 замыкаются через одноразрядные сдвиговые регистры 13 и 20, соответственно. Цепь циркуляции регистра 1 имеет вид: выход первого разряда - элемент И-ИЛИ 12 - триг.гер 13 - элемент И-ИЛИ 11 (элемент И 51, элемент ИЛИ 53) - сумматор 4 - вход п-го.разряда-регистра 1.

е Цепь циркуляции регистра 2 коммутируется следующим образом: выход первого разряда регистра 2 - элемент И-ИЛИ 1-9 - регистр 20 - элемент 15 (элемент И 4б, элемент ИЛИ 47) вход п-го разряда регистра 2. В

0 такте инверсным сигналом (шина 22) каждого цикла преобразования описанные цепи циркуляции разрываются. При в каждом цикле (в том числе и в предшествующем началу преобразования, т.е. в цикле ПК 2 по сигналу Т (шина 22) n-ый разряд регистра 1 с вьохода сумматора 4 через элемент 19 записывается в регистр 20, а п-ый разряд регистра 2 с выхода элемента 15 через элемент 12 - в регистр 13. Такая коммутация цепей циркуляции обеспечивает сдвиг в сторону старши разрядов записанных в регистрах 1 и 2 чисел, а также перепись содержимого п-ых разрядов регистров 1 и в первые разряды регистров 2 и 1 соответственно. Коррекция в регистре 1 осуществл ется следующим образом. Код коррекции определяется содер жимым четвертого разряда регистра 1 в каждом (4i+l)-M такте и формирует ся на выходе блока 3 коррекции. При единичном, значении четвертого разряда код коррекции равен числу 1101, при нулевом - ООН. Поступлен кода коррекции на вход сумматора 4 аналогично режиму Р 1. После преобразования двоично-десятичного числа в коде с избытком 3 формируется на регистре 1. Выдача преобразованной информации осуществляется с выхода .первого разряда регистра 1 через элемент 11 (элементы И 52, ИЛИ 53), сумматор 4 и элемент 17. Переход от кода с избытком 3 к обычному осуществляется при выдаче подачей на второй вход сумматора 4 в (4j+l)-M (4j+4)-M тактах кода 1101. При преобразовании и выдаче выработка сигнала переносаВ каждом ()-M так те блокируется. В режиме Р 3 двоично-десятичный код дробного числа перед преобразованием в двоичный код предварительно преобразуется в двоично-десятичн код с избытком 3. Это преобразовани осуществляется одновременно с приемом на сдвиговый регистр 1 следующи образом. По сигналу ПК 3 информация через элемент И-ИЛИ 11 (элементы.И 48, ИЛИ 53. на фиг.З) поступает на вход сумматора 4. На второй вход сумматора поступает п-разрядный код 00110011... ООН, который формируетс блоком 3 коррекции по сигналу ПК 3. Сформированный на выходе сумматора код с избытком 3 поступает на вход регистра 1. Врегистр 2 заносится нулевой код. Преобразование осущ,ествляется за. п циклов таким же образом, как и в режиме Р 2. Результат получается в регистре 2 и снимается с выхода первого разряда этого регистра через элемент 17 последовательным кодом по -сигналу БД 3. В режиме Р 4 прием целевого десятичного числа осуществляется по сигналу ПК 4 и через элемент И-ИЛИ 11 (элементы И 48, ИЛИ 53 на фиг.З) на регистр 1. На регистр 2 заносится нулевой код. Преобразование осуществляется за п циклов таким же образом как и в режиме Р 1. Выдача результата с регистра 2 производится так .же, как и в режиме Р 3. Блок 3 коррекции работает следующим образом. На D-триггере 24 (фиг.2) в каждом l(4j+l)-M такте по сигналам Т (4j+l) через элемент И-ИЛИ 26 запоминается содержимое пятого разряда регистра 1 или триггера 5. На D-триггере 25 запоминается содержимое четвертого разряда регистра 1. Тактирующие сигналы Т (4J+1:), подаваемые на С-входы триггеров 24 и 25, вырабатываются на выходе элемента ИЛИ 27 четырехразрядным сдвиговЕлм регистром 23. По сигналу Т .1 через элемент ИЛИ 27 в регистр 23 записывается единица, которая циркулирует в нем на протяжении всей работы преобразователя. На выходе четвертого разряда регистра 23образуются тактирующие сигналы Т (41+2), на выходе третьего разряда Т (41+3), на выходе второго разряда - 4 (41+4) и на выходе первого разряда - 4 (4i+l). Таким образом, в разных режимах работы преобразователя логические формулы X условий выработки блоком 3 формирования коррекции соответствующих кодов имеют вид .Vni43NJ(nP2Vnp3)C4 , ,CDav(:npavnP3)C4V(npivnp4)c5 , где С4. и Cj - состояния триггеров 24и 25. Условие Хоо1-1 вырабатывается на выходе элемента ИЛИ 33, условие X.,Q - на выходе элемента ИЛИ 31. Блок 34 преобразовывает унитарный код условий X 00 -t-ioi в соответствующий последовательный код ООН, 1101. Тактовые сигналы Т (4J+1), Т (4J+2), Т (4J+3), и Т (4J+4) вырабатываются на соответствующих выходах регистра 23 и поступают для синхронизации кода коррекции. Блок 7 управления может быть построен как автомат с жесткой логикой на основе счетчика и дешифратора (фиг.4). Его входными сигналами являются сигналы Т 1, сигналы Р 1 задания режима, Р 2, Р 3 и Р 4, а также сигнал Работа, (; преяепяю щий начало и конец преобразования. , . В исходном состоянии счетчик находится в нулевом состоянии. По сигналу Работа на счетный счетчика 35 через -элемент И 41 поступают тактовые сигналы Т 1, определяющие начало каждого цикла. С первого выхода (1) дешифратора 36 снимается базовый сигнал ПК. После второго сигнсша т 1 триггер 38 устанавливается в 1-е состояние.. Сброс триггера 38 осуществляется через п циклов сигналов С (п+2)-го выхода дешифратора (п+2). Таким образом,.на выходе триггера 38 формируется базовый сигнал ПР длительностью п циклов. На (п+2)-м выходе дешифратора 36 формируется базовый сигнал ВД длительностью 1 цикл. Посла окончания сигнала ВД снимается сигнал - Работа, и счетчик 36 устанавливается в исходное состояние {состояние готовности преобразователя) .. Управляющие сигналы ПК, tlP и ВД (,4) вырабатываются на основе базовых ПК, ПР и ВД в зависимости от заданного режима Р 1, Р 2, Р 3- или Р 4 на выходах блоков элементов И 37, 40 и 39. Таким.образом, предлагаемый преобразователь является устройством после довательного действия, и применение в не.м Динамических регистров позволяет значительно снизить его стоимость уменьшить габариты и повысить надеж-, ность, а также упростить блок коррекции и логические блоки преобразователя. Формула изобретения 1: Преобразователь-двоичного кода в двоично-десятичный и двоично-десятичного в двоичный, содержащий первы и второй сдвиговые р.егистры, первый, второй, третий и четвертый элементы И-ИЛИ, первый и второй О-триггеры, D-входы которых соединены соответ.ст.венно с выходами первых разрядов первого и второго сдвиговых регистро а синхровходы D-триггеров соединены с первым входом тактовых сигналов преобразователя,- блок коррекции, инфЬрмацйонные входы которого соединены с выходами четвертого и пятого разря дов первого сдвигового регистра, сум матор, первый и второй входы которог соединены соответственно с выходами блока коррекции и первого элемента И-ИЛИ, выход второго разряда второго сдвиговогорегистра соединен с первы входом второго элемента И-ИЛИ, первы и второй одноразрядные сдвиговые рег стры, входы которых соединены с выхо дами третьего и четвертого элементов ИтИЛИ соответственно, а выходы соеди нены со вторыми входами первого и вт рого элементов И-ИЛИ соответственно, блок управления, выход разрешения приёма которого соединен с .третьим входом второго элемента И-ИЛИ, выход разрешения циркуляции соединен с третьим ВХОДОМпервого элемента И-ИЛ выход разрешения коррекции блока управления соединен с первым управляющим входом блока коррекции, информационный вход преобразбвателя соединен с четвертыми входами первого и второго элементов И-ИЛИ, выходы первых разрядов первого и второго сдвиговых регистров соединены со в,торыми входами третьего и четвертого элементов И-ИЛИ, вторые входы которых соединены со вторым входом тактовых сигналов преобразователя, выход первого D-триггера соединен с пятым входом второго элемента И-ИЛИ выход которого соединен со входом второго сдвигового регистра и третьим входом третьего элемента И-ИЛИ, о т л и- . чающийся тем, что, с целью упрощения, он содержит пятый элемент И-ИЛИ, выход которого является выходом преобразователя, первый и второй входы соединены с выходом : разрешения вьщачи блока управления, а третий вход пятого элемента И-ИЛИ .соединен с выходом первого разряда второго сдвигового регистра, выход сумматора соединен с четвертым входом пятого элемента, и-или, третьим входом четвертого элемента И-ИЛИ и входом первого сдвигового регистра, выход второго разряда которого соединен с пятым входом первого элемента И-ИЛИ,.четвертые входы третье-, го и четвертого элементов И-ИЛИ соедине.ны со вторым входом тактовых сигналов преобразователя, выхо( второгоО-триггера соединен с управляющим входом блока коррекции и шестым входом первого элемента И-ИЛИ. 2. Преобразователь по п.1, отличающийся тем, что блок коррекции содержит блок преобразования унитарного кода в последовательный код, первый и второй D-триггеры, элемент И-ИЛИ, три элемента И, три элемента ИЛИ .и четырехразрядный сдвиговый регистр, выход первого разряда которого соединен с первым входом элемента ИЛИ, выход которого соединен с синхровходами первого и второго D-триггеров, первым входом элемента И-ИЛИ, входом четырехразрядного сдвигового регистра и первым входом блока преобразования унитарного кода в последовательный код,, выход которого является выходом блока коррекции, а второй и третий входы блока преобразования унитарного кода в последовательный код соединены соответственно с выходс1ми второго и третьего элементов ИЛИ, первый и второй входы второго элемента ИЛИ соединены с выходами первого и второго элементов И соответственно, первые входы которых соединены соответственно-с прямым выходом первого и инверсным выходом второго От-триггеров, прямой выход второго О-триггера соединен с первым входом третьего элемента И, выход которого подключен к.о входу третьего элемента .ИЛИ, вторые входы первого, второго и третьего элементов И и вторые входы второго и третьего элементов ИЛИ являются первым управляющим входом блока коррекции, 0-вход первого Dтриггера соединен с выходом элемента И-ИЛИ, второй вход которого является

вторым управляющим входом блока коррекции, D-вход второго D-триггера и третий вход элемента И-ИЛИ являются информационными входами блока коррекции.

3. Преобразователь по пп. 1 и 2, отличающийся тем, что в нем блок управления содержит последовательно соединенные счетчик. Дешифратор, элемент И, RS-триггер, три группы элементов И, первые входы элементов И первой группы соединены с первым выходом дешифратора, второй выход которого-соединен с R входом RS-триггера, выход которого соединен с первыми входами элементов И (второй группы, а третий выход дешифратора соединен с R-входом RS-триггера и первыми входами элементов И

третьей группы, вторые входы элемеитов И трех групп соединены с входами задания режимов работы, счетный вход счетчика через элемент И соединен со вторым входом тактовых сигналов преобразователя, выходы элементов И первой, второй и третьей групп являются соответственно выходами разрешения коррекции блока управления, выходами разрешения приема блока управления и выходами разрешения выдачи

0 блока управления.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 201774, кл. G Об F 5/02, 1968.

5

2.Авторское свидетельство СССР по заявке 2716075, кл. G Об F 5/02, 1979 (прототип).

Р/

J7

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСя-ТичНОгО B дВОичНый | 1979 |

|

SU809155A1 |

| Преобразователь двоичного кода в двоично-десятичный и двоично-десятичного в двоичный | 1979 |

|

SU860051A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоичного кодаВ дВОичНО-дЕСяТичНый | 1978 |

|

SU809150A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

lnuHfl

ПК

ПР

Выдача результатов

п. циклов

114ИКЛ I

fpuz.S

Авторы

Даты

1981-07-23—Публикация

1979-07-27—Подача