(54) УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Устройство для управления памятью | 1985 |

|

SU1280626A1 |

| Устройство для сопряжения двух микроЭВМ с общим внешним устройством | 1985 |

|

SU1345206A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1735907A1 |

1

Изобретение относится к запоминающим устройствам, а именно к управляющим устройствам памяти и может быть использовано в системах обработки данных.

Известно устройство программного управления, содержащее блок памяти, блок ввода данных, блок записи и считывания программы, в КОТОРОМ программа записывается в память в шаговой последовательности, а затем считывается по мере необходимости Ij

Недостатком такого устройства является отсутствие возможности записи данных в память при работе устройства в режиме непрерывного считывания путем прерывания считываемой программы.

Наиболее близким по техническому решению к предлагаемому изобретению является устройство управления памятью, которое обеспечивает непрерывное последовательное считывание информационных слов из памяти, -а также селективный ввод информационного слова в ячейку памяти по заданному адресу. Устройство содержит блок ввода данных, блок памяти с произвольной выборкой, распределитель управляющих сигналов, генератор последовательно сканирующего бинарного сигнала, блок адреса, блок для сравнения адреса 2.

Недостатком известного устройства управления памятью является то, что устройство в режиме непрерывного считывания информационных слов из памяти не позволяет осуществлять запись информации в память по заданному адресу путем прерывания режима непрерывного считывания и перехода в режим записи с последующим возвратом в режим считывания, а также низкое быстродействием в режиме записи очередного информационного слова в память.

Цель изобретения - расширение функциональных возможностей устройства управления памятью за счет осуществления прерывания процесса считывания в любой мо5 мент времени и повышение его быстродействия.

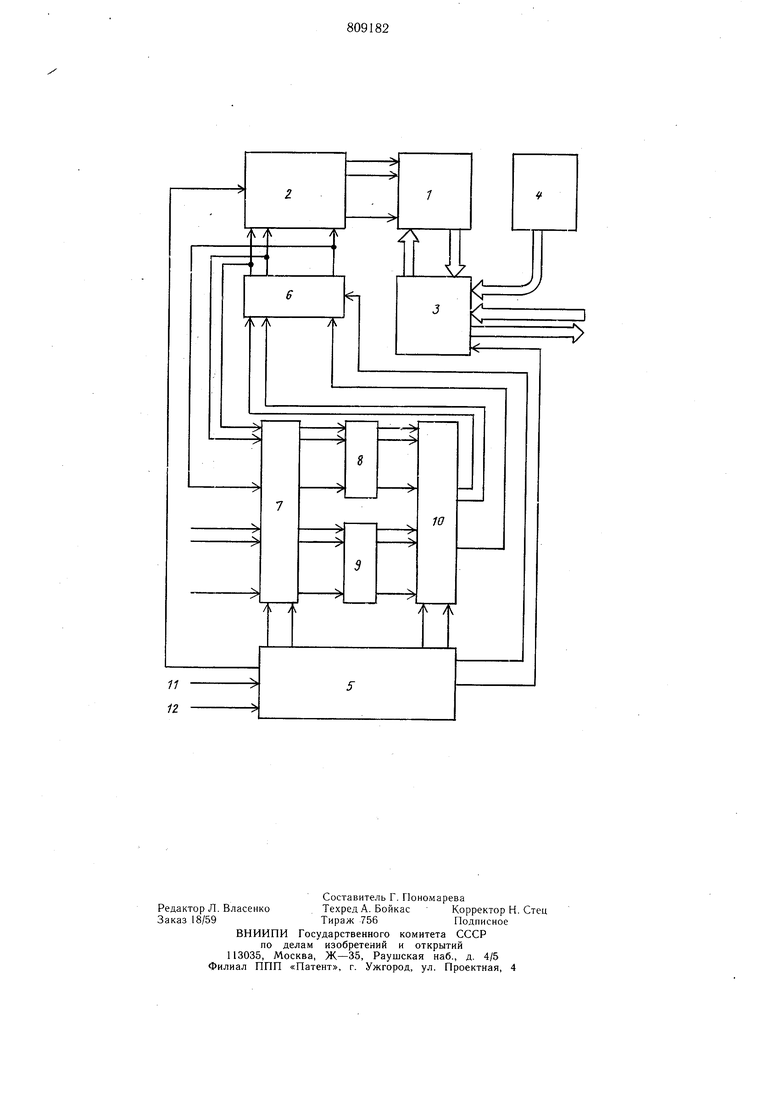

Поставленная цель достигается тем, что в устройство, содержащее блок записи и считывания, первый, второй и третий входы которого соединены соответственно с информа-

ционными выходами блока памяти, блока ввода данных и информационными входами устройства, первые и вторые информационные выходы блока записи и считывания соединены соответственно с информационным входом блока памяти и с информационным выходом устройства, группа выходов блока адреса соединена с группой адресных входов блока памяти, первый и второй выходы распределителя управляющих сигналов соединены соответственно с управляющим входом блока адреса и четвертым входом блока записи и считывания, введены счетчик адреса, блок записи адреса, блок счт№ывания адреса, регистр адреса программы, регистр адреса, группа разрядных выходов счетчика адреса соединена с группой адресных входов блока адреса и с первой группой входов блока записи адреса, вторая группа входов которого является группой адресных входов устройства, первая группа выходов блока записи адреса соединена с группой информационных входов регистра адреса программы, группа выходов которого соединена с первой группой входов блока считывания адреса, вторая группа входов которого соединена с группой выходов регистра адреса, группа информационных входов которого соединена со второй группой выходов блока записи адреса; группа выходов блока считывания адреса соединена с группой информационных входов счетчика адреса, счетный вход которого соединен с третьим выходом распределителя управляющих сигналов, четвертый и пятый выходы которого соединены соответственно с первым и вторым входами блока записи адреса, первый и второй входы блока считывания адреса соединены соответственно с щестым и седьмым выходами распределителя управляющих, сигналов, первый и второй входы которого являются соответственно входами прерывания программы и продолжения программы устройства. Такое устройство позволяет осуществлять запись информации в память по заданному адресу при работе устройства в режиме считывания информации путем прерывания последнего, и перехода в режим записи с последующим возвратом в режим считывания. Устройство позволяет также уменьщить время записи информационного слова в память по заданному адресу, путем исключения времени, необходимого для сравнения сканирующего бинарного сигнала с кодом заданного адреса. На чертеже представлена блок-схема устройства. Устройство содержит блок 1 памяти, блок 2 адреса, блок 3 записи и считывания, блок 4 ввода данных, распределитель 5 управляющих сигналов,счетчик 6 адреса, блок 7 записи адреса, регистр 8 адреса программы, регистр 9 адреса, блок 10 считывания адреса, вход 11 прерывания программы, вход 12 продолжения программы. На адресные входы блока 1 памяти подается код адреса из блока 2 адреса. На информационные входы блока 1 памяти через блок 3 записи и считывания подаются информационные слова, подлежащие записи в память. Ввод информационных слов в блок 1 памяти может осуществлять из блока 4 ввода данных или от внещнего источника информации. Распределитель 5 управляет блоком 3 записи и считывания, устанавливая его либо в режим записи, либо в режим считывания, а также блоком 2 адреса, осуществляя подачу кода адреса, поступающего из счетчика 6 адреса, на адресные входы блока 1 памяти. На входы блока 7 записи адреса, служащего для записи кода адреса в регистр 8 адреса программы и в регистр 9 адреса, поступают коды двух адресов - со счетчика 6 адреса и непосредственно со входов устройства. Коды адресов со счетчика 6 адреса и со входов устройства с помощью управляющих импульсов, поступающих из распределителя 5, могут быть записаны соответственно в регистр 8 адреса программы и в регистр 9 адреса. Управляющие импульсы, поступающие импульсы, поступающие из распределителя 5, осуществляют управление блоком 10 считывания адреса. С помощью этих импульсов в счетчик 6 адреса производится запись содержимого регистра 8 адреса программы, либо регистра 9 адреса. Вход 11 прерывания программы и вход 12 продолжения программы служат для установки распределителя 5 в режим прерывания или в режим продолжения соответственно. Сигнал прерывания по входу 11 прерывания поступает в распределитель 5,прерывает цикл считывания информации из памяти и устанавливает блок 3 записи и считывания в режим записи. Затем распределитель 5 последовательно во времени выдает два импульса, первый из которых подается на блок 7 записи адреса и переписывает содержимое счетчика 6 адреса в регистр 8 адреса программы, а второй подается в блок 10 считывания адреса и переписывает содержимое регистра 9 адреса в счетчик 6 адреса. В результате в регистре адреса 8 программы запоминается адрес, на котором произошло прерывание программы, а в счетчике 6 адреса устанавливается адрес, по которому следует осуществить запись информации в память. По окончании записи информации в память в распределитель 5 по входу 12 продолжения программы подается сигнал, по которому блок 3 записи и считывания устанавливается в режим считъшания и формируются два следующих друг за другом импульса, первый из которых поступает в блок 7 записи адреса и переписывает; содержимое счетчика 6 адреса в регистр 9 адреса, а второй поступает в блок 10 считывания адреса и записывает содержимое регистра 8 адреса программы в счетчик 6 адреса. В результате обеспечивается запоминание в регистре 9 адреса кода адреса, на котором закончена запись информации в память, и установка в счетчике 6 адреса кода адреса, содержащегося в регистре 8 адреса программы, на котором ранее было осуществлено прерывание программы. При поступлении очередного импульса прерывания программы описанный процесс повторяется и запись информации осуществляется по адресу, хранящемуся в регистре 9 адреса.

Таким образом, предлагаемое устройство позволяет в режиме непрерывного считывания информации в любой момент времени осуществлять прерывание процесса считывания с целью записи информации по адресу, храняющемуся в регистре 9 адреса. Причем такое прерывание можно осуществлять многократно, каждый раз начиная запись с ячейки памяти, адрес которой после предыдущего прерывания запоминается в регистре 9 адреса и на очередном прерывании записывается в счетчик 6 адреса.

Повыщение быстродействия устройства в режиме записи информационных слов в блок памяти достигается тем, что требуемый адрес ячейки памяти через блок 7 записи адреса, вводится заранее со входов устройства в регистр 9 адреса. Затем содержимое регистра 9 адреса через блок 10 считывания адреса переписывается в счетчик 6 адреса, устанавливая последний в состояние, соответствующее коду заданного адреса. Такая организация установки адреса позволяет сократить время записи информационных слов в память за счет исключения времени, необходимого для сравнения заданного адреса с бинарным сканирующим сигналом, последовательно принимающим значения, соответствующие адресам блока 1 памяти.

Введение новых блоков позволило в режиме непрерывного считывания программы записывать данные в память. Такой режим работы удобен в системах обработки данных, когда информация обрабатывается по блокам и результат каждой обработки необходимо запомнить в памяти. При этом за счет исключения времени, необходимого для сравнения заданного адреса с бинарным сканирующим сигналом, уменьщается время записи информации в память. В результате расщиряются функциональные возможности устройства и повыщается его быстродействие.

Формула изобретения

Устройство управления памятью, содержащее блок записи и считывания, первый, второй и третий входы которого соединены

соответственно с информационными выходами блока памяти, блока ввода данных и информационными входами устройства, первые и вторые информационные выходы блока записи и считывания соединены соответственно с информационным входо.м блока памяти и с информационным выходом устройства, группа выходов блока адреса соединена с группой адресных входов блока памяти, первый и второй выходы распределителя управляющих сигналов соединены соответственно с управляющим входом блока адреса и четвертым входом блока записи и считывания, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет осуществления прерывания процесса считывания в любой момент времени и повышения его быстродействия, в устройство введены счетчик адреса, блок записи адреса, блок считывания адреса, регистр адреса программы, регистр адреса, причем группа разрядных выходов счетчика адреса соединена с группой адресных входов блока адреса и с первой группой входов блока записи адреса, вторая группа входов которого является группой адресных входов устройства, первая группа выходов блока записи адреса соединена с группой информационных входов регистра адреса программы, группа выходов которого соединена с первой группой входов блока считывания адреса, вторая группа входов которого соединена с группой выходов регистра адреса, группа информационных входов которого

0 соединена со второй группой выходов бло ка записи адреса, группа выходов блока считывания адреса соединена с группой информационных входов счетчика адреса, счетный вход которого соединен с третьим выходом распределителя управляющих сигналов, четвертый и пятый выходы которого соединены соответственно с первым и вторым входами записи блока записи адреса, первый и второй входы считывания блока считывания адреса соединены соответственно с

Q шестым и седьмым выходами распределителя управляющих сигналов, первый и второй входы которого являются соответственно входами прерывания программы и продолжения программы устройства. Источники информации,

5принятые во внимание при экспертизе

/V /

/ /

11 12

Авторы

Даты

1981-02-28—Публикация

1979-06-18—Подача