(54) ИНТЕРПОЛЯТОР

жит группу экспоненциальных усреднителей, формирователь сигнала переполнения, оперативное запоминающее устройство, формирователь адреса и инвертор, подключенный входом к информационному входу ин.терполятора, а выходом - к первому информационному входу оперативного запоминающего устройства, соединенного вторым информационным входом с многоразрядным выходом регистра, адресным входом - с выходом формирователя адреса, а выходом - со вторым входом формирователя разности, подк; юченного выходом через формирователь сигнала переполнения к информационному входу регистра, вход обнуления которого соединен с щиной синхронизации, а многоразрядный выход регистра подключен к многоразрядному входу первого экспоненциального усреднителя со сдвигом в сторону его младщих разрядов, причем многоразрядный выход каждого i-ro экспоненциального усреднителя (1 i ш, где ш - количество усреднителей) соединен с многоразрядным входом (i + 1)-го экспоненциального усреднителя со сдвигом в сторону его младщих разрядов, а многоразрядный выход т-го экспоненциального усреднителя подключен к выходу интерполятора.

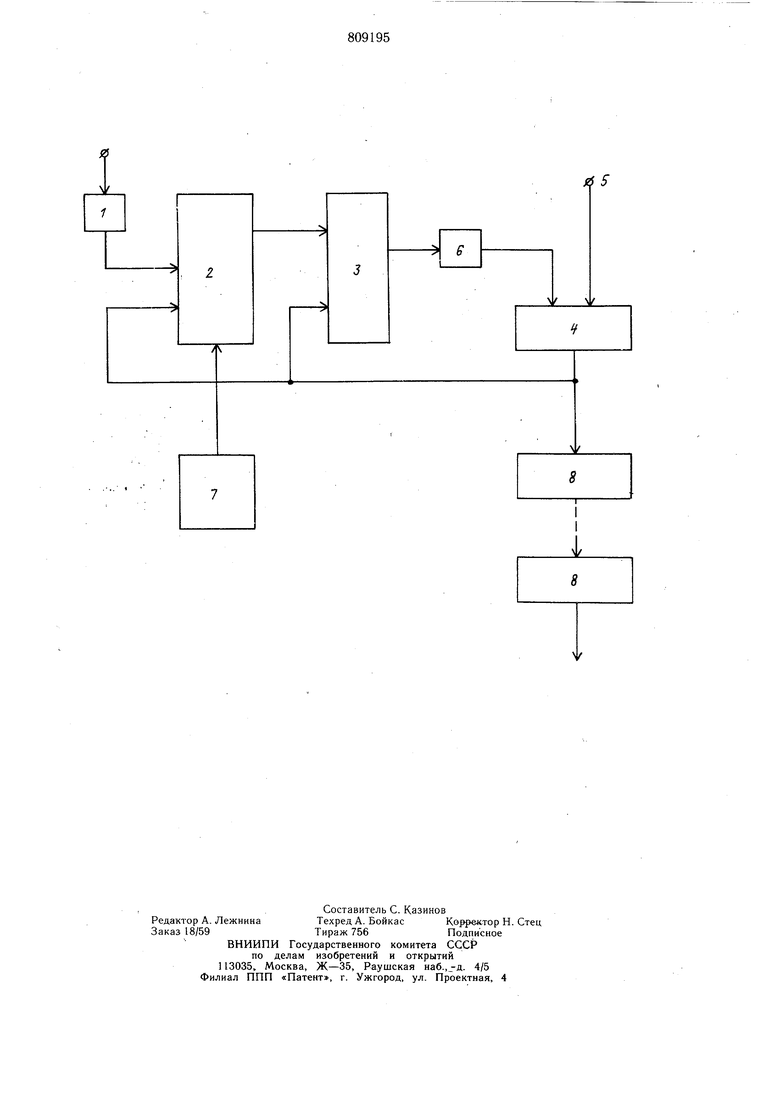

На чертеже изображена блок-схема интерполятора.

Интерполятор содержит инвертор 1, подключенный входом к информационному входу интерполятора, а выходом - к первому информационному входу оперативного запоминающего устройства 2, подключенного вторым информационным входом к первому входу формирователя 3 разности и к многоразрядному выходу регистра 4. Регистр 4 соединен входом обнуления с шиной 5 синхронизации, а информационным входом - с выходом формирователя 6 сигнала переполнения. Вход формирователя б подключен к выходу формирователя 3 разности, второй вход которого соединен с выходом оперативного запоминающего устройства 2, подключенного адресным входом к выходу формирователя 7 адреса. Многоразрядный выход регистра 4 соединен с многоразрядным входом первого экспоненциального усреднителя 8 со сдвигом в сторону его младщих разрядов. Многоразрядный выход каждого i-ro экспоненциального усреднителя 8 (1 i т, где m - количество усреднителей 8) соединен с многоразрядным входом (i -f + 1)-го экспоненциального усреднителя 8 со сдвигом в сторону его младщих разрядов. Многоразрядный выход т-го усреднителя 8 подключен к выходу интерполятора.

Интерполятор работает следующим образом.

Опорные значения входного сигнала в цифровом виде, пройдя инвертор 1, поступают в оперативное запоминающее устройство 2 через равные промежутки времени.

соответствующие периоду квантования входного сигнала, а в эти же моменты времени регистр 4 обнуляется сигналом по щине 5 синхронизации. Инверсное значение входного сигнала поступает в ячейку оперативного з апоминающего устройства 2, номер которой определяет формирователь 7 адреса. Считанное с выхода оперативного запоминающего устройства 2 это инверсное значение поступает на второй вход формирователя 3 разности, на первый вход которого подан нулевой сигнал из регистра 4. В формирователе 3 разности из сигнала, поступающего на первый вход, вычитается сигнал, поступающий на второй вход. Результат вычитания - прямое значение входного сигнала с выхода формирователя 3 разности через регистр 4 записывается в ту же ячейку оперативного запоминающего устройства 2 вместо инверсного значения входного сигнала для использования в следующем периоде квантования. После смены адреса па вь1ходе формирователя 7 адреса из запоминающего устройства 2 считывается предыдущее опорное значение входного сигнала, которое поступает на второй вход формирователя 3 разности, на первый вход которого с регистра 4 подано настоящее значение входного сигнала. В формирователе 3 разности формируется разность первого порядка, которая через регистр 4 записывается в ячейку оперативного запоминающего устройства 2 вместо предыдущего входного сигнала для использования ее в следующем периоде квантования. Со следующей сменой адреса из оперативного запоминающего устройства 2 считывается предыдущая разность первого порядка и поступает на второй вход формирователя 3 разности, на первый, вход которого с регистра 4 подана разность первого порядка за текущий период квантования. В формирователе 3 разности формируется разность второго порядка, которая через регистр 4 записывается в ячейку оперативного запоминающего устройства 2 вместо предыдущей разности первого порядка для использования ее в следующем периоде квантования. Эти операции повторяются многократно до получения на выходе формирователя 3 разности разности (п-1)-го 5 порядка. При этом формирователь 6 сигнала переполнения, включенный между выходом формирователя 3 разности и информационным входом регистра 4, позволяет использовать формирователь 3 разности с малой длиной разрядной сетки.

Разность (6-1)-го порядка с выхода регистра 4 поступает на эход первого из группы последовательно соединенных экспоненциальных усреднителей 8. В каждом экспоненциальном усреднителе 8 производится интегрирование разности и вырабатывается разность более низкого порядка, которая за счет экспоненциал ьного старения

начальных условий с высокой точностью повторяет соответствующую разность входного сигнала. С выхода последнего экспоненциального усреднителя 8 сигнал поступает на выход интерполятора. При выборе количества экспоненциальных усреднителей и максимального значения порядка разности следует установить, что увеличение порядка вычисляемых разностей приводит к более сильному подавлению изкочастотных составляющих входного сигнала, а увеличение количества экспоненциальных усреднителей - к более сильному подавлению высокочастотных составляющих сигнала. Указанное обстоятельство позволяет обеспечить заданные требования к частотной характеристике интерполятора для каждого конкретного случая. Использование поразрядного сдвига при соединении между собой регистра 4 и экспоненциальных усреднителей 8 позволяет обеспечить заданный коэффициент передачи интерполятора без использования соглясующего делителя. При этом величина сдвига зависит от типа используемых усреднителей 8 и потребного вида частотной характеристики спектра интерполируемого сигнала. При наиболее простом характере реализации усреднителей 8 (у которых коэффициент передачи для постоянной составляющей равен 2 , где Р - целое число} число разрядов P|, на которое необходимо выполнять сдвиг в соединениях между собой регистра и усреднителей, определяется спектром инте)полируемого сигнала и постоянной времени усреднителя, определяющей его частотную характеристику, где справедливо соотношение - 2.

Таким образом, предлагаемый интерполятор за счет использования экспоненциальных усреднителей и упрощения вычисления разности (п- )-го порядка позволяет упростить реализацию интерполятора, что в свою очередь обеспечивает более высокую надежность его работы.

Формула изобретения Интерполятор, содержащий формирователь разности, подключенный первым входом к многоразрядному выходу регистра, отличающийся тем, что, с целью упрощения

5 интерполятора при сохранении быстродействия и высокой точности передачи спектра входного сигнала, он содержит группу экспоненциальных усреднителей, формирователь сигнала переполнения, оперативное запоминающее устройство, формирователь

° адреса и инвертор, подключенный входом к информационному входу интерполятора, а выходом - к первомуинформационному входу оперативного запоминающего устройства, соединенного вторым информационным

5 входом с многоразрядным выходом регистра, адресным входом - с выходом формирователя адреса, а выходом - со вторым входом формирователя разности, подключенного выходом через формирователь сигнала переполнения к информационному входу регистра, вход обнуления которого соединен с щиной синхронизации, а многоразрядный выход регистра подключен к многоразядному входу первого экспоненциального усреднителя со сдвигом в сторону его младших раз-, рядов, причем многоразрядный выход каждого i-ro экспоненциального усреднителя (1 i т, где ш - количество усреднителей) соединен с многоразрядным входом (i + t)-ro экспоненциального усреднителя со сдвигом в сторону его младших разрядов,

0 а многоразрядный выход т-го экспоненциального усреднителя подключен к выходу интерполятора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 5 № 506873, кл. G 06 G 7/30, 1974.

2.Патент США № 4052605, Кл. 364-724, опублик. 1977.

3.Авторское свидетельство СССР по заявке № 2439337/18-24, кл. G 06 G 7/30, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1977 |

|

SU684562A1 |

| Линейный интерполятор | 1989 |

|

SU1659986A1 |

| Цифровой знаковый коррелометр | 1980 |

|

SU962975A1 |

| Устройство программного управления | 1984 |

|

SU1246055A1 |

| Многоканальное устройство для форми-РОВАНия ВРЕМЕННыХ иНТЕРВАлОВ | 1979 |

|

SU815875A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Процессор для оперативного корреляционно-спектрального анализа | 1973 |

|

SU477420A1 |

| Устройство для цифровой корреляционнойфильТРАции | 1978 |

|

SU799108A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

Авторы

Даты

1981-02-28—Публикация

1978-10-02—Подача