1

Изобретение относится к вычислительной технике.

Известно устройство, в котором в память записываются коды и по опросу последовательно считываются и сравниваются шаг за шагом с исходным кодом, считывание и сравнение продолжается до тех пор, пока не обнаружится требуемый код, в случае его отсутствия блбк памяти проверяется полностью Cll

Недостатками этого устройства являются низкое быстродействие и сложность устройства.

Наиболее близким по технической сущности к предлагаемому является поисковое запоминающее устройство, содержащее память поиска, в которой накапливается множество слов-указателей блоков памяти, каждое из которых содержит общую часть и инфомационную часть, регистр поиска, в котором хранится слово поиска, таже содержащее общую и информационную части и сравниваемое со словами-указателями блоков, хранящимися в памяти поиска; дешифратор для преобразования двоичной информационной части слова поиска в единичный позиционный код, устройство для

группирования множества слов данных в соответствии с их общими чactями, преобразователь для генерации слова-указателя блока каждой группы слов данны:с и средства загрузки, которые управляют работой памяти поиска и регистра поиска {.2} .

Недостатком этого устройства является его сложность, так как

0 требуется большой объем пгиляти и аппаратуры для запоминания и поиска информации.

Цель изобретения - упроцение устройства.

5

Поставленная цель достигается, тем, что в устройство для поиска информации в памяти, содержащее регистр признака поиска, дешифратор,на-, копитель и блок управления, одни из

0 выходов которого соединены соответственно со входом регистра признака П иска и первым входом дешифратора, второй вход ко-орого подключен к первому выходу регистра признака по5иска, введены регистр числа, схем сравнения и формирователь сигналов адреса, первый вход и выход которого соединены, соответственно, со вторым выходом регистра признака поиска и

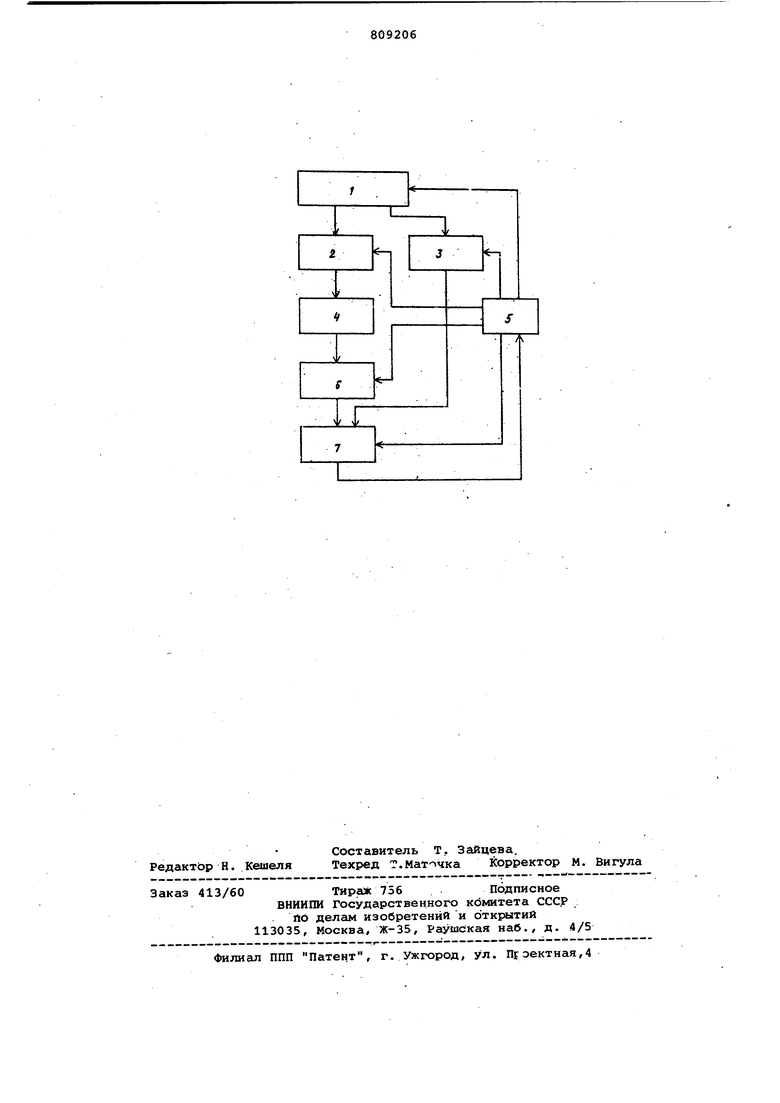

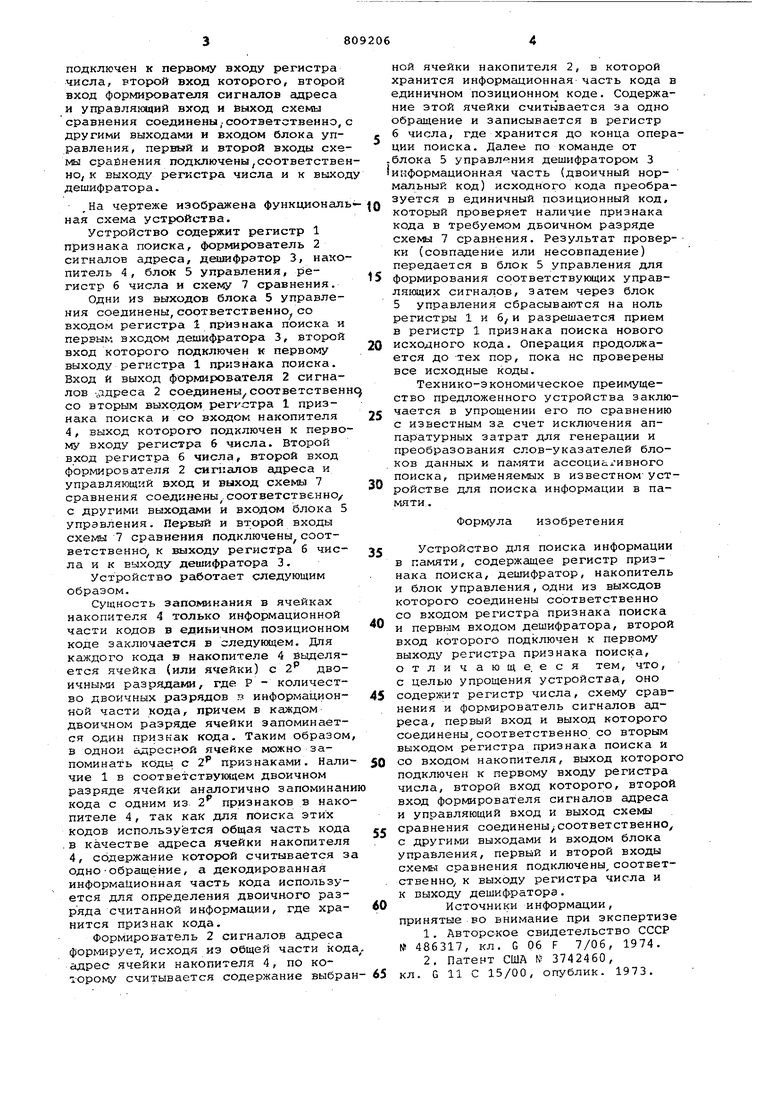

0 со входом накопителя, выход которого подключен к первому входу регистра числа, второй вход которого, второй вход формирователя сигналов адреса и управляющий вход и выход схемы сравнения соединены,.соответственно, другими выходами и входом блока управления, первый и второй входы схе мы срайнения подключены,соответстве но, к выходу регистра числа и к выхо дешифр атор а. ,На чертеже изображена функционал ная схема устройства. Устройство содержит регистр 1 признака поиска, формирователь 2 сигналов адреса, дешифратор 3, нако питель 4, блок 5 управления, регистр б числа и схему 7 сравнения. Одни из выходов блока 5 управления соединены,соответственно, со входом регистра 1 признака поиска и первым входом дешифратора 3, второй вход которого подключен к первому выходу регистра 1 признака поиска. Вход И выход формирователя 2 сигналов -.адреса 2 соединены соответствен со вторым выходом регистра 1 признака поиска и со входом накопителя 4, выход которого подключен к перво му входу регистра 6 числа. Второй вход регистра б числа, второй вход формирователя 2 сигналов адреса и управляющий вход и выход схемы 7 сравнения соединены соответственно/ с другими выходами и входом блока 5 управления. Первый и второй входы схемы 7 сравнения подключены соответственно к выходу регистра б числа и к выходу дешифратора 3. Устройство работает следующим образом. Сущность запоминания в ячейках накопителя 4 только информационной части кодов в единичном позиционном коде заключается в следукхцем. Для каждого кода в накопителе 4 выделяется ячейка {или ячейки) с двоичными разрядами, где Р - количество двоичных разрядов в информационяой части кода, причем в каждом двоичном разряде ячейки запоминается один признак кода. Таким образом в одной адресной ячейке можно запоминать коды с 2 признаками. Нали чие 1 в соответствующем двоичном разряде ячейки аналогично запоминан кода с одним из 2 признаков в нако пителе 4, так как для поиска этих кодов используется общая часть кода в качестве адреса ячейки накопителя 4, содержание которой считывается з одно-обращение, а декодированная информационная часть кода используется для определения двоичного разряда считанной информации, где хранится признак кода. Формирователь 2 сигналов адреса фop 1иpyeт, исходя из общей части код гщрес ячейки накопителя 4, по которому считывается содержание выбра ной ячейки накопителя 2, в которой хранится информсщионная часть кода в единичном позиционном коде. Содержание этой ячейки считывается за одно обращение и записывается в регистр б числа, где хранится до конца операции поиска. Далее по команде от блока 5 управления дешифратором 3 информационная часть (двоичный нормальный код) исходного кода преобразуется в единичный позиционный код, который проверяет наличие признака кода в требуемом двоичном разряде схемы 7 сравнения. Результат проверки (совпадение или несовпадение) передается в блок 5 управления для формирования соответствующих управляняцих сигналов, затем через блок 5 управления сбрасываются на ноль регистры 1 и 6, и разрешается прием в регистр 1 признака поиска нового исходного кода. Операция продолжается до тех пор, пока не проверены все исходные коды. Технико-экономическое преимущество предложенного устройства заключается в упрощении его по сравнению с известным за счет исключения аппаратурных затрат для генерации и преобразования слов-указателей блоков данных и памяти ассоциативного поиска, применяемых в известном устройстве для поиска информации в памяти. Формула изобретения Устройство для поиска информации в памяти, содержащее регистр признака поиска, дешифратор, накопитель и блок управления, одни из выходов которого соединены соответственно со входом регистра признака поиска и первым входом дешифратора, второй вход которого подключен к первому выходу регистра признака поиска, отличающе. еся тем, что, с целью упрощения устройства, оно содержит регистр числа, схему сравнения и форлшрователь сигналов адреса, первый вход и выход которого соединены,соответственно со вторым выходом регистра признака поиска и со входом накопителя, выход которого подключен к первому входу регистра числа, второй вход которого, второй вход формирователя сигналов адреса и управляющий вход и выход схемы сравнения соединены соответственно с другими выходами и входом блока управления, первый и второй входы схемы сравнения подключены, соответственно к выходу регистра числа и к выходу дешифратора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 486317, кл, G 06 F 7/06, 1974. 2,Патент США N- 3742460, кл. G 11 С 15/00, опублик. 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска информации в памяти | 1986 |

|

SU1392579A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| Ассоциативное запоминающее устройство | 1984 |

|

SU1234880A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Ассоциативное запоминающее устройство | 1986 |

|

SU1388949A1 |

Авторы

Даты

1981-02-28—Публикация

1979-06-07—Подача