I Изобретение относится к згшсжинающим устройствам. Известно устройство, которое содержит блок памяти, информационшШ вход которого соединен с источником информации, информационный выход соединен с ПРИ&4НИКОМ информгщии, счётчик адреса, выход которого соединен с гщресным входом блока памяти; и уст ройство управления, первый выход которого соединен с управляющим входом блока памяти, а второй, третий и четвертый выходы соединены соответственно с первым, вторым и третьим входами счетчика адреса . Недостатком этого устройства является то, что порядок выдачи информации из устройства обратен порядку поступления информации на его вход. Наиболее близким по техническому решению к предлагаемому является буферное запоминающее устройство, содержащее блок памяти, первый регистр адреса, хранящий и указывающий номер ячейки блока памяти, из которой извлекается информация, второй регистр адреса, хранящий и указывающий номер ячейки блока памяти, в которую помещается информация рЗ. Недостатком этого устройства является низкое бьютрсщействи е при больших сксфостях поступления информации на его вход, так как в этом устройстве операции эаписи информации, модификации адреса и сравнения гщресов выполня« тся { итоледовательно. Цель изобретения - повышение быстрсдействия буферного запокмнающего Устройства. Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее первый накопитель, блок управления и два счетчика, причем информацион1а1е вход и выход первого накопителя соединены с информационными входом и выходом устройства соответственно, а первые и вторые входы и выходы блока управления соответственно с первьши и вторыми входами и т:1ходг1ми устройства, первый и второй гшресные входы и первый адресный и третий выходы блока управления подключены соответственно к выходу первого счетчика, к выходу второго счетчика, к адресному и к управляющему входам первого накопителя, первые входы первого и второго счетчиков соединены с четвертым выходом блока управления, а вторые входы парвого и второго счетчиков - соответственно с пятым и шестым выходами блока управления, введены второй нако-. питель, третий, четвертый и пятый счетчики, дешифратор и два элемента ИЛИ, причем первые входы третьего, ггетвертого и питого счетчиков подключены к четвертому выходу блока управления , а вторые входы третьего и четвертого-счетчиков - соответственно к седьмому и восьмому входам блока управления, первые входы первого и второго элементов ИЛИ соединены соответственно со вторыми входами первого и второго счетчиков, а вторые входы - соответственно со вторыми входами третьего и четвертого счетчиков, выходы первого и второго элементов ИЛИ подключены соответственно ко второму и третьему входам пятого счетчика, выход, которого подключен ко входу дешифратора, первой и второй выходы которого и выходы третьего и четвертого счетчиков соединены соответственно с третьим и четвертым входами и с третьий и четвертым адресными входами блока управления, адресный и управляющий входы второго накопителя подключены соответственно ко второму адресному и девятому выходам блока управления, а информсщионные вход и выход второго накопителя - соответственно к информационным входу и выходу первого накопителя.

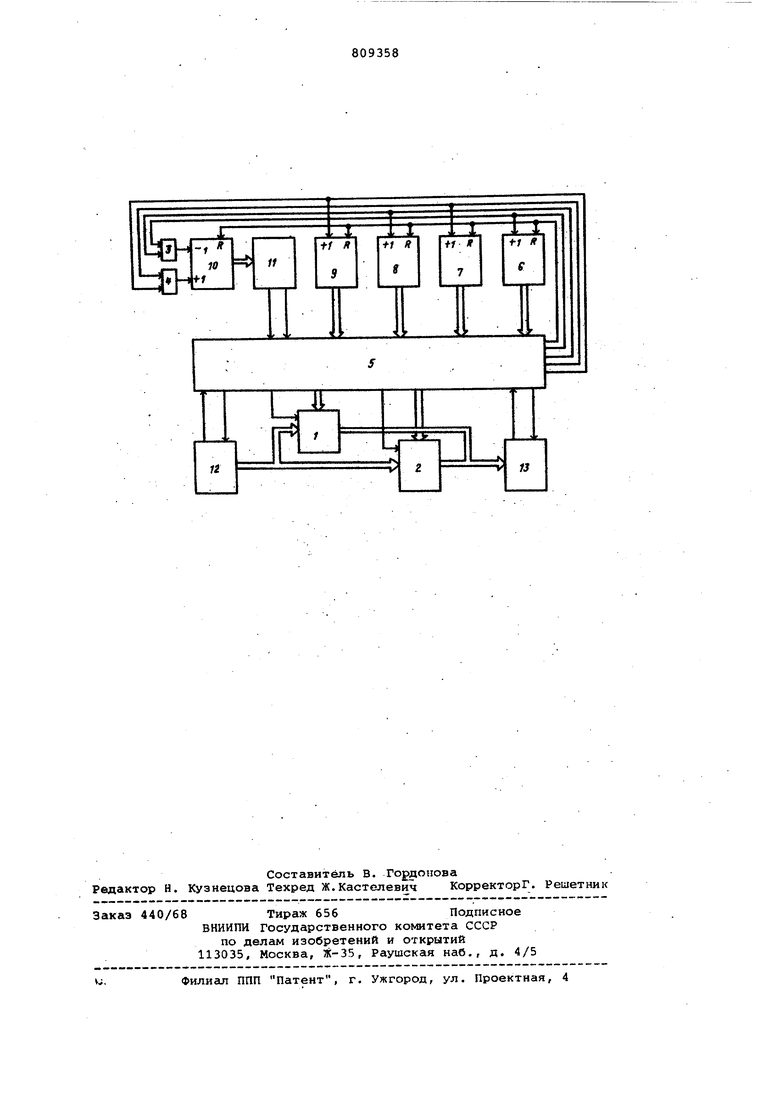

На чертеже приведена структурная схема предлагаемого устрс ства.

Устройство содержит первый 1и второй 2 накопители, первый 3 и второй. 4 элементы ИЛИ, блок 5 управления ,первый б, второй 7, третий 8, четвертый 9 и пятый 10 счетчики и дешифратор 11..

информационные вход и выход первого накопителя 1 соединегаа с информационными входом и выходе устройства соответственно. Первые и вторые входы и выходы блока 5 управления подключены соответственно к первым и вторым вводам и выходам устройства.

Первый и второй адресные входы и первый адресный и третий выходы блока 5 управления соединены соответственно с выходом первого счетчика 6 г с выходом второго счетчика 7, с адрёсшлм и с управляющим входами первого Накопителя 1. Первые входа первого б в.торого 7 счетчиков соединены с четвертым выходом блока 5 управления, а вторые входы первого б и второго 7 счетчик ов - соответственно с пятым и шестым выходами блока 5 управления. Первые входы третьего В,, четвертого 9 и пятого 10 счетчиков подключены к четвертому выходу блока 5 управления, а вторые входы третьего 8 и четвертого 9 счетчиков - соответственно к седьмому и восьмому входам блока 5 управления. Первые входы первого 3 и второго 4 элементов ИЛИ соединены

соответственно со вторыми входами первого 6 и второго 7 счетчиков, а вторые входы - соответственно со вторыми входами третьего 8 и четвертого 9 счетчиков, выходы первого 3 и второго 4 элементов ИЛИ подключены соответственно ко второму и третьему входам пятого счетчика 10. Выход которого подключен ко входу дешифратора 11. Первый и второй выходы дешифратора 11 и выходы третьего 8 и четвертого 9 счетчиков соединены соответственно с третьим и четвертым входами и с третьим и с четвертым адресными входами блока 5 управления. Адресный и управляющий входы второго накопителя 2 подключены соответственно ко второму адресному и девятому выходам блока управления 5, а информационные вход и выход второго накопителя 2 соответственно к информационным входу и выходу первого накопителя 1. Первые вход и выход и информационный вход устройства соединяются с соответству{Ьщими выходами и входом источника ин формации 12. Вторые вход и выход и информационный выход устройства подключаются к соответствующим входам и выходу приемника информации 13.

Устройство работает следукидим образом.

В исходном состоянии блок 5 управления вырабатывает ситнгш на четвертом выходе и устанавливает в нулевое состояние все пять счетчиков 6-10. Дешифратор 11 дешифрирует нулевое сО-, стояние пятого счетчика 10 и формирует на четвертом входе блока 5 управления осведомителыалй сигнал Буферное запоминающее устройство свободно . Устройство будет оставаться в этом состоянии до тех пор, пока на входе не появится информация. В этом случае источник информации 12 возбудит первый вход блока 5 управления.

Блок 5 управления подключит выход второго счетчика 7 к адресному входу первого накопителя 1, а выхсщ четвертого счетчика 9 - ко входу второго накопителя 2 и таким образсм подготовит устройство к приему информации.

Первое слово входной информации будет помещено в первый накопитель 1, в ячейку с адресом О путем подачи на его управляющий вхсд импульса Запись, одновременно содержимое четвертого счетчика 9 и пятого счетчика 10 будет увеличено на 1. Второе слово информации будет помещено во второй накопитель 2, в ячейку с адресом 1 путем подачи на его управлякиций вход импульса Запись, одновременно содержимое второго счетчи ка 7 и пятого счетчика 10 будет увеличено на 1. Третье слово информации будет помещено в первый накопитель 1, в .Ячейку с адресом 1, четвертое - во второй накопитель 2, в ячейку с адресом 3 и т.д. Входной процесс будет продолжаться до тех пор, пока источник информации 12 не прекратит выдачу информации, либо пока не будут заполнены накопители 1 и 2. В последнем случае на втором выходе дешифратора будет сформирован си нал SaiHHTo. После окончания входно го процесса через блок 5 управления подключен к адресному входу накопите пя 1 выход первого счетчика б, а к адресному входу второго накопителя выход третьего счет.чика 8. Затем будет происходить считывание информации из устройства и выдача ее потреб телю. Сначала блок 5 управления сфор мирует сигнал считывания на входе первого накопителя 1 и одновременно выдаст сигнал увеличения содержимого третьего счетчика 8 и уменьшения со держимого пятого счетчика 10 на 1. При этом первое слово информации из :Первого накопителя 1 из ячейки памяти О будет выдано потребителю. Затем будет сформирован сигнал считывгь ния на входе второго накопителя и одновременно сигнал увеличения содер жимого первого счетчика 6 и уменьшения содержимого пятого счетчика 10 на 1. В результате будет считано второе слово информации из второго накопителя 2 из ячейкиПамяти 1. Таким образом, выходной процесс будет продолжаться до тех пор, пока не будет ввдана вся информация из накопителей 1 и 2, и на первом выходе дешифратора 11 не будет сформирован осведомительный сигнгш Свободно, либо пока источник информации 12 не выдаст очередной массив информации. Во втором случае выходной процесс бу дет прерван и устройство перейдет в состояние приема информации. Технико-экономическое преимуществ предлагаемого устройства заключается в том, что в нем длительность цикла записи информации уменьшена в три ра за по сравнению с известным устройством, что существенно повышает . быстродействие буферного эапоминг«ощего устройства. ; Формула изобретения Буферное запоминающее устройство, содержащее первый накопитель, блок управления и два счетчика, причем информационные вход и выход первого накопителя соединены с информационными входом и выходом устройства соответственно, а первые и вторые входы и выходы блока управления -соответственно с первыми и вторыми входами и выходами устройства, первый и второй адресные входы и первый адресный и третий выходы блока управления подключены соответственно к выходу первого счетчика, к выходу второго счетчика, к адресному и к управляющему входам первого накопителя, первые входы первого и второго счетчиков соединены с четвертым выходом блока управления, а вторые входы первого и второго счетчиков - соответственно с пятым и шестым выходами блока управления, отличающееся тем, 4TOj с целью повьвпения быстродействия устройства, оно содержит второй накопитель, третий, четвертый и пятый счетчики, дешифратор и два элемента ЛИ, причем первые входы третьего, четвертого и пятого счетчиков подключены к четвертому выходу блока управления, а вторые входы третьего и четвертого счетчиков - соответственно к седьмому и восьмому входам блока управления, первые входы первого и второго элементов ИЛИ соединены соответственно со вторыми входагФ первого и второго счетчиков, а вторые входы - соответственно со вторыми входами третьего и четвертого счетчиков, выходы первого и -второго элементов ИЛИ подключены соответственно ко второму и третьему входам пятого счетчика, выход которого подключен ко входу дешифратора, первый и второй выходы которого и выходам третьего и четвертого счетчиков соединены соответственно с третьим и четвертым входами и с третьим и четвертым ащресными входами блока управления, адресный и управляющий входы второго накопителя псздключены соответственно ко второму адресному и девятому выходам блока управления, а информационные вход и выход второго накопителя - соответственно к информсщионным входу и выходу первого накопителя. Источники информации, принятые во внимание при экспертизе 1.Майоров С.А. и Новиков Г.И. Принципы организации цифровых машин. Л., Мсшмностроение, 1974, с.388. 2.Патент Японии № 30982, кл. 97/7/С, опублик. 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Многоканальное буферное запоминающее устройство | 1980 |

|

SU903971A1 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Адресно-коммутационное устройство | 1987 |

|

SU1515378A1 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| Устройство для программного сопряжения электронных вычислительных машин | 1976 |

|

SU641434A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

Авторы

Даты

1981-02-28—Публикация

1979-05-31—Подача