Наиболее близким к изобретению является ЗУ оперативной памяти, содержащее адресный регистр, блок накопителя в состав адресного дешифратора, накопителя и разрядных формирователей, блок ввода-вывода информации в составе блоков кодирования и декодирования и регистра слова .блока управления ГЛ и f2 .

Однако в системе обработки данных оперативная память которой имеет многоблочную структуру и исп,ользует в качестве блоков памяти описанное ЗУ отказ нерезервированного блока памяти требует для восстановления работоспособности системы в общем случае не только перенесения всей или части информации, размещавшейся в отказавшем блоке в другой блок оперативной памяти, но и редактирование связей всех тех точек других блоков, из которых происходило обращение к ячейкам отказавшего блока памяти.

Известные ЗУ не могут быть настроны на различные поля пространства адресов оперативной памяти системы Обработки данных, находясь в одном и том же установочном месте системы с многоблочной оперативной памятью. Поэтому в системе, оперативная памят которой состоит из одинаковых блоков , невозможно управлять кратностью резервирования блоков памяти. В результате оказывается сложным автоматическое восстановление работоспособности системы после выхода из строя одного из блоков нерезервированого участка памяти.

Целью изобретения является повышение надежности, унификации и расширение функциональных возможностей ЗУ за счет настройки устройства переадресации накопителя информации на различные значения из пространства адресов ячеек памяти системы обработки данных.

Поставленная цель достигается тем, что в устройство переадресации накопителя информации системы обработки, содержащее блок селекции,блок хранения адреса, накопитель информации, блок ввода-вывода и блок управлния, причем первый вход блока селекции является установочным входом устройства, второй вход является пеРвым адресным входом устройства, а выход соединен с первым входом блока управления, вход которого является управляющим входЬм устройства выход блока хранения адреса соединен с адресным входом накопителя информации , информационный вход которого соединен с первым выходомблока ввода-вывода, информационный выход накопителя информации соединен с первым входом блока ввода-вывода, второй вход блока ввода-вывода является информационны входом устройства, а второй выход - соответственно информационньлм выходом устройства., трети вход блока ввода-вывода соединен с выходом блока управления, четвертый вход является установочным входом устройства, введены регистр-идентификатор адресов ячеек, блок селекци адресов ячеек и шифратор внутренних соединений. Вход регистра - идентифкатора адресов ячеек соединен с первым выходом блока ввода-вывода, выход с .первым входом блока селекции адресов ячеек и пят1лм входом блока ввод а-выв од а. Второй вход блока селекции адресов ячеек соединен с выходом ишфратора внутренних соединений, третий вход является вторым адресным входом устройства, четвертый вход соединен со вторым выходом блока управления, а выход со входом блока хранения адреса.

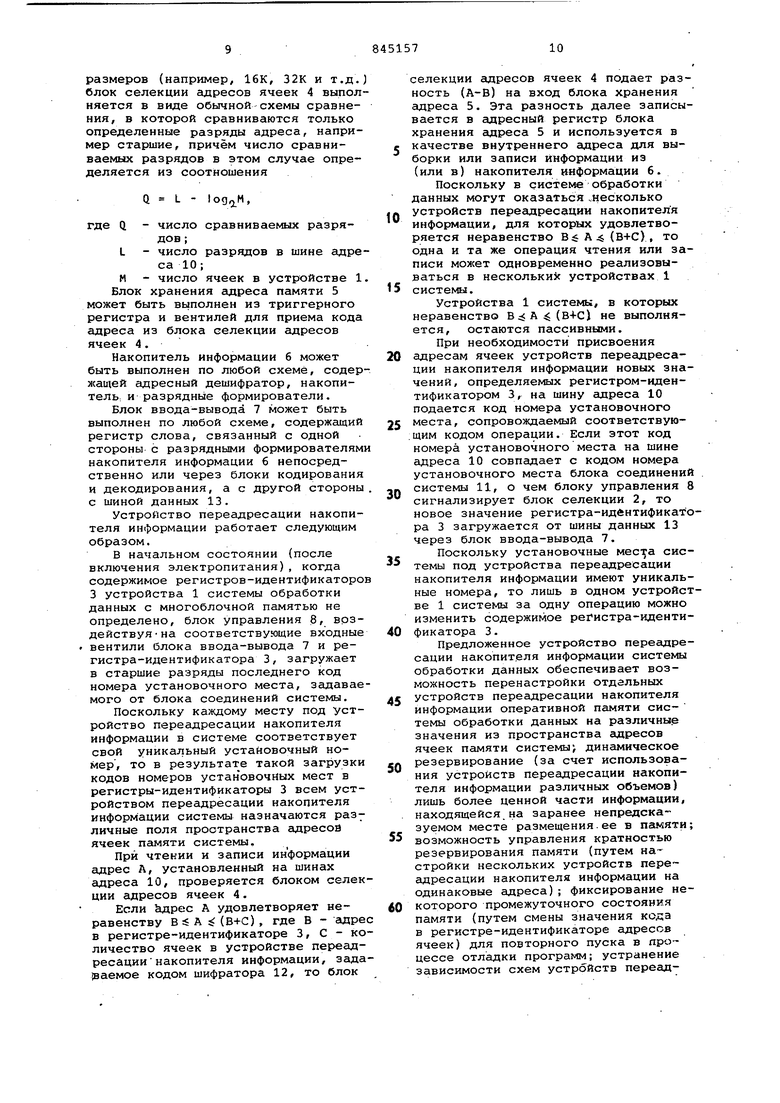

На фиг. 1 изображена структурная схема устройства переадресации накопителя информации в системе обработки данных,- на фиг. 2 - вариант схемы блока ввода-вывода, блока управлени шифратора внутренних соединений и блока соединений системы.

Устройство переадресации накопителя информации 1 содержит блок селекции 2 для сравнения кода, находящегося на шинах адреса, с кодом номера установочного места, подаваемым от блока соединений системы, регистр-идентификатор адресов ячеек 3 для хранения кода адреса первой ячейки из пространства адресов ячеек памяти системы, блок селекции адресов ячеек 4 для сравнения кода адреса, находящегося на шине адреса, с границами поля адресов, определяемыми кодом, находящимся в регистре-идентификаторе 3,и кодом соответствующим количеству адресуемых ячеек, и для формирования кода адреса ячейки внутри блока адреса 5 для хранения адреса той ячейки, к которой происходит обращение в текущий цикл работы данного накопителя информации б для записи,хранения и выборки информации, блок ввода-вывода 7 для ввода информации в накопитель информации 6 от шины данных и в регистр-идентификатор 3 от шины данных и от блока соединений системы, для вывода на шину данных информации из накопителя информации 6, из регистра-идентификатора 3, от блока соединений системы, блок управления 8 для приема и передачи управляющих сигналов от процессора 9 и к процессору 9 системы обработки данных для управления работой устройства переадресации накопителя информации, шифратор внуренних соединений для хранения количества адресуемых ячеек в устройстве переадресации накопителя информации .

Первый вход блока селекции 2 является установочным входом устройства переадресации накопителя информации 1, который соединен с выходом блока соединений системы. Число разрядов Р кода номера установочного места, хранящегося в блоке соединений системы, связано с максимально возможным в системе числом N установочных мест для устройств переадресации накопителя информации 1

соотношением (р-1) Р. Второй вход блока селекции 2 является первым адресным входом устройства переадресации накопителя информации 1, который через шину с1Дреса 10 соединен с адресным выходом процессора 9. Выход блока селекции 2 соединен с первым входом блока управления 8, второй вход которого является управляющим входом ЗУ переадресации накопителя.информации 1. Управляющий вход устройства переадресации накопителя информации 1 чере шину управления соединен с управляющим выходом процессора 9.

Вход регистра-идентификатора 3 соединен с первым выходом блока вводвывода 7, выход с первым входом блока селекции адресов ячеек 4 и пятым входом блока ввода-вывода 7.

Второй вход блока селекции адресо ячеек 4 соединен с выходом шифратора внутренних соединений, хранящим код количества адресуемых ячеек, число разрядов п в котором связано с числом М ячеек соотношением

(n-i:

i- n

Третий вход блока селекции адресов ячеек 4 является вторым адресным входом устройства переадресации накопителя информации 1, который через шину адреса 10 соединен с адресным выходом процессора 9. Четвертый вход блока селекции адресов ячеек 4 соединен с выходом блока управления 8, выход - со входом блока хранения адреса 5. Выход блока хранения адреса 5 соединен с адресным входом накопителя информации б, информационный вход которого соединен с первым выходом блока ввода-вывода 7. Информационный выход накопителя информации б соединен с первым входом блока ввода-вывода 7. Информационный выход устройства переадресации накопителя информации 1 является вторым выходом блока ввода-вывода 7 и Через шину информации соединен с информационным входом-выходом процессора 9. Третий вход блока ввода-вывода 7 соединен с выходом блока управления 8, четвертый вход является установочным входом устройства 1.

Блок селекции 2 выполнен по комбинационной схеме параллельного сравнения кодов. С выхода блока селекции

2 блок управления 8 получает сиг нал совпадения кода на шине адреса 10 с кодом номера установочного места.

Регистр-идентификатор 3 состоит из триггерного регистра и вентилей для приема кода из блока ввода-вывода 7 .

Блок селекции адресов ячеек 4 построен так, что в нем, во-первых, определяется разность между адресом, образованным суммой кода из

0 регистра-идентификатора 3 и кода количества адресуемых ячеек памяти От шифратора внутренних соединений, и адресом от шины адреса 10 и, вовторых, определяется разность между

5 - адресом от шины адреса 10 и адресом из регистра-идентификатора 3.

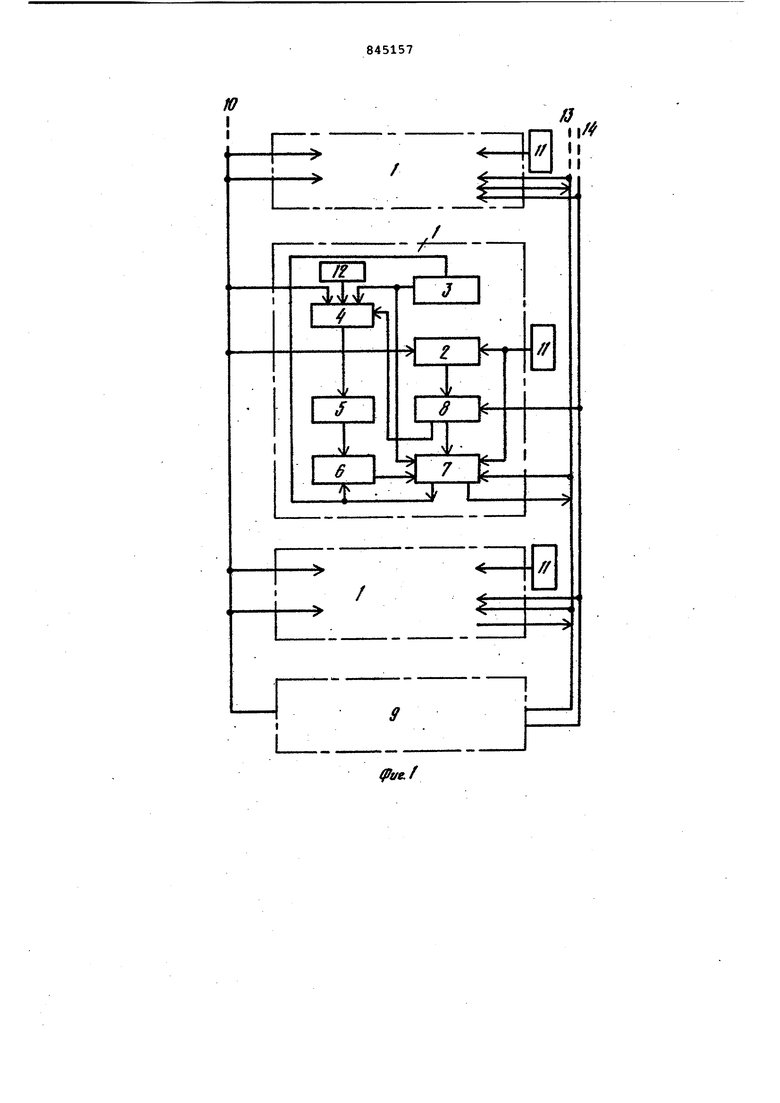

На фиг.,2 изображено устройство переадресации накопителя информации 1 систе1 5Ы обработки данных, на ко0тором в более развернутом виде показана реализация блока ввода-вывода 7, блока управления 8, блока соединений системы 11 и блока внутренних соединений 12. Информация с шины данных 13 заносится в регистр-иден5тификатор 3.

Блок управления 8 в основном служит для выполнения двух главных функций: выдачи необходимых последовательностей сигналов для управле0ния накопителем информации б и сигналов опроса и изменения состояния регистра-идентификатора 3.

От процессора 9 по шине управления 14 поступают сигналы управления

5 (например, в виде двоичного кода) в блок управления 8 на дешифратор 15. Дешифратор 15 подает сигнал на один из вeнтиJleй 16,17 или на одну из линий задержки 18 и 19 при появле0нии на шине управления 14 соответственно сигналов Запись в регистр, Чтение регистра, Запись в память и Чтение памяти.

Последние два выхода дешифратора 15 (Запись в память, Чтение па5мяти) также подключены к схеме ИЛИ 20. При подаче сигнала Сброс на шину управления 14 дешифратор 15 подает сигнал на входы группы вентилей 21.

0

Блок ввода-вывода 7 может быть представлен в нашем случае как пять групп вентилей 21-25.

К первым-входам группы вентилей 21 подключен выход блока соединений

1 системы 11, а вторые входы подключены к выходу дешифратора 15.

Первые входы группы вентилей 22 подключены к выходу вентиля 16, а вторые входы - к шине данных 13.

С

Выходы групп вентилей 21 и 22 объединены и подключены на вход регистра-идентификатора 3 .

Первые входы группы вентилей 23, 24, 25 подключены соответ :твенно к выходу вентиля 17 и к выходам линий задержек 18 и 19.

Вторые входы групп вентилей 23, 24 и 25 подключены соответственно к выходу регистра-идентификатора 3, к одному входу накопителя информации б и к выходу накопителя информации 6.

Блок соединений системы 11 выполнен как шифратор, подключение к которому производится через разъем 26.

Допустим для простоты в системе предусмотрено шестнадцать уЬтановочных мест для установки устройств памяти. Таким образом, для идентифика.ции установочного места достаточно четырех двоичных разрядов (проводов)

Провода внешней части разъема 6 подключаются к соответствующим полюсам источника питания для подачи конституент О или 1, т.е. шифруются так, чтобы образрвать уникальное значение номера для данного установочного места (fia фиг.2 это 0101). Внутренняя часть разъема 26 соединена с первым входом блока селекции 2 и с первыми входами группы вентилей 21

Каждый раз при переустановке устройства 1 на- новое установочное место (путем соединения через разъем 26) его номер формируется блоком соединений системы 1 в виде двоичного чис51а, отличающегося от прежнего.

Аналогично выполнен шифратор внутренних соединений 12, с той лишь разницей, что в нем отсутствует разъем (так как устройство постоянно находится внутри) и разрядность формируемого шифратора кода характеризует объем накопителя информации.

Таким образом, код количества адресуемых ячеек памяти, образованный путем подключения к соответствующим полюсам источника питания (шифрация конституент О и 1) шифратора внутренних соединений 12, постоянно постуЬает на один из входов блока селекции адресов ячеек 4.

Блок управления 8 устройства 1 работает следующим Ьбразом. Пусть по шине управления 14 поступил сигнад Сброс. Этот сигнал поступает с выхода дешифратора 15 на опрос группы вентилей 21, в результате чего в каждом из устройств 1 в регистры идентификаторы 3 записывается код номера установочного места.

Таким образом, обеспечивается последующее дифференццрованное обращение к их накопителям информации б

Состояние регистра-идентификатора 3 может быть изменено следующим образом. Пусть по шине управления 14 поступил сигнал Запись в регистр, на шину адреса 10 подан код, указывающий в каком устройстве должна быть выполнена эта установка, а на шине данных.13 имеется информация, . которую надо записать в регистридентификатор 3. Тогда то устройство 1, в котором совпали значения информации на шине адреса 10 и кода номера установочного места, вырабатывает сигнал разрешения на выходе J блока селекции 2 и открывает вентиль

16для прохождения сигнала Запись в регистр, вьщеляемого дешифратором 15 для опроса группы вентилей 22.

В результате информация с шины Q данных 13 заносится в регистр-иден. тификатор 3.

Аналогично производится чтение содержимого этбг0 регИйтра. При поступлении сигнала Чтение регистра по шине управления 14 и соответствующего кода на шинах адреса 10 в одном из устройств 1 срабатывает блок селекции 2 и открывает вентиль

17для прохождения сигнала Чтение регистра, выделяемого дешифратором

0 15 для опроса группы вентилей 23. В результате Информация из регистраидентификатора адресов ячеек 3 поступает на шину данных 13; Для обращения к накопителю информации б по шине управления передаются сигналы Запись в память или Чтение памяти, которые проходя через дешифратор 15 поступают на схему ИЛИ 20 и на одну из линий задержек

Q 18 или 19 соответственно.

Сигнал с выхода схемы ИЛИ 20 поступает в блок селекции адресов ячеек 4. Одновременно на этот блок подаются информация с шин адреса 10,

данные регистра-идентификатора 3 и код количества адресуемых в устройство 1 ячеек памяти из шифратора внутренних соединений 12. Если адрес, заданный на шине адреса 10, попадает в пространство адресов , определяемое

0 настройкой и объемом данного устройства управления (см.ниже), то на выходе блока селекции адресов ячеек 4 формируются фактический адрес и сигнал обращения к накопителю информации 6, передаваемые через блок хранения адреса 5. Если адрес, заданный на шине адреса 10, не попадает в указанное пространство адресов, блок селекции адресов ячеек 4 не срабатывает и операция обращения к накопителю информации 6 в данном устройстве памяти не начинается. .

В случае обращения по сигналу Запись в память работает группа вентилей 24, которая по сигналу с

выхода линии задержки 18 пропускает информацию с шины данных 13 на вход накопителя информации 6.

Если происходит обращение по сигналу Чтение памяти, то работает

0 группа вентилей 25, которая по сигналу с выхода линии задержки 19 считывает информацию из накопителя информации 6 на шину данных 13.

В частном случае при использовании

5 накопителей информации 6 стандартных

размеров (например, 1бК, 32К и т.д. блок селекции адресов ячеек 4 выполняется в виде обычной схемы сравнения, в которой сравниваются только определенные разряды адреса, например старшие, причём число сравниваемых разрядов в этом случае определяется из соотношения

( log,j,M,

где Q - число сравниваемых разрядов ; L - число разрядов в шине гщреса 10; М - число ячеек в устройстве 1

Блок хранения адреса памяти 5 может быть выполнен из триггерного регистра и вентилей для приема кода адреса из блока селекции адресов ячеек 4.

Накопитель информации б может быть выполнен по любой схеме, содержащей адресный дешифратор, накопитель, и разрядные формирователи.

Блок ввода-вывода 7 может быть выполнен по любой схеме, содержащий регистр слова, связанный с одной стороны с разрядными формирователям накопителя информации 6 непосредственно или через блоки кодирования и декодирования, а с другой стороны с шиной данных 13.

Устройство переадресации накопителя информации работает следующим образом.

В начальном состоянии (после включения электропита;ния) , когда содержимое регистров-идентификаторо 3 устройства 1 системы обработки данных с многоблочной памятью не определено, блок управления 8, воздействуя -на соответствующие входные вентили блока ввода-вывода 7 и регистра-идентификатора 3, загружает в старшие разряды последнего код номера установочного места, задаваемого от блока соединений системы.

Поскольку каждому месту под устройство переадресации накопителя информации в системе соответствует свой уникальный установочный номер, то в результат е такой загрузки кодов номеров установочных мест в регистры-идентификаторы 3 всем устройством переадресации накопителя информации системы назначаются раз-;личные поля пространства гщресой ячеек паимяти системы,

При чтении и записи информации адрес Л, установленный на шинах адреса 10, проверяется блоком селекции адресов ячеек 4.

Если йдрес А удовлетворяет неравенству В« А (В+С) , где В - адре в регистре-идентификаторе 3, С - количество ячеек в устройстве переадресации накопителя информации, зада|ваемое кодом шифратора 12, то блок

селекции гщресов ячеек 4 подает разность (А-В) на вход блока хранения адреса 5. Эта разность далее записывается в адресный регистр блока хранения адреса 5 и используется в качестве внутреннего адреса для выборки или записи информации из (или в) накопителя информации 6.

Поскольку в системе обработки данных могут оказаться .несколько устройств переадресации накопителя информации, для которых удовлетворяется неравенство В$ А« (В+С) , то одна и та же операция чтения или записи может одновременно реализовываться в нескольким устройствах 1 системы.

Устройства 1 системы, в которых неравенство В4А4(В-(-С) не выполняется, остаются пассивными.

При необходимости присвоения адресам ячеек устройств переадресации накопителя информации новых значений, определяемых регистром-идентификатором 3, на шину ёщреса 10 подается код номера установочного места, сопровождаемый соответствую:щим кодом операции. Если этот код номера установочного места на шине адреса 10 совпадает с кодом номера установочного места блока соединени системы 11, о чем блоку управления сигнализирует блок селекции 2, то новое значение регистра-идйнтификатра 3 загружается от шины данных 13 через блок ввода-вывода 7.

Поскольку установочные места системы под устройства переадресации накопителя информации имеют уникальные номера, то лишь в одном устройсве 1 системы за одну операцию можно изменить содержимое регистра-идентификатора 3.

Предложенное устройство переадресации накопителя информации системы обработки данных обеспечивает возможность перенастройки отдельных устройств переадресации накопителя информации оперативной памяти сиетемы обработки данных на различные значения из пространства адресов ячеек памяти системы; динамическое резервирование (за счет использования устройств переадресации накопителя информации различных объемов) лишь более ценной части информации, находящейся на заранее непредсказуемом месте размещения, ее в па1мяти возможность управления кратностью резервирования памяти (путем настройки нескольких устройств переадресации накопителя информации на одинаковые адреса); фиксирование некоторого промежуточного состояния памяти (путем смены значения кода в регистре-идентификаторе адресов ячеек) для повторного пуска в процессе отладки программ; устранение зависимости схем устройств переадресации накопителя информации от числа абонентов памяти, а также устранения зависимости схем абонентов памяти от количества ячеек в устройстве переадресации накопителя информации и количества самих устройств переадресации накопителя-информации в системе; простоту подключения дополнительных устройств переадресации накопителя информации (в том числе и резервных) без прокладки индивидуального интерфейса. Формула изобретения Устройство переадресации накопителя информации системы обработки д ных,содержащее блок селекции, блок хранения адреса, накопитель информации, блок ввода-вывода и блок управ ления, причем первый вход блока селе .ции является установочным входом устройства, второй вход - первым ад ресным входом устройства , а выход соединен с первым входом блока управ ления, второй вход которого являетс управляющим входом устройства, выход блока хранения гщреса соединен с сщресным входом накопителя информации, информационный вход которого с динен с первым выходом блока вводавывода, а информационный выход нако пителя информации соединен с первым входом блока ввода-вывода, второй вход блока ввода-вывода является ин формационным входом устройства, а второй выход - соответственно информационным выходам устройства,третий вход блока ввода-вывода соединен с выходом блока управления, а четвертый вход является установочным входом устройства, отличающееся тем, что, с целью повьошения надежности и. расширения функциональных возможностей за счет настройки устройства на различные значения из пространства адресов ячеек памяти системы обработки данных, в него введены регистр-идентификатор адресов ячеек, блок селекции адресов ячеек и шифратор внутренних соединений, причем ВХОД регистра-идентификатора адресов ячеек соединен с первым выходом блока ввода-вывода, выход регистра-идентификатора адресов ячеек соединен с первым входом блока селекции адресов ячеек и пятым входом блока ввода-вывода, второй вход блока селекции адресов ячеек соединен с выходом шифратора внутренних соединений,третий вход блока селекции адресов ячеек является вторым адресным входом устройства, четвертый вход блока селекции адресов ячеек соединен со вторым выходом блока управления, а выход - со входом блока хранения адреса. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 297070, кл. G 11 С 9/04, 1969. 2.Авторское свидетельство СССР № 377873, кл. G 11 С 9/06, 1970 (прототип).

ю

,/.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переадресации накопителя информации системы обработки данных | 1982 |

|

SU1072053A2 |

| Устройство для сопряжения ЦВМ и накопителя информации | 1985 |

|

SU1265780A1 |

| Модульная многоуровневая система коммутации процессоров | 1984 |

|

SU1249524A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для сопряжения каналов ввода-вывода | 1975 |

|

SU559234A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Устройство для ввода информации | 1979 |

|

SU840870A1 |

Авторы

Даты

1981-07-07—Публикация

1979-06-04—Подача