00 00

00 ел

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах, интерпретирующих программу, записанную на языке высокого уровня, мини-машинах, не имеюших программных средств динамического распределения памяти, а также для страничного обмена между оперативным и внешними запоминаюш,ими устройствами.

Целью изобретения является повышение быстродействия устройства.

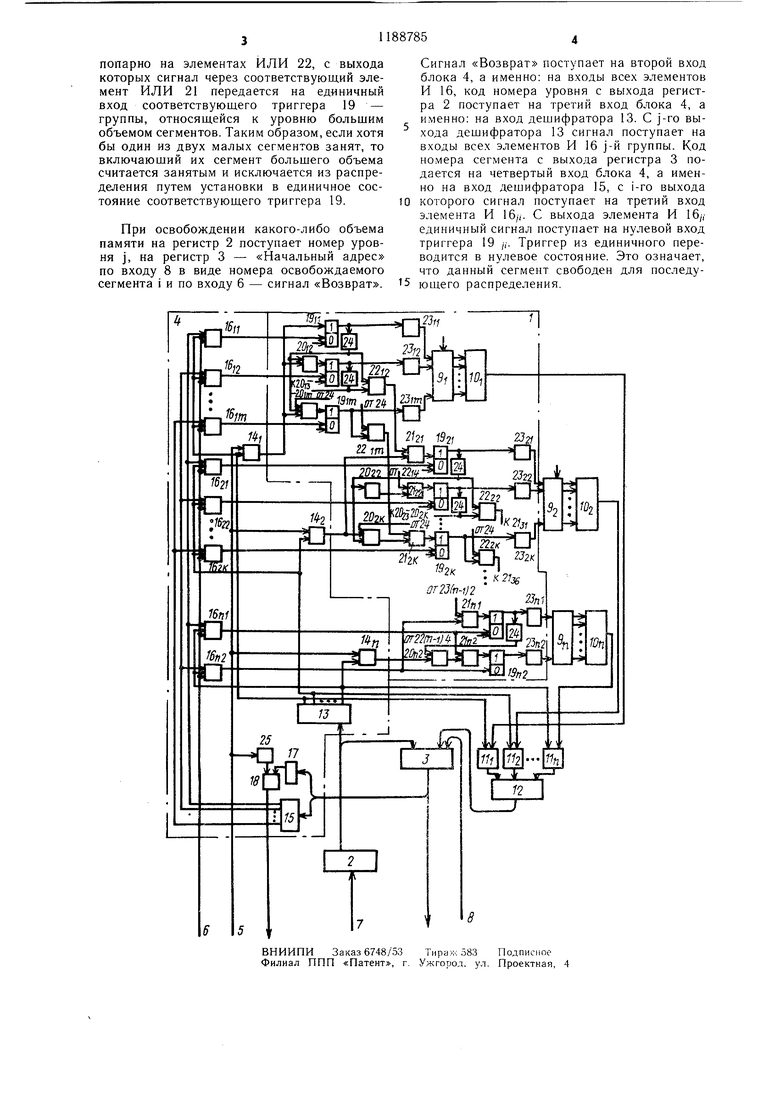

На чертеже приведена функциональная схема предложенного устройства.

Устройство содержит блок 1 памяти, первый 2 и второй 3 регистры адреса, блок 4 управления, входы «Зпрос« 5, «Возврат 6, «Номер уровня 7 и «Начальный адрес 8, группу регистров 9i, 92,..., 9„ адреса, шифраторы 10|, 102,...,10„, элементы И 11, элементы ИЛИ 12.

Блок 4 управления включает в свой состав дешифратор 13 номер уровня, группу элементов И 14i, 14,2,..., 14„, дешифратор 1.5 начального адреса, группы элементов

и 16ii, 16i2,...,16im, 1621, 1622,..., 162.., 16„|,

16„2, элемент ИЛИ-НЕ 17, элемент И 18. Вся распределяемая память объемом 2 слов разделяется на сегменты объемом 2, слов. Все сегменты одного размера составляют уровень распределяемой памяти и представлены узлами регистров, состояш,ими из триггеров 19ib 19i2,..., 19ь 1921,1922,-.., 192. 19ni, 19,i2. Блок 4 содержит также группы элементов И 20 2,---, 20im, 2022,..., 202ife,..., 20л2, группы элементов ИЛИ 2l2i, 2122,..., 212/г,...,21„|, 21„2, группы элементов ИЛИ 22i2, ..., 22i, 2222,..., 22гк,..., 22(n-t)2, 22cn-i)4 , группы формирователей 23 п, 23t2 ..., 23ия, 23г|, 23га,..., 232К,..., 23ц, 23п1 элементы 24, 25 задержки.

Число уровней распределяемой памяти ,2,...,n; число сегментов одинакового объема на одном уровне ,2,..., k,...,m.

Устройство работает следующим образом.

На блок 4 поступает сигнал «Запрос по входу 5, а на первый регистр 2 - сигнал «Номер уровня по входу 7, который соответствует объему запрашиваемой памяти. При поступлении каждого сигнала запроса регистры 9i, 92,..,9п устанавливаются в нулевое состояние. По сигналам «Запрос и «Номер уровня блок 4 вырабатывает сигнал, который поступает на вход блока памяти, соответствующий запрашиваемому уровню. Происходит это следующим образом: код j-ro уровня с первого регистра 2 поступает на третий вход блока 4, а именно на вход дешифратора 13, с j-ro выхода которого единичный сигнал поступает на первый вход элемента И 14. На второй вход элемента И 14, поступает сигнал «Запрос С выхода элемента 14,- поступает сигнал «Запрос. С выхода элемента 14/ сигнал подается на вход блока памяти, соответствующий запрашиваемому уровню.

С получением запроса от блока 4 в блоке 1 памяти определяется первый по порядку на запрашиваемом уровне свободный сегмент и его номер заносится в регистр 9j. Происходит это следующим образом. Сигнал с выхода блока 4 управления поступает на одни из входов элементов И 20,2. 20/з,..., 20jft, на другие входы которых через элемент 24 задержки поступают сигналы с единичных выходов триггеров 19/, 19,2,...,

0 19/ k-i- Если сегмент занят, то на единичном выходе соответствующего ему триггера 19 единичный сигнал, а если свободен - нулевой. Таким образом, единичный сигнал появится на выходе тех элементов И 20, номера которых соответствуют номерам сегментов, которым предшествуют все уже занятые сегменты. С выходов соответствующих элементов И 20 единичные сигналы через соответствующие элементы ИЛИ 21 поступают на единичные входы соответствующих триггеров 19. Однако изменение состояния -

переход из О в 1 - происходит лишь в том триггере, который соответствут свободному сегменту. На входе соответствующего данному триггеру формирователя 23 произойдет изменение потенциала с нулевого на единичный и на выходе формирователя сформируется импульс, который фиксируется в соответствующем разряде регистра 9/. Унитарный код с выхода регистра 9 поступает на вход шифратора lOj, где преобразуется в двоичный. С выхода щифратора lOj код

0 номера занимаемого сегмента памяти поступает на первые входы элементы И И/, на вторые входы которых поступает сигнал с выхода блока 4, а именно с j-ro выхода дешифратора 13.

С выхода элементов И 11/ через элементы ИЛИ 12 код номера занимаемого сегмента поступает на регистр 3. В разряды адреса, соответствующие номеру уровня, информация поступает с выхода регистра 2. Таким образом, в регистре 3 формируется адрес, соответствующий запрашиваемому объему памяти.

Если все сегменты запрашиваемого уровня окажутся занятыми, то ни один из триггеров 19 не изменит своего состояния, ни на

5 одном из выходов формирователей 23 не будет сформирован импульс и во всех регистрах 9 будет нулевая информация. Нулевая информация будет и в разрядах регистра 3, соответствующих номеру сегмента. Эта информация с выхода регистра 3 поступает на четвертый вход блока 4; на вход элемента ИЛИ-НЕ 17. С выхода элемента ИЛИ-НЕ 17 сигнал единичного уровня поступит на один из входов элемента И 18, На другой вход элемента И 18 через элемент 25 задержки подается сигнал «Запрос.

5 Единичный уровень на выходе элемента И 18 соответствует сигналу «Отказ.

Сигналы с единичных выходов соседних в группе триггеров 19 объединяются

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство приоритета | 1982 |

|

SU1108450A1 |

| Устройство для динамического распределения памяти | 1984 |

|

SU1243031A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для обработки прерываний | 1985 |

|

SU1282124A1 |

ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блок памяти, блок управления, первый и второй входы которого являются входами «Запрос и «Возврат устройства, третий и четвертый входы блока управления соединены с выходами первого и второго регистров адреса соответственно, вход первого регистра адреса является входом «Номер уровня устройства, первый вход второго регистра адреса соединен с выходом первого регистра адреса, второй вход является входом «Начальный адрес устройства, один из выходов блока управления подключен к входам блока памяти, отличающееся тем, что с целью повышения быстродействия устройства, в него введены группа регистров адреса, шифраторы, группы элементов И и элементы ИЛИ, причем входы регистров адреса группы соединены с выходами блока памяти, а выходы - с входами соответствуюш,их шифраторов, выходы которых подключены к первым входам элементов И групп, вторые входы которых соединены с другими выходами блока управления, выходы элементов И групп подключены к входам элементов ИЛИ, выходы которых соединены с третьим входом второго (Л регистра адреса.

| Плавкий предохранитель | 1972 |

|

SU513651A3 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 760190, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-10-30—Публикация

1984-06-14—Подача