(54) ЗАПСЙШНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Запоминающее устройство | 1979 |

|

SU809368A1 |

| Запоминающее устройство | 1979 |

|

SU809347A1 |

| Запоминающее устройство | 1979 |

|

SU809350A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Запоминающее устройство | 1979 |

|

SU826417A1 |

| Запоминающее устройство | 1979 |

|

SU773723A1 |

| Запоминающее устройство | 1981 |

|

SU982093A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU765875A1 |

| Запоминающее устройство | 1982 |

|

SU1049969A1 |

Изобретение относится к запоминаиоцим устройствам. Одно из известных запоминающих уст ройств содержит числовой блок, кбсф динатные ключи X и Y для выборки требуемой числовой линейки, формирователь ащресного тока, выходные усилители сигналов считывания со стробированием. Все блоки управляются н синхронизируются от общего блока местного управления. В этом устройстве считаниае с числового блока сигналы 1 и О отличаются только по амплитуде, но ив по фазе. Выходные сигналы 1 представляют собой илтульсы определенной амплитуды, и полярности. Запоминающее устройство этого типа имеет значитель ные преимущества перед другими тйпами по количеству используемого овррудования и потребляемой мощности Ij . Однако устройство менее помехоустойчиво и надежно из-за наличия пог мех в фазе с полезными сигналаада из-за усложнения схем числового блока и выходных усилителей. Для различения сигналов О и 1 приходится применять амплитудные селекторы, пороговые ,схемы и специальные схемы стробирования, однако это не всегда приводит к желаеким резальтатам. Особенно усложияются СХ.&ЛЛ для устройств, работамцйх в широком диапазоне механических и кли1 «1тических воздействий, и при .изменении напряжений источников пита Наиболее близким техническим решением к предлагаемому изобретению является устройство, которое содержит тсповоЛ блок, усилители считывания, блок у1фавлеЮ1Я, ключи X и Y и адресные форишрователи, а также разрядные Формирователи, регистры адреса и числа 2 . Одншсо в этом устройстве в результате наличия паразитшис индуктивност, емкостей и полувыбраниых сердечников сигиая О представляет собой . не отсутствие импульса, а импульс в фазе с полезным сигналом 1, что может привести к искажению считываемой инфсч мации-фиксации сигнала 1 вместо сигнала О. Это уменыпает помехоустойчивость и снижает надежность устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в запоминаихцее устройство, срдержащее иакопителЬу соединенный с ключами, формирователь адресного тока, усилители считывания и блок управления, одни из выходов которого подключены к управляющим входам ключей, формирователя адресного тока и усилителей считывания, введены селектор, формирователь сигналов компенсации помех, 0ЛОК местного управления, элемент задержки, блок сопряжения, усилитель сигналов компенсации помех, элемент . памяти сигналов компенсации помех, сумматоры, элементы связи и элементы И и ИЛИ, причем первый вход блока местного управления подключен к первому выходу формирователя адресного тока, второй выход которого соединен с входом селектора, выходы которого подключены соответственно к. первому входу первого элемента И и входам одних из ключей, выход блока местного управления соединен ,с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, вход элемента задержки соединен с выходом первого элемента И, а выход - с первым входом формирователя сигналов компенсации помех, второй вход которого подключен к выходу элемента ИЛИ, а выходы соединены с входами блока сопряжения, одни из выходов которого подключены к входам усилителя сигналов компенсации помех, выход которого соединен с входом элемента памяти сигналов компенсации помех, выходы которого подключены соответственно к первому входу второго элемента И и входу блока управления, другие выходы блока сопряжение через элементы связи соединены с одними из входов сумматоров, другие входы которых подключены к выходам накопителя, а выходы - к входам усилителей считывания, вторые входы блока местного управления, элементов И и управляющий вход блока сопряжения соединены с другими выходами блока управления.

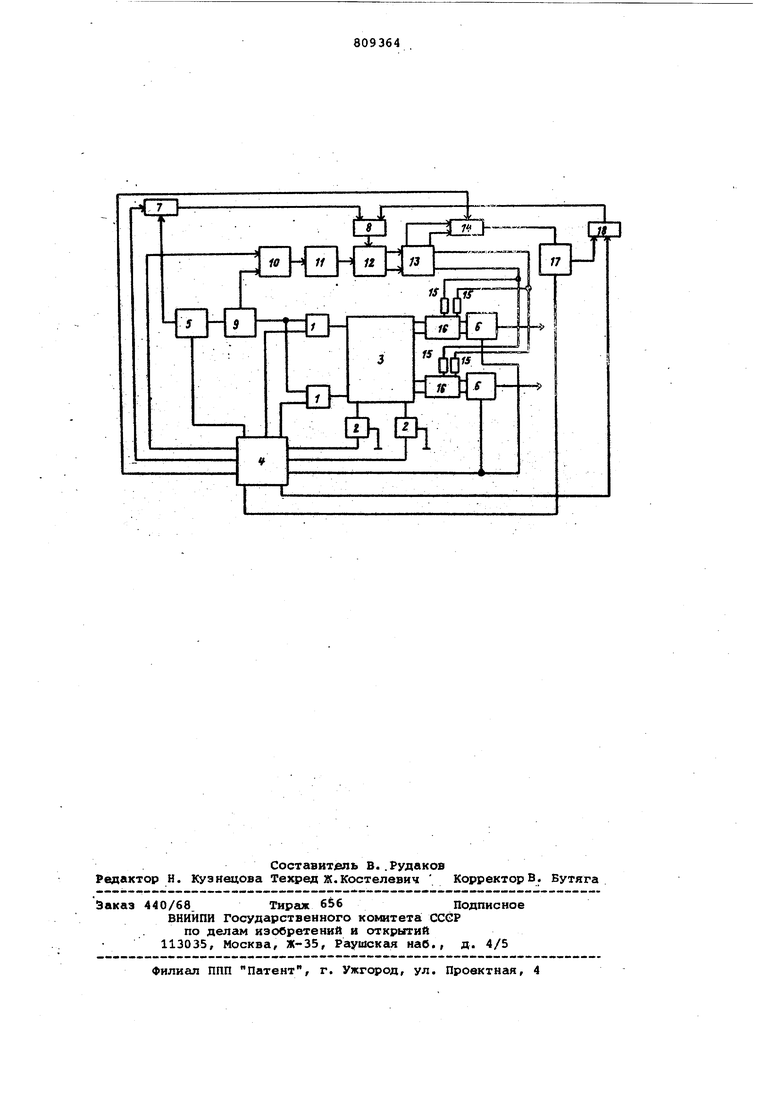

На чертеже изображена структурная схема запоминающего устройства.

Устройство содержит ключи IX, ключи 2 Y, накопитель 3, блок 4 упра ления, формирователь 5 адресного тока,усилители 6 считывания, блок 1 местного управления, элемент 8 ИЛИ, селектор 9, служащийдля выделения си1 налов компенсации помех, первый элемент 10 И, элемент 11 задержки, формирователь 12 сигналов компенсации Помех, блок 13 сопряжения, усилитель 14 сигналов компенсации помех/ элементы 15 связи, выполненные, например в виде резисторов, сумматоры 16, элемент 17 памяти сигналов компенсации помех и второй элемент 13 И.

Первый вход блока 7 подключен к первому выходу формирователя 5, вто|РОЙ выход которого соединен с входом селектора 9, выходы которого подключены соответственно к первому входу элемента 10 И и входам ключей 1. Выход блока 7 соединен с первым входом элемента 8 ИЛИ, второй вход которого подключен к выходу элемента 18 И. Вход элемента 11 задержки соединен с выходом элемента 10 И, а выход С первым входом формирователя 12, второй вход которого подключен к выходу элемента 8 ИЛИ, а выходы соединны с входами блока IS, одни из выходов которого подключены к входам усилителя 14, выход которого соединен с входом элемента 17 памяти, выходы которого подключены соответственно к первому входу элемента 18 И и входу блока. 4, другие выходы блока 13 через резисторы 15 соединены с одними из входов сумматоров 16, другие входы которых подключены к выходам накопителя 3, а выходы - к входам усилителей 6. Вторые входы блока 7, элементов И 10 и 18 и управляющий вход блока 13 соединены с выходами блока 4 .

Устройство работает следующим образом.

При считывании выбранного числа и накопителя 3 по сигналам блока 4 упрления, срабатывают один ключ IX и один ключ 2 Y. После этого формирователь 5 адресного тока выдает импульс тока спроса, который протекает по выбранной числовой линейке накопителя 3 и через некоторое время на выходах накопителя 3 появляются сигналы 1 и О выбранного числа. С селектра 9 при наличии разрешающего сигнала с блока 4 управления импульс тока опроса передается через первый элемент 10 И на элемент 11 задержки, с помощью которого можно регулировать время поступления сигнала компенсаци на сумматоры 16. Из импульса тока опроса формирователь 12 формирует сигнал компенсации, который через блок 13 сопряжения и резисторы 15 подается на входы сумматоров 16 (для каждого разряда). Сигнал компенсации в формирователе 12 может регулироватся по амплитуде и длительности с помощью блока 7 по скгналам с формирователя 5 адресных токов и блока 4 управления. На сумматорах 16 выбран-, ного числа происходит алгебраическое сложение считанных яз накопителя 3 сигналов 1 и О и сигнала компенсации, в результате чего формируются противоположные по фазе сигналы 1 и О и производится подавление имеющихся в запоминающем устройстве помех. Эти суммарные сигналы поступают на соответствующие входы усилителей 6, где они усиливаются до необходимого уровня и стробируются по сигналам с блока 4 управления. Для осуществления замкнутой обратной связи и поддержании сигнала компенсации на необходимом уровне служит цепочка блока 13 сопряжения, усилитель 14, элемент 17 памяти, второй элемент 18 И элег1ент 8 ИЛИ, формирователь 12. Наличие сигнала компенсации контролиру ется блоком 4 управления по сигналу элемента 17 памяти. Таким образом, подбирая необходимую амплитуду, длительность и время появления сигнала компенсации, можно обеспечить заданные параметры выходных сигналов 1 и О на входе усилителей воспроизведения. Использование предлагаемого запоьм нающего устройства с введенным в него селектором, блоком местно.го управления, элементом задержки, формирователем сигналов компенсации помех, бло ком сопряжения, усилителем сигналов компенсации помех, элементом .памяти, сунадаторами, элементами связи, двумя элементами Ни одним элементом ИЛИ, позволяющими подавить возникакицие в запоминающем устройстве помехи и получить фазовое различение выходных сигналов 1 и О, выгодно отличает его от существующих запоминающих устройств , так как значительно упрощаются блоки усиления и выделения сигналов, упрощаются схемы их временного стробирования и расширяются пределы работоспособности устройств. Все это значительно упрсхцает проектирование И конструирование запоминающего уст ройства, уменьшение время его отладки и повышает его надёжность. Формула изобретения Запоминающее устройство, содержа;щее накопитель, соединенный с ключами, формирователь адресного тока, ус лители считывания и блок управления, одни из выходов которого подключаю к управляющим входам ключей, формиро вателя адресного тока и усилителей считывания, отличающееся тем, что, с целью повышения надежное :ти устройства, оно содержит селектор формирователь сигналов компенсации помех, блок местного управления, элемент задержки, блок сопряжения, усилитель сигналов компенсации помех, элемент памяти сигналов компенсации помех, сумматоры, элементы связи и элементы И и ИЛИ, причем первый вход блока местного управления подключен к первому выходу формирователя,адресного тока, второй выход которого соединен с входом селектора, выходы когорого подключены соответственно к дервсму входу первого элемента И и входам одних из ключей, выход блока местного управления соединен с первым входом элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, вход элемента задержки соединен с выходом первого элемента И, а выход - с первым входом формирователя сигналов компенсации помех, второй вход которого подключен к выходу элемента ИЛИ, а выходы соединены с входа ш блока сопряжения, одни из выходов которого подключены к входам усилителя сигнсшов ктэмпеисации помех, выход которого соединен с входом элемента памяти сигналов компенсации помех, выходы которого подключены соответственно к первому входу второго элемента И и входу блока управления, другие выходы блока сопряжения через элементы связи соединены t одними из входов сумматоров, другие входы которых подключены к выходам накопителя, а выходы - к входам усилителей считывания, вторые входы блока местного управления, элементов И и управляющий вход блока сопряжения соединены с другими выходами блока уп равления. Источники информации, принятые во внимание при экспертизе 1. Брик Е.А. Техника постоянных запокшнающих устройств. М., Советское радио, 1973, с. 51-62. 2.IiterHH А.Г. и Дерюгин А.А. Цифро вые вычислительные машины. М., Энер гия, 1975, с. 33-37 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-06-04—Подача