1

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройстве содержащее генератор, выход которого соединен с первичной обмоткой трансформатора, вторичная обмотка которого одним концом через диод подключена к базе транзистора, а другим концом к эмиттеру транзистора, между базой и эмиттером которого включен резистор 1 ,

Недостатке этого устройства является ненадежность его работы в условиях интенсивных помех, действующих по цеци питания.

Наиболее близким по технической сущности к предлагаемому является запоминающее устройство, содержащее накопитель, формирователи разрядных токов, дешифратор адреса, формирователи адресных токов, регистр числа и усилители воспроизведения, причем эыходы дешифратора гщреса подключены ко входам формирователей адресных токов, выходы усилителей воспроизведения соединены со входами регистра числа, выходы которого подключены ко входам формирователей разрядных токов, выходы ко.торых и выходы формирователей адресных токов.соединены с соответствующими входами накопите.г1Я 2.

Недостатке) этого устройства является невозможность полного подавления квазидетерминированных синфазных и дифференциальных, а также случайных помех, что снижает надежность устройства.

Цель изобретения - повышение надежности устройства за счет увеличения его помехозащищенности.

Поставленная цель достигается тем, что устройство содержит элементы задержки две группы элементов ИЛИ, генератор импульсов, эталонный запоминающий элемент и корреляторы, причем входы элементов Задержки подключены к выходам дешифратора адреса, а выходы - ко

входам элементов ИЛИ первой группы, входы элементов ИЛИ второй группы соединены с выходами элементов первой группы, а выходы - со входом генератора импульсов, выход которого подключен ко входу эталонного запоминающего элемента, одни входы корреляторов подключены к выходу эталонного запоминающего элемента,

30 другие входы - к выходам накопитея, а выходы - ко входам усилитеей воспроизведения.

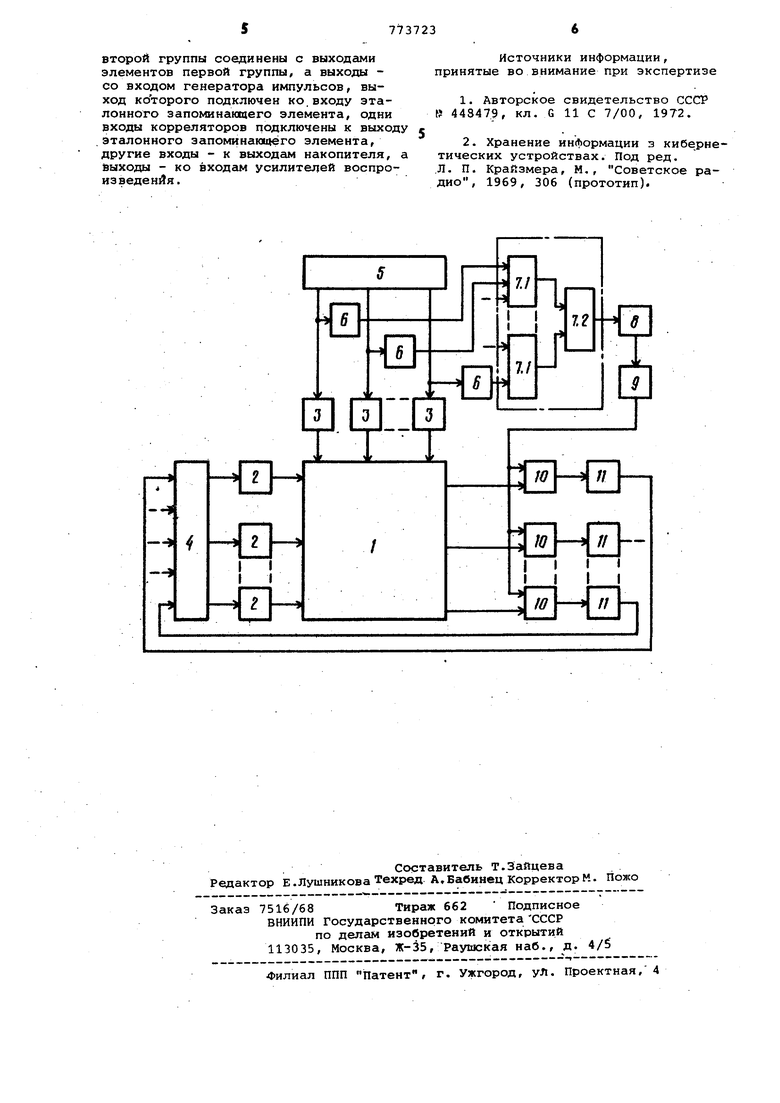

На чертеже изображена блок-схема стройства.

Устройство содержит накопитель i; ормирователи разрядных токов 2, формирователи адресных токов 3, регистр числа 4, дешифратор адреса 5, элементы 6 задержки первую 7,1 и вторую 7.2 группы элементов ИЛИ, генератор импульсов 8, эталонный запоминающий элемент 9, коррелятоы 10 и усилители воспроизведения 11.

Выходы дешифратора адреса 5 подлючены ко входам формирователей адресных токов 3. Выходы усилителей воспроизведения 11 соединены со входами регистра числа 4 , выходы которого подключены ко входам формирователей разрядных токов 2. Выходы формирователей разрядных токов 2 и формирователей адресных токов 3 соединены с соответствующими входами накопителя 1. Входы элементов 6 задержки подключены к выходам дешифратора адреса 5, а выходы - ко входам элементов ИЛИ первой группы 7.1. Входы элементов ИЛИ второй группы 7.2 соединены с выходами элементов ИЛИ первой группы 7.1, а выходы - со входом генератора импульсов 8, выход которого подключен ко входу эталонного запоминающего элемента 9. Одни входы корреляторов 10 соединены с выходом эталонного запоминающего элемента 9, другие входы - с выходами накопителя 1, а выходы со входами усилителей воспроизведения 11.

Устройство работает следуклциМ образом.

При счить1вании числа по сигналу с дешифратора адреса 5 срабатывает соответствукадий формирователь адресных токов 3 и сигналы чтения вместе с помехами поступают по разрядно-считывающим линиям на выход накопителя 1. Причем сигналы чтения, соответствующие коду числа, из-за задержки в разрядно-считывающих линиях накопителя 1 появляются на выходе накопителя 1 в разное время относительно момента времени считывания в зависимости от адреса числа. По тому же сигналу с дешифратора адреса 5 запускается соответствующий элемент 6 задержки, задержка сигнала в которой равна задержке сигн}илрв чтения по этому адресу в накопителе 1. Сигнал с элемента задержки 6 поступает на вход элементов ИЛН 7.1. С выхода элемента ИЛИ 7.2 сигнал поступает на вход генератора импульсов 8 и запускает его. Сигнал считывания с генератора импульсов 8 подается на эталонный запоминающий элемент 9, с выхода которого эталонный сигнал подается на входы корреляторов 10, на другие входы которых в это же время поступают сигналы чтения с выходов накопителя 1. С выходов корреляторов 10 сигналы о воспроизведении поступают поразрядно на соответствующие усилители воспроизведения 11 и после усиления подаются на входы регистра числа 4.

ИнФомарционная надежность и помехозащищенность в предлагаемом запоминающем устройстве повышена, во-первых, за счет организации коррелирования сигналов чтения, смешанных с помехами, с эталонным сигналом, лишенньви помех,так как эталонный элемент 9 не связан с накопителем 1 ни по разрядным, ни по адресным линиям, а во-вторых, за счет того, что сигналы приходят на входы корреляторов 10 в одно и то же время, независимо от адреса числа (задержка этих сигналов относительно Друг друга в случае необходимости для корреляции может быть введена путем изменения параметров элементов б задержки).Элементы 6 задержки обеспечивают синхронное поступление сигнала чтения, смешанного с псмехой, и эталонного сигнала или обеспечивают наперед заданное смещение (постоянное) вне зависимости от изменения адреса числа.

Технико-экономическое преимущество предложенного устройства заключается в том, что воспроизведение считанной из накопителя информации близко к оптимальному вследствие применения эталонного запоминающего элемента и корреляторов, за . счет чего.улучшена помехозащищенность, т.е. повышена надежность устройства.

Формула изобретения

Запс 4инаквдее устройство,содержащее накопитель, формирователи разрядных токов, дешифратор адреса, формирователи адресных токов, регистр числа и усилители воспроизведения, причем выходы доиифрат.ора адреса подключены ко входам формирователей адресных токов, выходы усилителей воспроизведения соединены со входгиии регистра числа, выходы которого подключены ко входам формирователей адресных токов соединены с соответствующими входг ми накопителя, о т л ич ающ ее ся тем, что, с целью повышения надежности устрой ства, оно содержит элементы задержки, две группы элементов ИЛИ, генератор импульсов, эталонный запоминакяций элемент и коррелятО1«, прнгчем входы элементов задержки подключены к выходам дешифратора адреса, а выходы - ко входам элементов ИЛИ первой группы, входы элементов ИЛИ

второй группы соединены с выходами элементов первой группы, а выходы со входом генератора импульсов, выход которого подключен ко. входу эталонного запоминающего элемента, одни входы корреляторов подключены к выходу .эталонного запоминающего элемента, другие входы - к выходам накопителя, а йыходы - ко входам усилителей воспроизведения.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 443479, кл. G 11 С 7/00, 1972.

2.Хранение информации з кибернетических устройствах. Под ред.

.Л. П. Крайзмера, М., Советское радио, 1969, 306 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1978 |

|

SU781971A1 |

| Запоминающее устройство | 1983 |

|

SU1117709A1 |

| Запоминающее устройство | 1980 |

|

SU873275A1 |

| Полупостоянное запоминающее устройство | 1980 |

|

SU900314A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1100640A1 |

| Полупостоянное запоминающее устройство | 1978 |

|

SU765875A1 |

| "Запоминающее устройство | 1979 |

|

SU809369A1 |

| Устройство управления для доменной памяти | 1988 |

|

SU1566409A1 |

| Запоминающее устройство | 1979 |

|

SU824304A1 |

| Запоминающее устройство | 1981 |

|

SU982093A1 |

I

J

I I

10

II

11

//

10

Авторы

Даты

1980-10-23—Публикация

1979-02-01—Подача