- 1 . Изобретение относится к запбминающим устройствам и может быть использовано в автоматике и вычислительной технике, в частности, для контроля запоминающих устройств (ЗУ Известны методы повышения достоверности хранения информации в ЗУ, с введением аппаратурной и временной избыточности. Аппаратурная избыточность реализуется путем использования кодов, устраняющих и обнаруживаю щих ошибки, введением специальной контрольной аппаратуры, резервированием, обходом отказавших ячеек р . Однако применение указанньгх методов или их комбинаций не обеспечивает корректировку информации постоянных запоминающих устройств (ПЗУ) по любому адресу с полной заменой содер жания всего слова в ПЗУ в реальном масштабе времени с приемлемой избыточностью. Наиболее близким к предлагаемому изобретению по технической сущности является устройство, которое содержит первый и второй блоки памяти, логический блок, коммутатор, корректирующий блок памяти, причем входы второго блока памяти подключены соответственно к адресным шинам первой группы, управляющей шине и шинам ввода, выходы коммутатора соединены соответственно с выходами второго блока памяти и адресными шинами второй rpynnj i адресов, выходы коммутатора подключены к первым входам логического блока и первого блока памяти, ко вторьм входам логического блока подключены информационные шины, к третьим - выходы первого блока памяти, остальные входы первого блока памяти подключены соответственно к адресным шинам третьей группы, шинам ввода и управляющей тине 2j. Недостатком этого устройства является применение блоков памяти и больших объемов по сравнению с объемом корректируемой информации.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что в устройство для коррекции информации в блоках постоянной памятц, содержащее первый блок памяти, первый вход которого соединен с шиной ввода информации, второй и третий входы первого блока памяти подключены соответственно к первой адресной шине и шике управления, коммутатор, один из входов которого соединен со второй адресной шиной, другой вход коммутатора подсоединен к выходу второго блока памяти, один из входов которого соединен с третьей адресной шиной, другой вход второго блока памяти подключен к шине управления и к первому выходу устройства, блок элементов И-ИЛИ-НЕ, первый вход которого соединен с выходом первого блока памяти, второй вход блока элементов И-ШТИ-НЕ подключен к информационной шине, а выход - ко второму выходу устройства, введены шифратор и сумматор, выход которого подключен -к четвертому входу первого блока памяти, входы сумматора подсоединены соответственно к первому выходу шифратора и первому вьсходу коммутатора, второй выход шифратора

соединен с третьим входом блока элементов И-ИЛИ-НЕ, первый вход шифратора подключен ко второму выходу коммутатора, а второй вход шифратора соединен с четвертой адресной шиной.

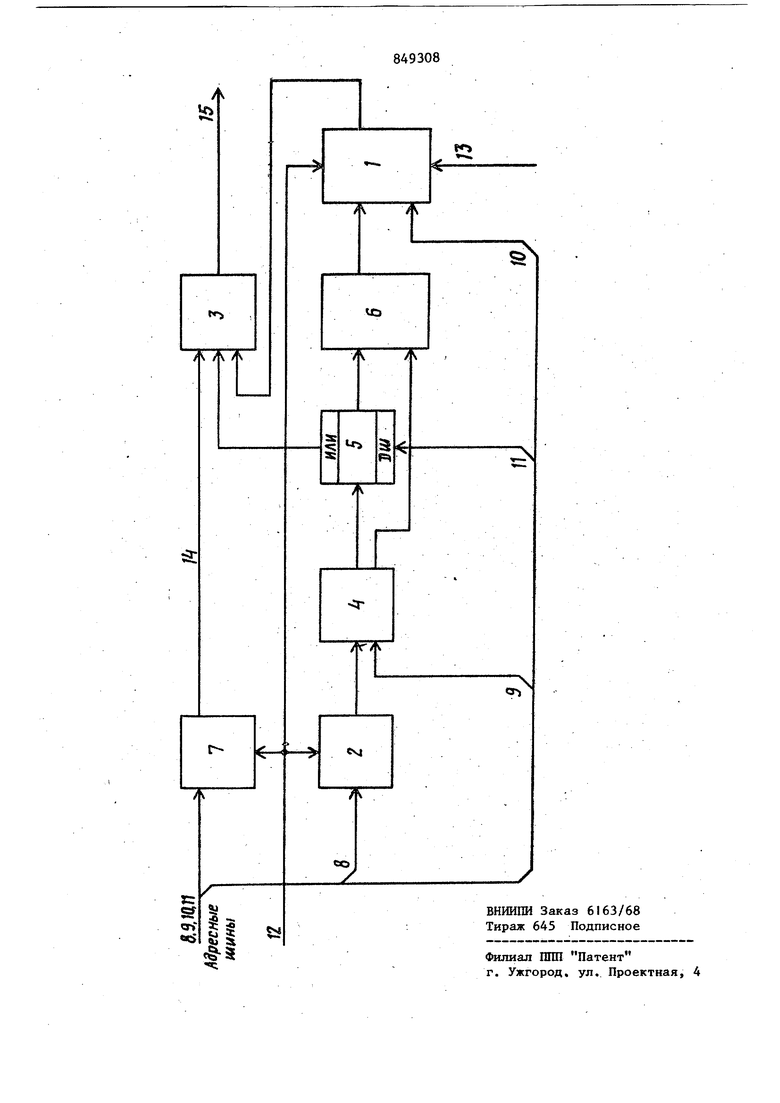

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит блоки 1 и 2 памяти, блок элементов И-ИЛИ-НЕ 3, коммутатор 4, шифратор 5, сумматор 6 корректируемый блок 7 постоянной памяти, адресные шины 8-11, шина 12 управления, шина 13 ввода информации информационная шина 14 и выход 15 усройства.

Устройство работает следующим образом.

Работу устройства рассмотрим на примере коррекции блока постоянной памяти 2 36-ти разрядных слов при необходимости корректировать до 256 массивов, состоящих каждый из 4-х ,слов, при этом блоки 1 и 2 памяти усройства должны иметь объем 2 36-ти разрядных слов.

Второй блок 2 памяти служит для запоминания адресов корректируемых массивов. .

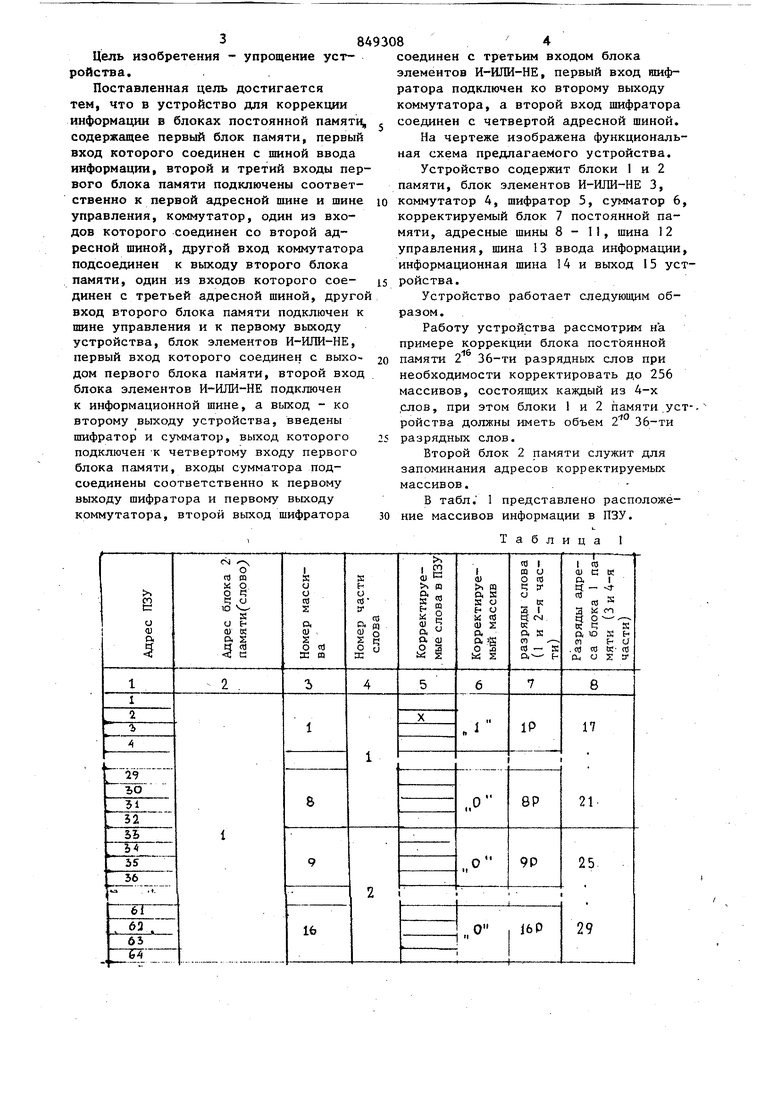

В табл. 1 представлено расположение массивов информации в ПЗУ.

Таблиц

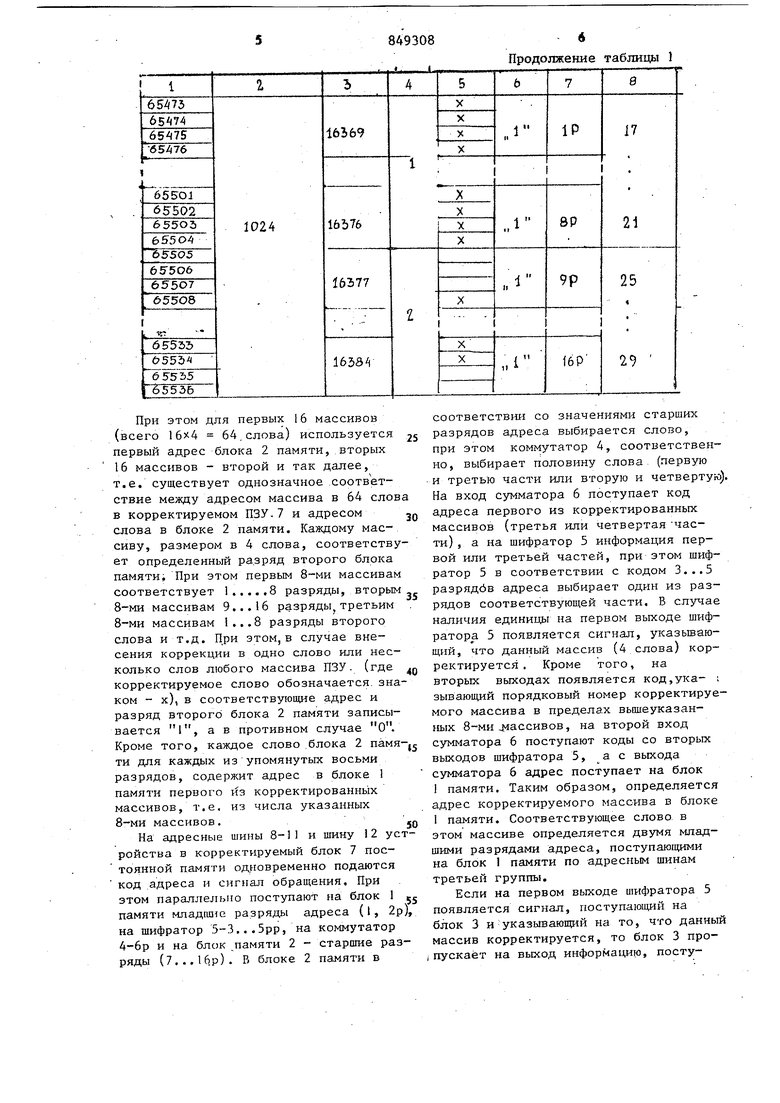

Продолжение таблицы 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией информации | 1986 |

|

SU1392596A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Устройство для коррекции информации в блоке постоянной памяти | 1978 |

|

SU752501A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Запоминающее устройство с коррекцией программы | 1981 |

|

SU963108A2 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для коррекции информации в блоках постоянной памяти | 1988 |

|

SU1543460A1 |

При этом для первых 16 массивов (всего 16x4 64,слова) используется 2S первый адрес блока 2 памяти, вторых 16 массивов - второй и так далее, т.е. существует однозначное соответствие между адресом массива в 64 слова в корректируемом ПЗУ.7 и адресом JQ слова в блоке 2 памяти. Каждому массиву, размером в 4 слова, соответствует определенный разряд второго блока памяти; При этом первым 8-ми массивам

соответствует 18 разряды, вторым

8-ми массивам 9...16 разряды.третьим 8-ми массивам 1.,.8 разряды второго слова и т.д. Цри этом,в случае внесения коррекции в одно слово или несколько слов любого массива ПЗУ. (где Q корректируемое слово обозначается, знаком - х), в соответствующие адрес и разряд второго блока 2 памяти записывается I, а в противном случае О. Кроме того, каждое слово блока 2 памя-j ти для каждых из упомянутых восьми разрядов, содержит адрес в блоке 1 памяти первого из корректированных массивов, т.е. из числа указанных 8-ми массивов.JQ

На адресные шины 8-11 и шину 12 устройства в корректируемый блок 7 постоянной памяти одновременно подаются код адреса и сигнал обращения. При этом параллельно поступают на блок 1 jj памяти млад1Ш1е разряды адреса (1, 2р), на шифратор 5-3...5рр, на коммутатор 4-6р и на блок памяти 2 - старшие разряды (7...16.р). В блоке 2 памяти в

соответствии со значениями старших разрядов адреса выбирается слово, при этом коммутатор 4, соответственно, выбирает половину слова (первую и третью части или вторую и четвертую). На вход сумматора 6 поступает код адреса первого из корректированных массивов (третья или четвертая -части) , а на шифратор 5 информация первой или третьей частей, при этом шифратор 5 в соответствии с кодом 3...5 разрядов адреса выбирает один из разрядов соответствующей части. В случае наличия единицы на перв.ом выходе шифратора 5 появляется сигнал, указьшающий, что данный массив (4 слова) корректируется. Кроме того, на вторых выходах появляется код,ука- i зывашщий порядковый номер корректируемого массива в пределах вышеуказанных 8-ми ассивов, на второй вход сумматора 6 поступают коды со вторых выходов шифратора 5, а с выхода сумматора 6 адрес поступает на блок 1 памяти. Таким образом, определяется адрес корректируемого массива в блоке 1 памяти. Соответствующее слово в этом массиве определяется двумя младими разрядами адреса, поступающими на блок 1 памяти по адресным шинам третьей группы.

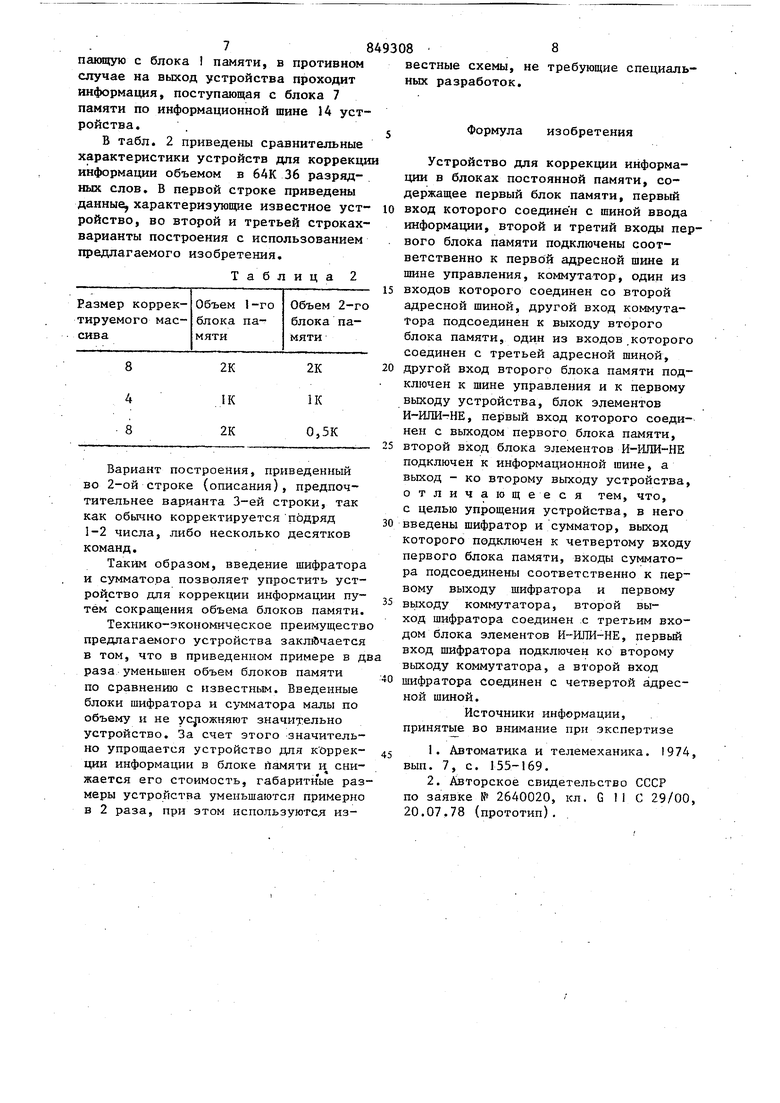

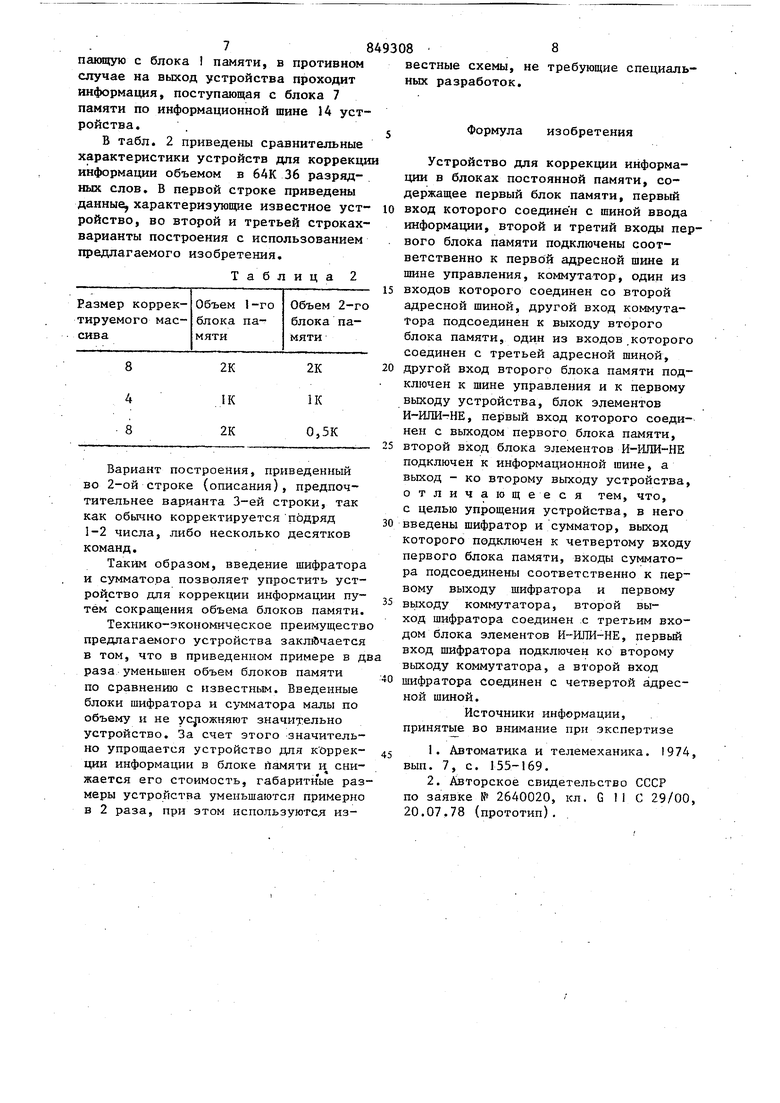

Если на первом выходе шифратора 5 появляется сигнал, поступающий на лок 3 и указывающий на то, что данный ассив корректируется, то блок 3 пропускает на выход информацию, поступакицую с блока 1 памяти, в противном случае на выход устройства проходит информация, поступающая с блока 7 памяти по информационной шине 14 устройства. В табл. 2 приведены сравнительные характеристики устройств для коррекци информации объемом в 64К 36 разрядных слов. В первой строке приведены данные характеризующие известное устройство, во второй и третьей строкахварианты построения с использованием предлагаемого изобретения. Таблица 2 Вариант построения, приведенный во 2-ой строке (описания), предпочтительнее варианта 3-ей строки, так как обычно корректируется подряд 1-2 числа, либо несколько десятков команд. Таким образом, введение шифратора и сумматора позволяет упростить устрой ство для коррекции информации путём сокращения объема блоков памяти. Технико-экономическое преимуществ предлагаемого устройства заключается в том, что в приведенном примере в д раза уменьшен объем блоков памяти по сравнению с известным. Введенные блоки шифратора и сумматора малы по объему и не ус гожняют значительно устройство. За счет этого значительно упрощается устройство для кОррекции информации в блоке йамяти и снижается его стоимость, габаритные раз меры устройства уменьшаются примерно в 2 раза, при этом используются известные схемы, не требующие специальных разработок. Формула изобретения Устройство для коррекции информации в блоках постоянной памяти, содержащее первый блок памяти, первый вход которого соединён с шиной ввода информации, второй и третий входы первого блока памяти подключены соответственно к первой адресной шине и шине управления, коммутатор, один из входов которого соединен со второй адресной шиной, другой вход коммутатора подсоединен к выходу второго блока памяти, один из входов.которого соединен с третьей адресной шиной, другой вход второго блока памяти подключен к шине управления и к первому выходу устройства, блок элементов И-ШШг-НЕ, первый вход которого соединен с выходом первого блока памяти, второй вход блока элементов И-ИЛИ-НЕ подключен к информационной шине, а выход - ко второму выходу устройства, отличающееся тем, что, с целью упрощения устройства, в него введены шифратор и сумматор, выход которого подключен к четвертому входу первого блока памяти, входы сумматора подсоединены соответственно к первому выходу шифратора и первому выходу коммутатора, второй выход шифратора соединен с третьим входом блока элементов И-ИЛИ-НЕ, первый вход шифратора подключен ко второму выходу коммутатора, а второй вход шифратора соединен с четвертой адресной шиной. Источники информации, принятые во внимание при экспертизе 1.Автоматика и телемеханика. 1974, вып. 7, с. 155-169. 2.Авторское свидетельство СССР по заявке № 2640020, кл. G 11 С 29/00, 20.07.78 (прототип).

Авторы

Даты

1981-07-23—Публикация

1979-06-04—Подача