1

Изобретение относится к запоминающим устройствам, в частности к запоминающим устройствам, реализовным на БИС и управляемым вычислительными устройствами (ЭВМ).

Цель изобретения - повьппение быстродействия устройства.

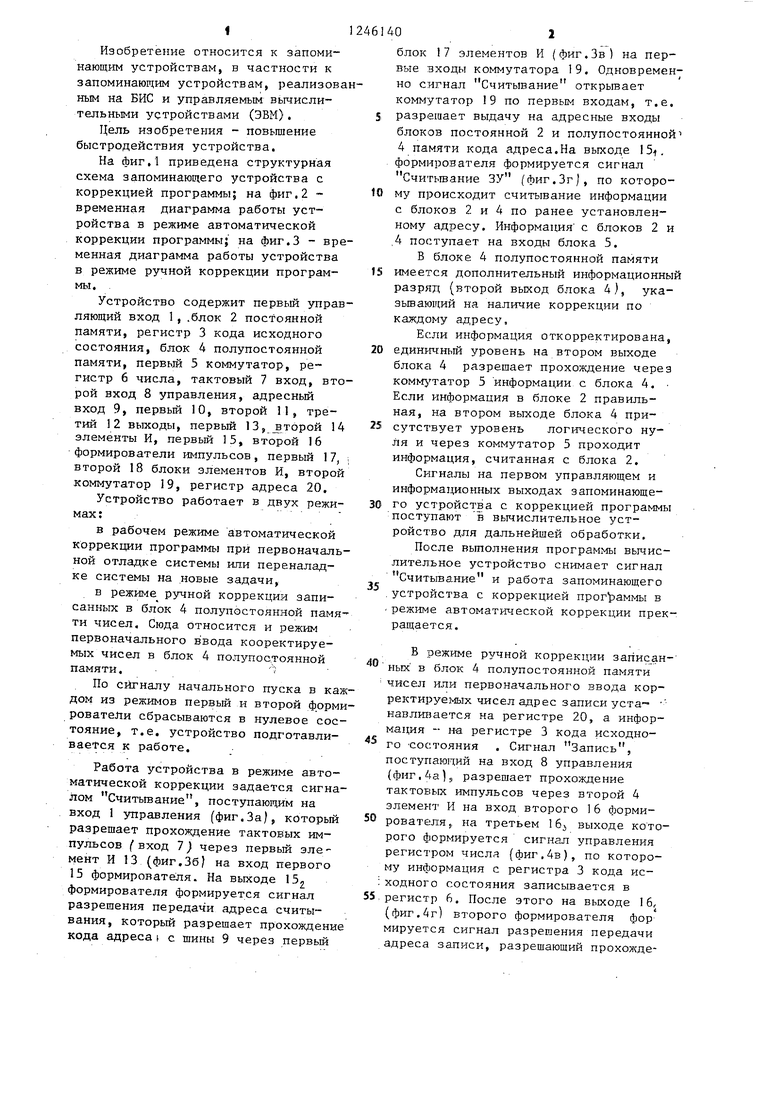

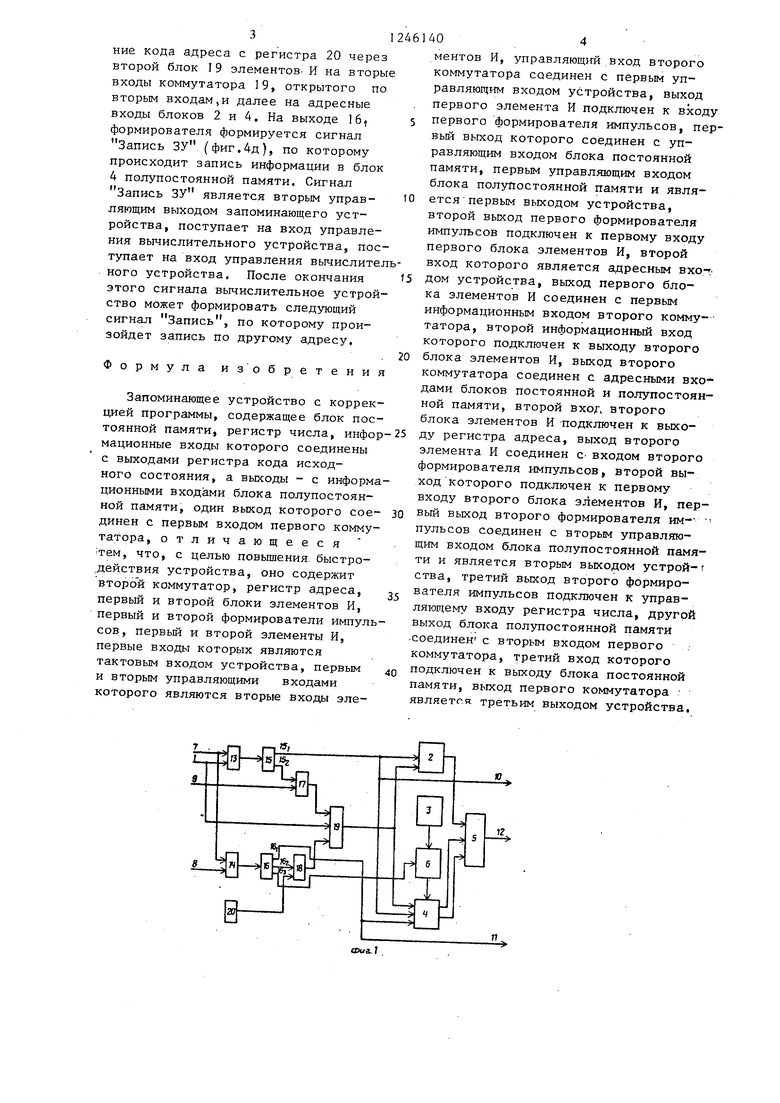

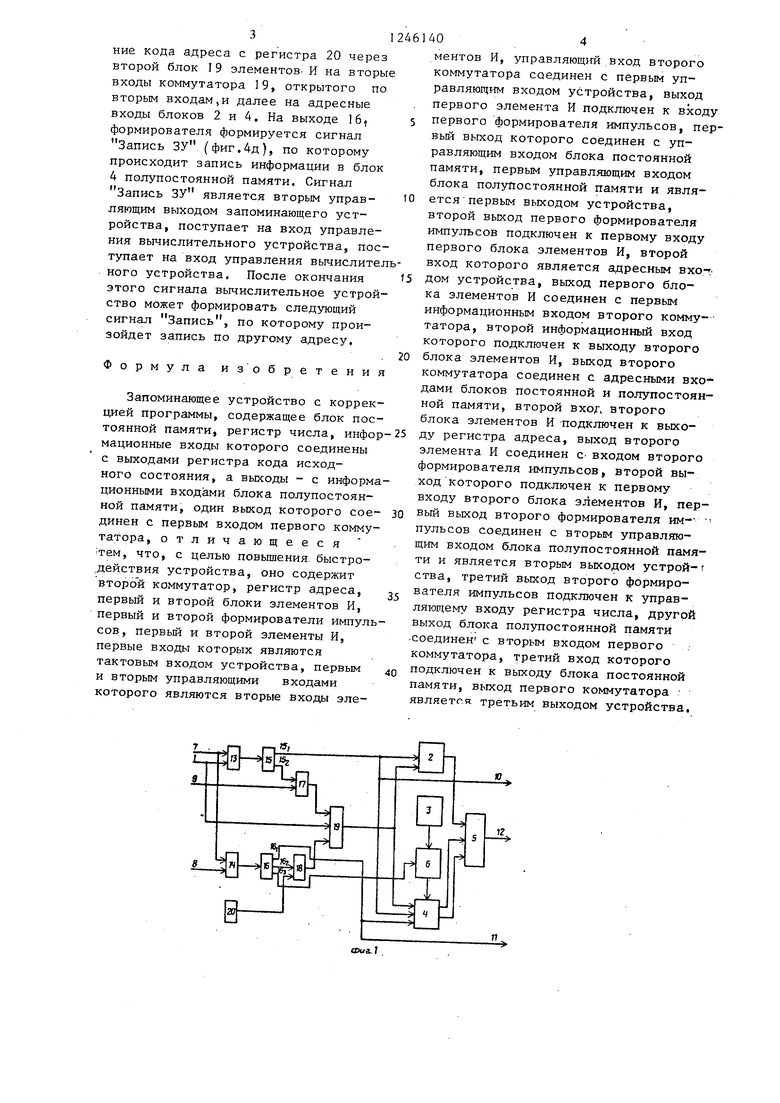

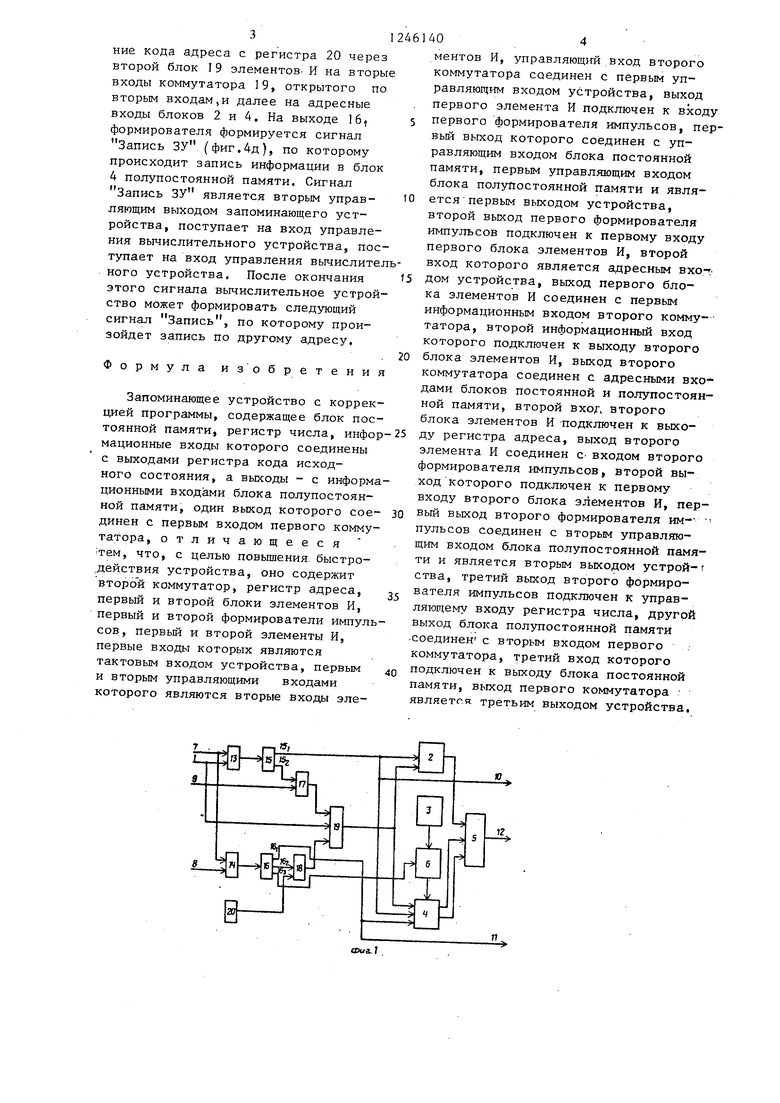

На фиг.1 приведена структурная схема запоминающего устройства с коррекцией программы; на фиг.2 временная диаграмма работы устройства в режиме автоматической коррекции программы; на фиг.З - врменная диаграмма работы устройства в режиме ручной коррекции программы.

Устройство содержит первый упраляющий вход 1, .блок 2 постоянной памяти, регистр 3 кода исходного состояния, блок 4 полупостоянной памяти, первь й 5 коммутатор, ре

гистр 6 числа, тактовый 7 вход, второй вход 8 управления, адресный вход 9, первьш 10, второй 11, третий 12 выходы, первый 13, торой 14 элементы И, первьй 15, второй 16 формирователи импульсов, первый 17, второй 18 блоки элементов И, второй коммутатор 19, регистр адреса 20.

Устройство работает в двух режимах:

в рабочем режиме автоматической коррекции программы при первоначальной отладке системы или переналадке системы на новые задачи,

в режиме ручной коррекции записанных в блок 4 полупостоянной памяти чисел. Сюда относится и режим первоначального в вода кооректируе- мых чисел в блок 4 полупостоянной памяти.

По сигналу начального пуска в каждом из режимов первый и второй формирователи сбрасываются в нулевое состояние, т.е. устройство подготавли- вается к работе.

Работа устройства в режиме автоматической коррекции задается сигналом Считьгеание, поступающим на вход 1 управления (фиг.3а|, который разрешает прохождение тактовых импульсов (вход 1) через первьй эле- мент И 13 (фиг,36} на вход первого 15 формирователя. На выходе 152 формирователя формируется сигнал разрешения передачи адреса считывания, который разрешает прохождение кода адреса t с шины 9 через первый

25

30

35

2461402

блок 17 элементов И (фиг.Зв) на первые входы коммутатора 19. Одновремену но сигнал Считывание открьшает коммутатор 19 по первым входам, т.е.

5 разрешает выдачу на адресные входы блоков постоянной 2 и полупостоянной 4 памяти кода адреса.На выходе 15. формирователя формируется сигнал Считьшание ЗУ (фиг.Зг), по которо10 му происходит считывание информации с блоков 2 и 4 по ранее установленному адресу. Информация с блоков 2 и ,4 поступает на входы блока 5.

В блоке 4 полупостоянной памяти

15 имеется дополнительный информационный разряд (второй выход блока 4), ука- зьшающий на наличие коррекции по каждому адресу.

Если информация откорректирована,

20 единичный уровень на втором выходе блока 4 разрешает прохождение через комментатор 5 информации с блока 4. Если информация в блоке 2 правильная, на втором выходе блока 4 присутствует уровень логического нуля и через коммутатор 5 проходит информация, считанная с блока 2.

Сигналы на первом управляющем и информационных выходах запоминающего устройства с коррекцией программы поступают в вьиислительное устройство для дальнейшей обработки.

После выполнения программы вычислительное устройство снимает сигнал Считьшание и работа запоминающего устройства с коррекцией прог раммы в режиме автоматической коррекции прекращается.

В режиме ручной коррекции записан- ных в блок 4 полупостоянной памяти чисел или первоначального ввода кор- ректируе у1ых чисел адрес записи уста- навливается на регистре 20, а информация - на регистре 3 кода исходного сос;тояния . Сигнал Запись, поступающий на вход 8 управления (фиг,4а).| разрешает прохождение тактовых импульсов через второй 4 элемент И на вход второго 16 формирователя, на третьем 16 выходе которого формируется сигнал управления регистром числа (фиг,4в), по которому информация с регистра 3 кода исходного состояния записывается в регистр 6. После этого на выходе 16, (фиг.4г) второго формирователя фор мируется сигнал разрепзения передачи адреса записи, разрешающий прохожде31

ние кода адреса с регистра 20 через второй блок 19 элементов- И на вторые входы коммутатора 19, открытого по вторым входам,и далее на адресные входы блоков 2 и 4, На выходе 16 формирователя формируется сигнал Запись ЗУ (фиг.4д), по которому происходит запись информации в блок 4 полупостоянной памяти. Сигнал Запись ЗУ является вторым управ- ляющим выходом запоминающего устройства, поступает на вход управления вычислительного устройства, поступает на вход управления вычислителного устройства. После окончания этого сигнала вычислительное устройство может формировать следующий сигнал Запись, по которому произойдет запись по другому адресу.

. Формула из обретения

Запоминающее устройство с коррекцией программы, содержащее блок постоянной памяти, регистр числа, инфор мационные входы которого соединены с выходами регистра кода исходного состояния, а выходы - с информационными входами блока полупостоянной памяти, один выход которого сое- динен с первым входом первого коммутатора, отличающееся Тем, что, с целью повышения, быстродействия устройства, оно содержит второ й коммутатор, регистр адреса, первый и второй блоки элементов И, первый и второй формирователи импульсов, первьй и второй элементы И, первые входы которых являются тактовым входом устройства, первым и вторым управляющими входами которого являются вторые входы эле404

ментов И, управляющий вход второго коммутатора соединен с первым управляющим входом устройства, выход первого элемента И подключен к входу первого формирователя импульсов, первый выход которого соединен с управляющим входом блока постоянной памяти, первым управляющим входом блока полупостоянной памяти и является первым выходом устройства, второй выход первого формирователя импульсов подключен к первому входу первого блока элементов И, второй вход которого является адресным вхо-Г дом устройства, выход первого блока элементов И соединен с первым информационным входом второго коммутатора, второй информационный вход которого подключен к выходу второго блока элементов И, выход второго коммутатора соединен с адресными входами блоков постоянной и полупостоянной памяти, второй вход второго блока элементов И подключен к выходу регистра адреса, выход второго элемента И соединен с- входом второго формирователя импульсов, второй выход которого подключен к первому входу второго блока элементов И, первый выход второго формирователя им- пульсов соединен с вторым управляющим входом блока полупостоянной памяти и является вторым выходом устройства, третий выход второго формирователя импульсов подключен к управ- ляюР1ему входу регистра числа, другой выход блока полупостоянной памяти .соединен с вторым входом первого коммутатора, третий вход которого подключен к выходу блока постоянной памяти, выход первого коммутатора является третьим выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией программы | 1986 |

|

SU1347097A1 |

| Запоминающее устройство с коррекцией информации | 1984 |

|

SU1259339A1 |

| Запоминающее устройство с коррекцией программы | 1981 |

|

SU963108A2 |

| Запоминающее устройство | 1979 |

|

SU826423A1 |

| Устройство для коррекции программ | 1983 |

|

SU1141416A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1479954A1 |

| Устройство для контроля памяти | 1984 |

|

SU1215138A1 |

Изобретение относится к запоминающим устройствам, в частности к запоминающим устройствам, реализованным на БИС и управляемым вычислительными устройствами. Цель иэобрете ния - повьпиение быстродействия уст-. ройства. Устройство содержит блок :постоянной памяти, блок полупостоянной памяти, коммутаторы, регистр числа, элементы И, блоки элементов И, формирователи импульсов, регистр адреса, входы и выходы устройства. Устройство работает в ,двух режимах: в рабочем режиме автоматической коррекции программы при первоначаль ной отладке системы или переналадке системы на новые задачи;.в режиме ручной коррекции записанных в блок полупостоянной памяти чисел. Сюда относится и режим первоначального ввода корректируемых чисел в блок полупостоянной памяти. 3 ил. с (Л

а. 5.

в- г

rZDC

DCZTZDC.а

Фмг.2

,™«П1

.J

Фиг.Ъ

| Автоматика и телемеханика, 1974, № 7, с.155-171 | |||

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-07-23—Публикация

1984-06-29—Подача