(54) ВЫЧИСЛИТЕЛЬНЫЙ УЗЕЛ ЦИФРОВОЙ СЕТОЧНОЙ МОДЕЛИ для РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ

1

Изобретение относится к вычислительной технике и может быть использовано при построении устройств для решения задач математической физики, описываемых уравнениями в частных производных.

Известен вычислительный узел цифровой сетки, содержащий многовходовый сумматор, регистр сдвига, элемент И и группу элементов И р.

Недостатком узла является то, что он не может быть непосредственно применен для решения дифференциальных уравнений с переменными коэффициентами .

Наиболее близок к предлагаемому по технической су1,ности и достигаемому эффекту вычислительный узел цифровой сетки, который содержит запоминающее устройство, коммутаторы, сумматор, регистр сдвига, регистр коэффициента, элемент И и группу элементов И, причем выходы группы элементов И являются группой выходов

.узла, последовательный выход регистра сдвига соединен со входом элемента И, выход которого является выходом узла, вход регистра коэффициента является информационным входом узла, адресный вход запоминающего устройства соединен с выходом первого коммутатора, первая и вторая группы входов которого являются соответственно nepBoJ и второй груп10пами входов узла, выход запоминающего устройства соединен с первым входом сумматора,первый и второй входы второго коммутатора подключены соответственно к выходу сумматора и

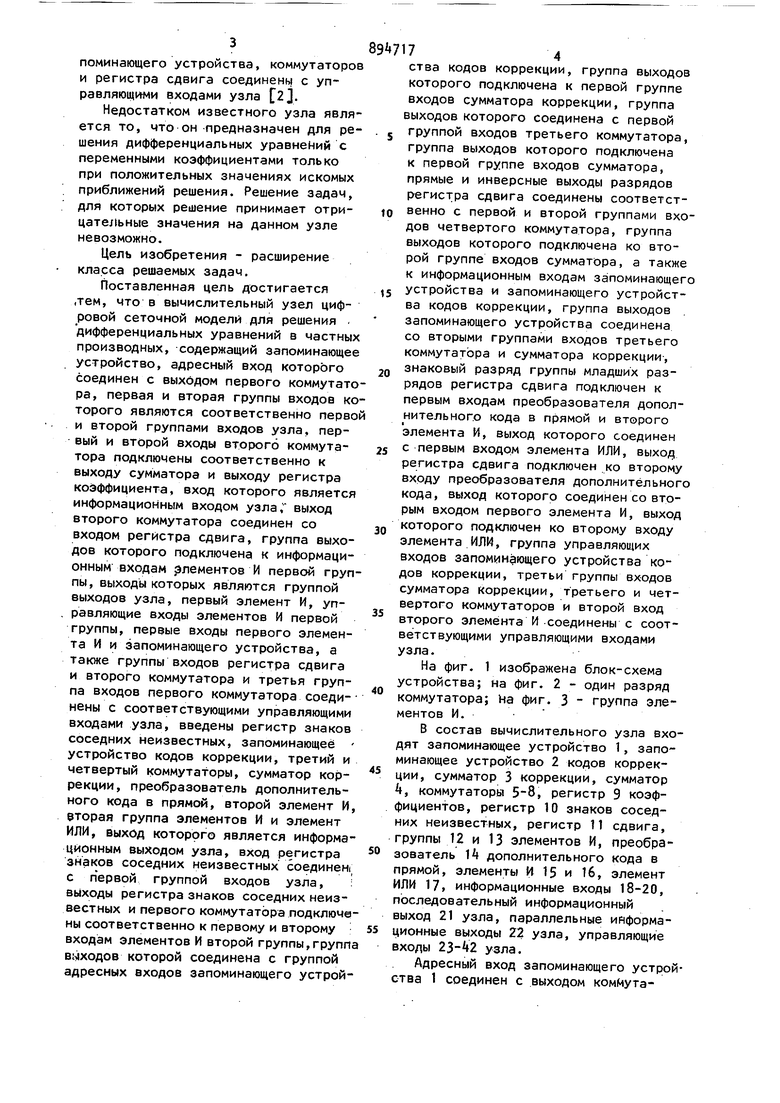

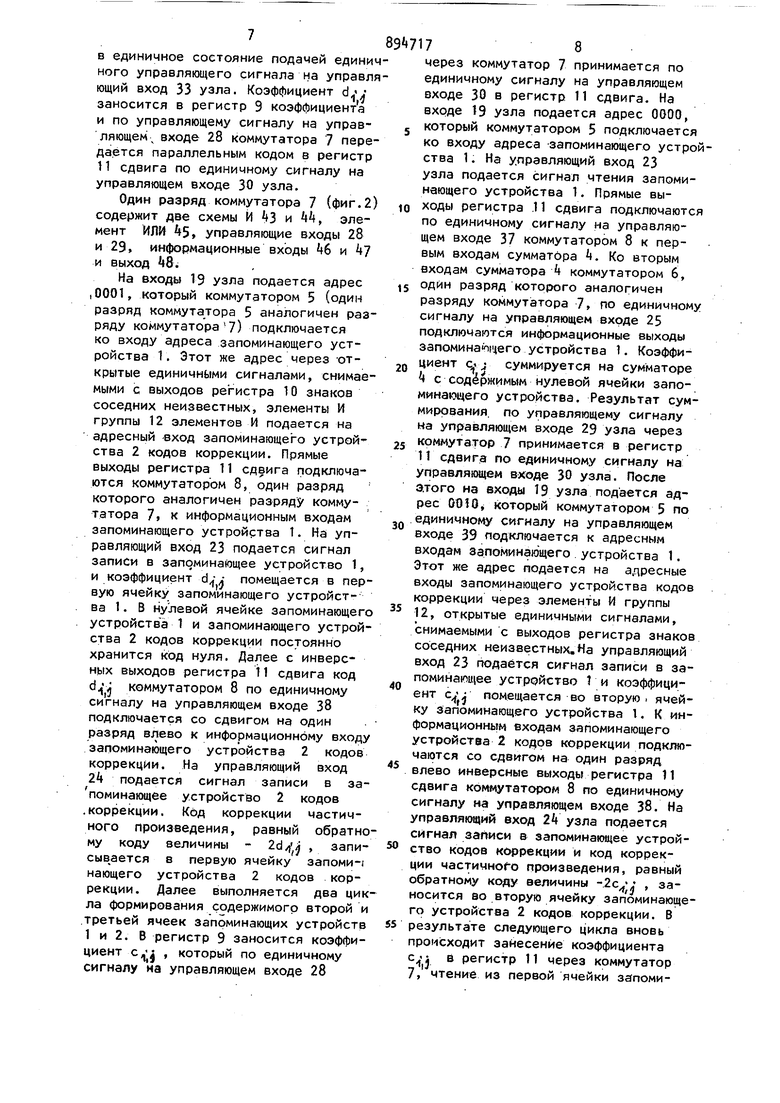

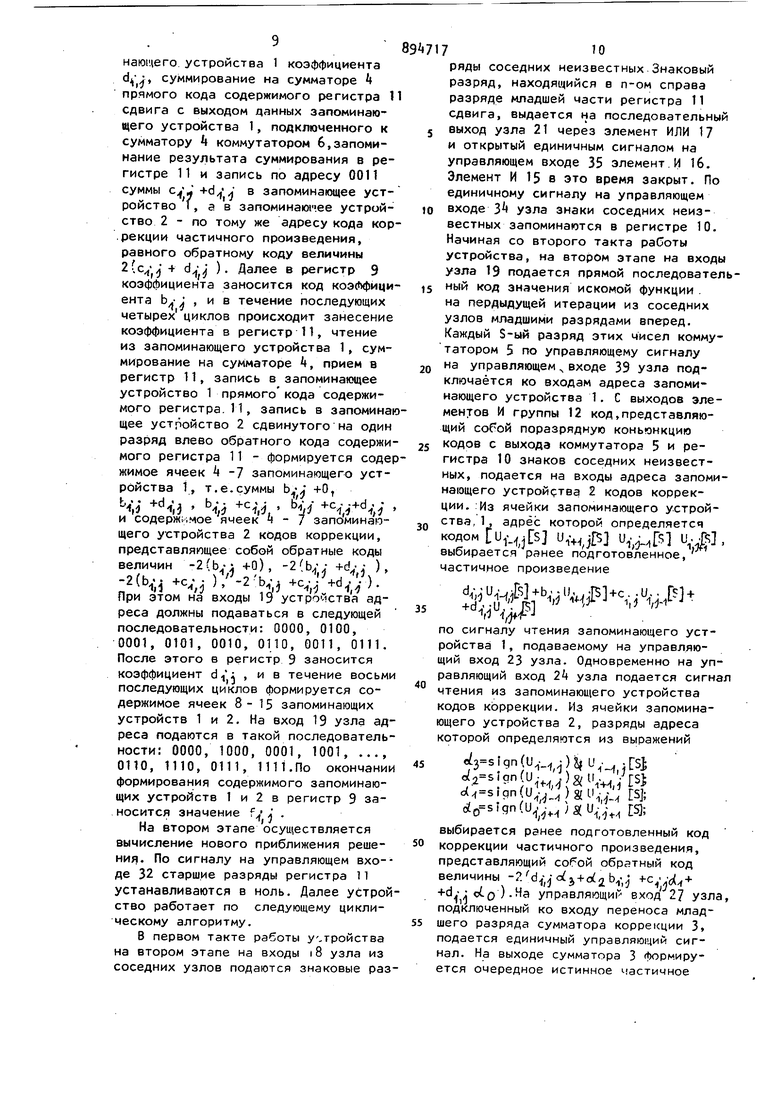

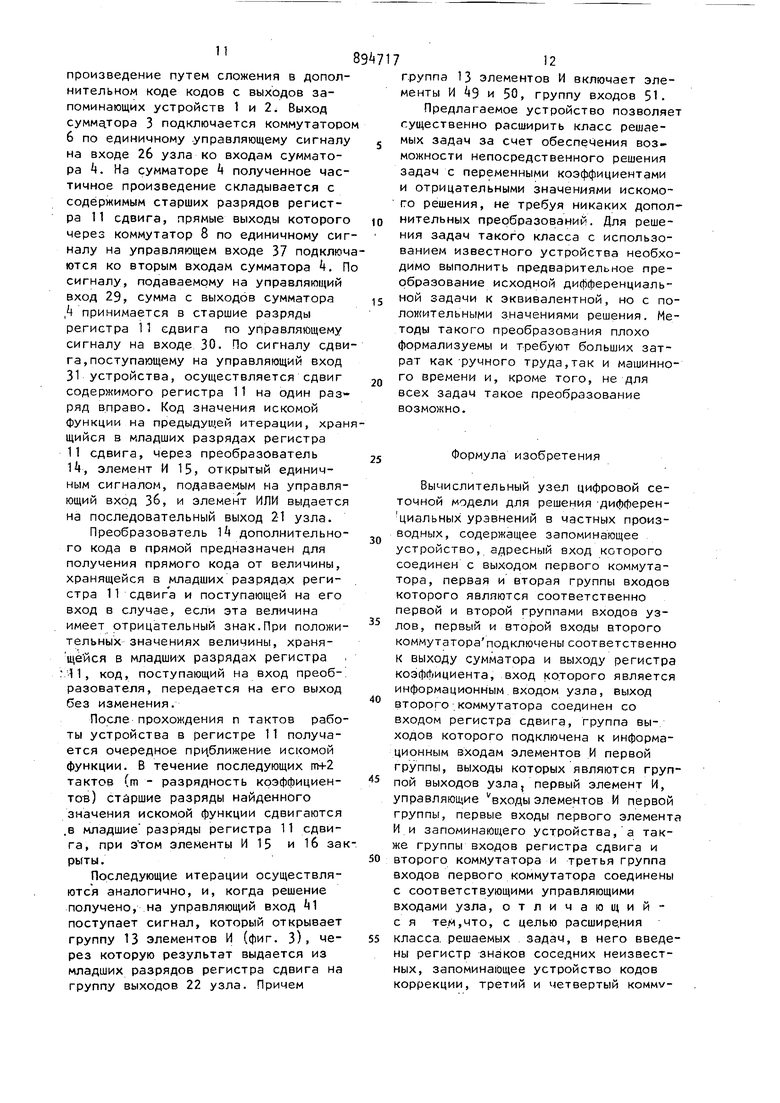

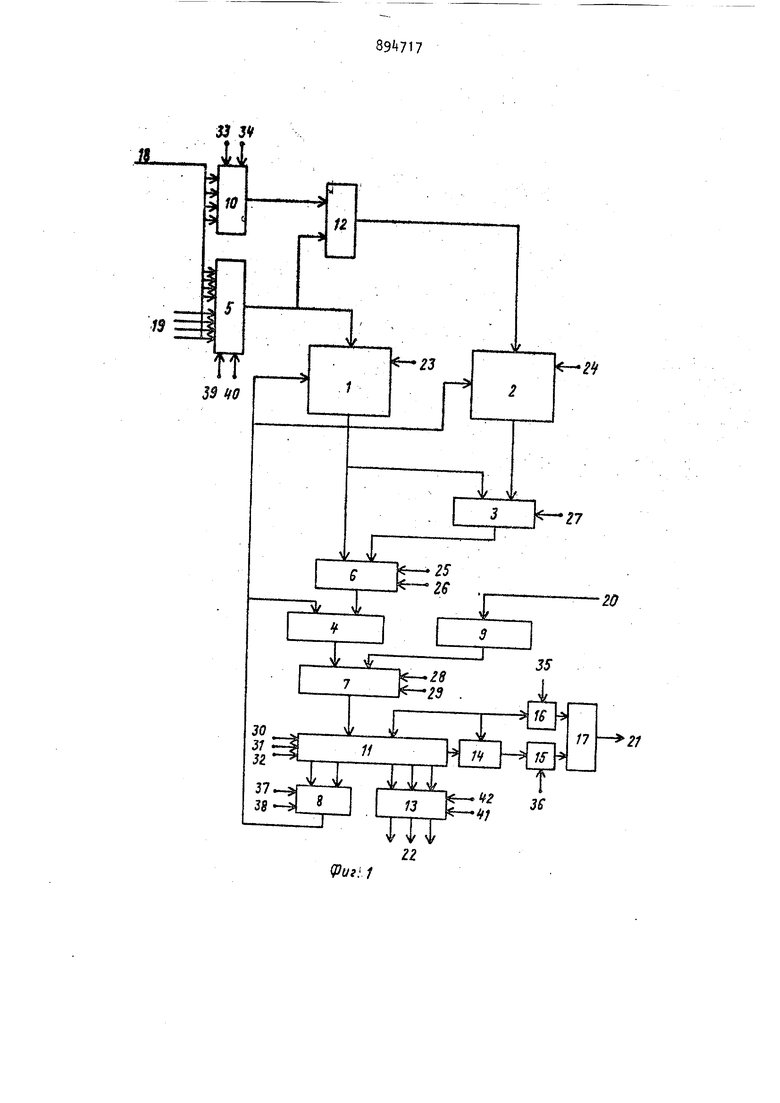

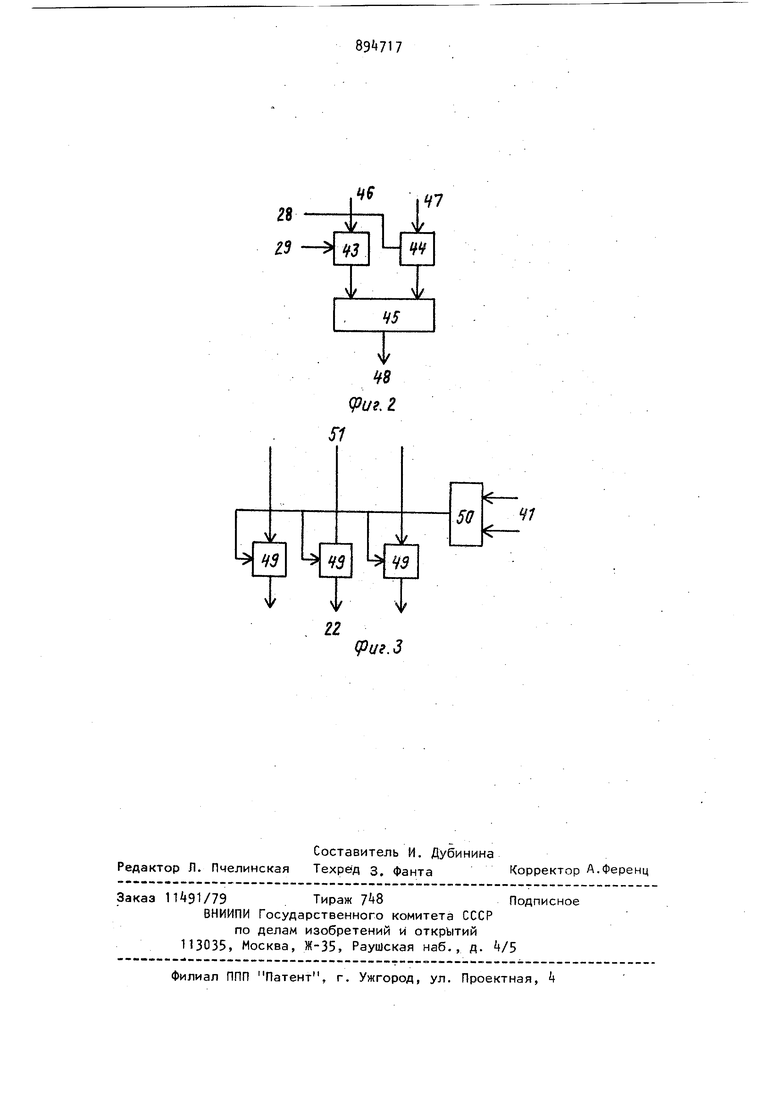

ts выходу регистра .коэффициента, выход второго коммутатора соединен со входами регистра сдвига, выход которого соединен со вторым входом сумматора и информационным входом за20поминающего устройства, входы элементов И группы соединены с вь1ходами регистра сдвига, управляющие входы элемента И, группы элементов И, запоминающего устройства, коммутаторов и регистра сдвига соединены с управляющими входами узла 2j. Недостатком известного узла является то, что он предназначен для решения дифференциальных уравнеИий с переменными коэффициентами только при положительных значениях искомых приближений решения. Решение задач, для которых решение принимает отрицательные значения на данном узле невозможно. Цель изобретения - расширение класса решаемых задач. Поставленная цель достигается ,тем, что в вычислительный узел цифровой сеточной модели для решения . дифференциальных уравнений в частных производных, содержащий запоминающее устройство, адресный вход которЬго соединен с выходом первого коммутато ра, первая и вторая группы входов ко торого являются соответственно перво и второй группами входов узла, первый и второй входы второго коммутатора подключены соответственно к выходу сумматора и выходу регистра коэффициента, вход которого является информационным входом узла, выход второго коммутатора соединен со входом регистра сдвига, группа выходов которого подключена к информационным входам элементов И первой груп пы, выходы которых являются группой выходов узла, первый элемент И, уп. равляющие входы элементов И первой группы, первые входы первого элемента И и запоминающего устройства, а также группы входов регистра сдвига и второго коммутатора и третья группа входов первого коммутатора соединены с соответствующими управляющими входами узла, введены регистр знаков соседних неизвестных, запоминающее устройство кодов коррекции, третий и четвертый коммутаторы, сумматор коррекции, преобразователь дополнительного кода в прямой, второй элемент И еторая группа элементов И и элемент ИЛИ, выход которого является информа ционным выходом узла, вход регистра знаков соседних неизвестных соединен с первой группой входов узла, выходы регистра знаков соседних неизвестных и первого коммутатора подключе ны соответственно к первому и второму входам элементов И второй группы,групп в:)1ходов которой соединена с группой адресных входов запоминающего устрой 74 ства кодов коррекции, группа выходов которого подключена к первой группе входов сумматора коррекции, группа ыходов которого соединена с первой группой входов третьего коммутатора, группа выходов которого подключена к первой группе входов сумматора, прямые и инверсные выходы разрядов регистра сдвига соединены соответственно с первой и второй группами входов четвертого коммутатора, группа выходов которого подключена ко второй группе входов сумматора, а также к информационным входам запоминающего устройства и запоминающего устройства кодов коррекции, группа выходов . запоминающего устройства соединена со вторыми группами входов третьего коммутатора и сумматора коррекции-, знаковый разряд группы младших разрядов регистра сдвига подключен к первым входам преобразователя дополнительного кода в прямой и второго элемента И, выход которого соединен с первым входом элемента ИЛИ, выход регистра сдвига подключен ко второму входу преобразователя дополнительного кода, выход которого соединен со вторым входом первого элемента И, выход которого подключен ко второму входу элемента.ИЛИ, группа управляющих входов запоминающего устройства кодов коррекции, третьи группы входов сумматора коррекции, третьего и четвертого коммутаторов и второй вход второго элемента И соединены с соответствующими управляющими входами узла. На фиг. 1 изображена блок-схема устройства; на фиг. 2 - один разряд коммутатора; На фиг. 3 - группа элементов И. В состав вычислительного узла входят запоминающее устройство 1, запоминающее устройство 2 кодов коррекции, сумматор 3 коррекции, сумматор 4, коммутаторы 5-8, регистр 9 коэффициентов, регистр 10 знаков соседних неизвестных, регистр 11 сдвига, группы 12 и 13 элементов И, преобразователь Н дополнительного кода в прямой, элементы И 15 и 16, элемент ИЛИ 17, информационные входы 18-20, последовательный информационный выход 21 узла, параллельные ийформационные выходы 22 узла, управляющие входы 23-42 узла. Адресный вход запоминающего устройства 1 соединен с выходом комМутатора 5, первая группа входов которо го соединена с информационными входами 18 узла, вторая группа входов соединена с информационными входами 19узла. Адресный вход запоминающего устройства 2 кодов коррекции соединен с выходами группы 12 элементов И, первые и вторые входы которых соединены соответственно с выходами коммутатора 5 и регистра 10 знаков соседних неизвестных, соединенного входами с информационным входом 18 узла. Информационный выход запоминаю щего устройства 1 соединен с первой группой входов коммутатора 6 и сумматора 3 коррекции, вторая группа входов и выходы которого соединены соответственно с выходом запоминающего устройства 2 кодов коррекции и второй группой входов коммутатора Выход коммутатора 6 соединен с первой группой входов сумматора k. Вторая группа входов сумматора i сое динена с выходами четвертого коммутатора 8. Выход сумматора соединен с первыми входами коммутатора 7, вторая группа входов которого сое динена с выходом регистра 9 коэффициентов. Вход регистра 9 коэффициен тов соединен с информационным входом 20узла. Выход коммутатора 7 соединен со входом регистра 11 сдвига. Прямые и инверсные выходы регистра сдвига соединены со входами коммутатора 8. Выход коммутатора 8 соеди нен с информационными входами запоми нающих устройств 1 и 2. Вторая группа в ходов регистра 11 сдвига соединена с п выми входами группы 13 элементов И Выходы группы 13 элементов И соедине ны с параллельными информационными выходами 22 узла. Последовательный выход регистра 11 сдвига соединен со входом преобразователя И дополнительного кода в прямой, выход которого соединен со входом элемента И 15. Выход знакового разряда группы младших разрядов регистра 11 сдвига соединен со входом элемента И 16 и преобразователя 1 кода.Выходы элементов И 15 и 16 соединены со входами элемента ИЛИ 17, выход которого соединен с последовательным выходом 21узла. Управляющие входы регистров коммутаторов,элементов И,запоминающи устройств и сумматора 3 соединены с со- ответствующими управляющими входами у Пердлагаемый узел цифровой сетки позволяет вычислять приближение к решению в узле сеточной области по соотношению (кн) ,.1,l -l-t, .,L,b ff. -.Hl.- индексы строки и столбца сеточной области; ,1 соответственно приведенS. ные коэффициенты и вая часть разностных уравнений; ./ ,,( Uj4.j, значения искомого решеи - , и) . ния в соседних узлах )3 i, сеточной области на пре( дыдущей итерации; - новое приближение решения в узле i,j. 1, -fJ 14{, Величины и , могут принимать как положительные так и отрицательные значения и представляются п -разрядным дополнительным кодом. Устройство работает следующим образом. Вычисление последующего приближения решения состоит в общем случае из двух этапов. На первом этапе в запоминающее устройство 1 заносятся сочетания сумм коэффициентов по О, 1, 2, 3, k членов. В запоминающее устройство 2 кодов коррекции заносятся удвоенные значения соответствующих сочетаний сумм коэффициентов по 0,1, 2, 3, членов с противоположным знаком. При этом соответствие между адресами ячеек запоминающих устройств и их содержимым устанавливается зависимостями: для запоминающего устройства 1 запоминающего устройства 2 кодов коррекции -2(,...c,..4d,,,.), де Cotjdgft ipio} двоичный адрес ячейки соответствующего запоминающего устройства. При занесении информации в запоинающие устройства 1 и 2 использутся входы 19 задания адреса запомиающих устройств узла и входы 20 адания коэффициентов узла. Предваительно все разряды регистра знаков оседних неизвестных устанавливаются / в единичное состояние подачей единич ного управляющего сигнала на управля ющий вход 33 узла. Коэффициент d заносится в регистр 9 коэффициента и по управляющему сигналу на управляющем, входе 28 коммутатора 7 передается параллельным кодом в регистр 11 сдвига по единичному сигналу на управляющем входе 30 узла. Один разряд коммутатора 7 (фиг.2 содержит две схемы И 3 и , элемент ИЛИ 45, управляющие входы 28 и 29, информационные входы б и 7 и выход 8 На входы 19 узла подается адрес ,0001, который коммутатором 5 (один разряд коммутатора 5 аналогичен раз ряду коммутатора7) подключается ко входу адреса запоминающего устройства 1. Этот же адрес через -открытые единичными сигналами, снимае мыми с выходов регистра 10 знаков соседних неизвестных, элементы И группы 12 элементов И подается на адресный «ход запоминающего устройства 2 кодов коррекции. Прямые выходы регистра 11 сдвига подключаются коммутатором 8, один разряд которого аналогичен разряду коммутатора 7, к информационным входам запоминающего устройства 1. На управляющий вход 23 подается сигнал записи в запоминающее устройство 1, и коэффициент помещается в пер вую ячейку запоминающего устройства 1 . В нулевой ячейке запоминающег устройства 1 и запоминающего устрой ства 2 кодов коррекции постоянно хранится код нуля. Далее с инверсных выходов регистра 11 сдвига код коммутатором 8 по единичному сигналу на управляющем входе 38 подключается со сдвигом нд один разряд влево к информационному вход запоминающего устройства 2 кодов коррекции. На управляющий вход 2 подается сигнал записи в за поминающее устройство 2 кодов .коррекции. Код коррекции частичного произведения, равный обратн му коду величины - 26/(л , запи сыв ается в первую ячейку запоминающего устройства 2 кодов коррекции. Далее выполняется два ци ла формирования содержимого второй третьей ячеек запоминающих устройст 1 и 2. В регистр 9 заносится коэффи циент cv| , который по единичному сигналу иа управляющем входе 28 78 через коммутатор 7 принимается по единичному сигналу на управляющем входе 30 в регистр 11 сдвига. На входе 19 узла подается адрес 0000, который коммутатором 5 подключается ко входу адреса запоминающего устройства 1. На управляющий вход 23 узла подается сигнал чтения запоминающего устройства 1. Прямые выходы регистра ,11 сдвига подключаются по единичному сигналу на управляющем входе 37 коммутатором 8 к первым входам сумматора . Ко вторым входам сумматора коммутатором 6, один разряд которого аналогичен разряду коммутатора 7, по единичному сигналу на управляющем входе 25 подключаются информационные выходы запоминапмдего устройства 1. Коэффициент . J суммируется на сумматоре Ц с содержимым нулевой ячейки запоминающего устройства. Результат суммирования, по управляющему сигналу на управляющем входе 29 узла через коммутатор 7 принимается в регистр 11 сдвига по единичному сигналу на управляющем входе 30 узла. После этого на входы 19 узла подается адрес 0018 который коммутатором 5 по единичному сигналу на управляющем входе 39 подключается к адресным входам запоминающего . устройства 1. Этот же адрес подается на адресные входы запоминающего устройства кодов коррекции через элементы И группы 12, открытые единичными сигналами, снимаемыми с выходов регистра знаков соседних неизвестных,На управляющий вход 23 подается сигнал записи в запоминающее устройство 1 и коэффициент помещается во вторую , ячейку запоминающего устройства 1. К информационньтм еходам запоминающего устройства 2 кодов коррекции подключаются со сдвигом на один разряд влево инверсные выходы регистра 11 сдвига коммутатором 8 по единичному сигналу на управляющем входе 38. На управляющий вход 2k узла подается сигнал записи в запоминающее устройство кодов коррекции и код коррекции частичного произведения, равный обратному коду величины , заносится во вторую ячейку запоминающего устройства 2 кодов коррекции. В результате следующего цикла вновь происходит занесение коэффициента в регистр 11 через коммутатор 7, чтение из первой ячейки запоми наюрдего. устройства 1 коэффициента суммирование на сумматоре 4 прямого кода содержимого р егистра 1 сдвига с выходом данных запоминающего устройства 1, подключенного к сумматору 4 коммутатором 6,запоминание результата суммирования в регистре 11 и запись по адресу ООП суммы в запоминающее устройство 1 , а в запоминакичее устройство 2 - по тому же адресу кода кор .рекции частичного произведения, равного обратному коду величины 2( 4 ). Далее в регистр 9 коэффициента заносится код ента bV : , и в течение последующих четырех циклов происходит занесение коэффициента в регистр 11, чтение из запоминающего устройства 1, суммирование на сумматоре 4, прием в регистр 11, запись в запоминающее устройство 1 прямого кода содержимого регистра.11, запись в запомина щее устройство 2 сдвинутого на один разряд влево обратного кода содержи мого регистра 11 - формируется соде жимое ячеек k -7 запоминающего устройства 1, т.е.суммы +0, Ч:; +s,. bi/ и содержимое ячеек ч - / запоминающего устройства 2 кодов коррекции, представляющее собой обратные коды величин -2( +0), ( ), -2(bY,i +cv,j )/-2bv, +c,-.j ). При этом на входы 19 устройства адреса должны подаваться в следующей последовательности: 0000, 0100, 0001, 0101, 0010, 0110, 0011, 0111. После этого в регистр 9 заносится коэффициент , и в течение восьм последующих циклов формируется содержимое ячеек 8-15 запоминающих устройств 1 и 2, На вход 19 узла ад реса подаются в такой последователь ности: 0000, 1000, 0001, 1001 0110, 1110, 0111, 1111.По окончани формирования содержимого запоминающих устройств 1 и 2 в регистр 9 заносится значение fу . На втором этапе осуществляется вычисление нового приближения решения. По сигналу на управляющем входе 32 старшие разряды регистра 11 устанавливаются в ноль. Далее устро ство работает по следующему циклическому алгоритму. В первом такте работы устройства на втором этапе на входы i8 узла из соседних узлов подаются знаковые раз О ряды соседних неизвестных Знаковый разряд, находящийся в п-ом справа разряде младшей части регистра 11 сдвига, выдается на последовательный выход узла 21 через элемент ИЛИ 17 и открытый единичным сигналом на управляющем входе 35 элемент.И 16. Элемент И 15 в это время закрыт. По единичному сигналу на управляющем входе 3 узла знаки соседних неизвестных запоминаются в регистре 10. Начиная со второго такта работы устройства, на втором этапе на входы узла 19 подается прямой последовательный код значения искомой функции . на пердыдущей итерации из соседних узлов младшими разрядами вперед. Каждый S-ый разряд этих чисел коммутатором 5 по управляющему сигналу на управляющем., входе 39 узла подключается ко входам адреса запоминающего устройства 1. С выходов элементов И группы 12 код,представляющий собой поразрядную коньонкцию кодов с выхода коммутатора 5 и регистра 10 знаков соседних неизвестных, подается на входы адреса запоминающего устройства 2 кодов коррекции. -Из ячейки запоминающего устройства, 1, адрес которой определяется кодом и,ц.)Г5 U, и,.,р1 Ь-ТЯ, выбирается ранее подготовленное, частичное произведение 1) 1,J4fПО сигналу чтения запоминающего устройства 1, подаваемому на управляющий вход 23 узла. Одновременно на управляющий вход 24 узла подается сигнал чтения из запоминающего устройства кодов коррекции. Из ячейки запоминающего устройства 2, разряды адреса которой определяются из выражений (u,.,)S,u. .rsi . и. ) o(,sian(u;;:,) o((u..).,V, И; выбирается ранее подготовленный код коррекции частичного произведения, представляющий обратный код величины -2d,,, + 4j управляющий вход 2 узла, подключенный ко входу переноса младшего разряда сумматора коррекции 3, подается единичный управляющий си1- нал. На выходе сумматора 3 формируется очередное истинное частичное произведение путем сложения в дополнительном коде кодов с выходов запоминающих устройств 1 и 2. Выход суммд.тора 3 подключается коммутаторо 6 по единичному .управляющему сигналу на входе 26 узла ко входам сумматора . На сумматоре 4 полученное частичное произведение складывается с содержимым старших разрядов регистра 11 сдвига, прямые выходы которого через коммутатор 8 по единичному сиг налу на управляющем входе 37 подключ ются ко вторым входам сумматора k. П сигналу, подаваемому на управляющий вход 29, сумма с выходов сумматора ,А принимается в старшие разряды регистра 11 сдвига по управляющему сигналу на входе 30. По сигналу сдви га, поступающему на управляющий вход 31 устройства, осуществляется сдвиг содержимого регистра 11 на один разряд вправо. Код значения искомой функции на предыдуш.ей итерации, хран щийся в младших разрядах регистра 11 сдвига, через преобразователь Т, элемент И 15, открытый единичным сигналом, подаваемым на управляющий вход Зб, и элемент ИЛИ выдается на последовательный выход 21 узла. Преобразователь Н дополнительного кода в прямой предназначен для получения прямого кода от величины, хранящейся в младших разрядах регистра 11 сдвига и поступающей на его вход в случае, если эта величина имеет отрицательный знак.При положительных значениях величины, хранящейся в младши-х разрядах регистра :-11 , код, поступающий на вход преобразователя, передается на его выход без изменения. После прохождения п тактов рабо ты устройства в регистре 11 получается очередное приближение искомой функции. В течение последующих т+2 тактое (т - разрядность крэффициентов) стйршие разряды найденного значения искомой функции сдвигаются .в младшие разряды регистра 11 сдвига, при этом элементы И 15 и 16 за рыты. Последующие итерации осуществляются аналогично, и, когда решение получено, на управляющий вход поступает сигнал, который открывает группу 13 элементов И (фиг. 3), через которую результат выдается из младших разрядов регистра сдвига на группу выходов 22 узла. Причем 12 группа 13 элементов И включает элементы И 49 и 50, группу входов 51. Предлагаемое устройство позволяет существенно расширить класс решаемых задач за счет обеспечения возможности непосредственного решения задач с переменными коэффициентами и отрицательными значениями искомого решения, не требуя никаких дополнительных преобразований. Для решения задач такого класса с использованием известного устройства необходимо выполнить предварительное преобразование исходной дифференциальной задачи к эквивалентной, но с положительными значениями решения. Методы такого преобразования плохо формализуемы и требуют больших затрат как -ручного труда,так и машинного времени и, кроме того, не для всех задач такое преобразование возможно. Формула изобретения Вычислительный узел цифровой сеточной модели для решения -дифференциальных уравнений в частных производных, содержащее запоминающее , устройство,. адресный вход которого соединен с выходом первого коммутатора, первая и вторая группы входов которого являются соответственно первой и второй группами входов узлов, первый и второй входы второго коммутатораподключены соответственно К выходу сумматора и выходу регистра коэффициента, вход которого является информационным входом узла, выход второго коммутатора соединен со входом регистра сдвига, группа выходов которого подключена к информационным входам элементов И первой группы, выходы которых являются группой выходов узла, первый элемент И, управляющие входы элементов И первой группы, первые входы первого элемента И и запоминающего устройства,а также группы входов регистра сдвига и второго коммутатора и третья группа входов первого коммутатора соединены с соответствующими управляющими входами узла, отличаю щийс я тем,что, с целью расширения класса, решаемых задач, в него введены регистр знаков соседних неизвестных, запоминающее устройство кодов коррекции, третий и четвертый KOMMVтаторы, сумматор коррекции, преобразователь дополнительного кода в прямой, второй элемент И, вторая группа .элементов И и элемент ИЛИ, выход которого является информационным выходом узла, вход регистра знаков соседних неизвестных соединен с первой группой входов узла, выходы регистра знаков соседних неизвестных и первого коммутатора подключены соответственно к первому и второму входам элементов И второй группы, группа выходов которой соединена с группой адресных входов запоминающего устройства кодов коррекции, группа выходов которого подключена к первой группе входов сумматора кор рекции, группа выходов которого соединена с первой группой входов треть его коммутатора, группа выходов кото рого подключена к первой группе вхо дов сумматора, прямые и инверсные выходы разрядов регистра сдвига соединены соответственно с первой и второй группами входов четвертого коммутатора, группа выходов которого подключена ко второй группе входов сумматора, а также к информационным входам запоминающего устройства и запоминающего устройства кодов рекции, -группа выходов запоминающего устройства соединена со вторыми группами входов третьего коммутатора и сумматора коррекции, знаковый разряд группы младших разрядов регистра сдвига подключен к первым входам преобразователя дополнительного кода в прямой и второго элемента И, выход которого соединен с первым входом элемента ИЛИ, выход регистра сдвига подключен ко второму входу преобразователя дополнительного кода,выход которого соединен со вторым входом первого элемента И, выход которого подключен ко второму входу элемента ИЛИ,группа управляющих входов запоминающего устройства кодов коррекций, третьи группы входов сумматоров коррекции, третьего и четвертого коммутаторов и второй вход второго элемента И соединены с соответствующими управляющими входами узла. Источники информации, принятые во внимание при экспертизе 1- Авторское свидетельство СССР ff , кл. G 06 F 15/3, 1975. 2. Авторское сивдетельство СССР по заявке № 271.7710/18-24, кл. G Об F 15/32, 27.07.79 (прототип).

(риг: 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1980 |

|

SU926667A1 |

| Вычислительный узел цифровой сетки для решения дифференциальных уравнений в частных производных | 1981 |

|

SU976448A1 |

| Вычислительный узел цифровой сеточ-НОй МОдЕли для РЕшЕНия диффЕРЕНциАль-НыХ уРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU840920A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Вычислительный узел цифровойСЕТОчНОй МОдЕли для РЕшЕНия диффЕРЕН-циАльНыХ уРАВНЕНий B чАСТНыХ пРОизВОд-НыХ | 1978 |

|

SU798858A1 |

| Устройство для решения двумерныхзАдАч МАТЕМАТичЕСКОй физиКи | 1978 |

|

SU811272A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Устройство для вычисления коэффициентов преобразования по Уолшу-Адамару | 1983 |

|

SU1107133A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

Авторы

Даты

1981-12-30—Публикация

1980-03-03—Подача