1

Изобретение относится к вычислительной технике и может быть использовано для интегрирования аналоговой информации с представлением результата вычисления как в виде цифрового кода, так и в виде напряжения.

Известно, что при длительном интегрировании аналогового сигнала обычно осуществляется аналого-цифровое преобразование, а в качестве накопителя информации используется реверсивный счетчик 1.

Если результат вычисления необходимо представить в виде напряжения, то для этой цели на выходе счетчика устанавливается преобразователь кода в напряжение.

Основными недостатками такого устройства является существенное увеличение емкости реверсивного счетчика при длительном интегрировании и низкая помехоустойчивость, так как на вход реверсивного счетчика поступает числовой эквивалент текущего значения входного сигнала.

Известно интегрирующее устройство, содержащее аналоговый интегратор, выполненный на базе операционного усилителя, в цепь обратной связи которого для устранения влияния дестабилизирующих факторов, введен цифровой повторитель и формирователь корректирующих сигналов 2.

Недостатком такого устройства является ограниченный динамический диапазон входных сигналов, обусловленный конечной величиной интегрирующего конденсатора и величиной линейного участка характеристики операционного усилителя.

Наиболее близким по технической сущности к изобретению является устройство, состоящее из последовательно соединенных аналогового интегратора, блока сравнения, реверсивного счетчика и преобразователя кода в напряжение, причем выход сравнивающего устройства соединен с выходом обнуления аналогового интегратора, которое отвечает всем поставленным в данной задаче техническим требованиям, за исключением точности интегрирования при малых величинах входных сигналов 3.

Целью изобретения является повышение точности интегрирования аналого-цифрового интегратора.

Это достигается тем, что в аналого-цифровой интегратор, содержащий последовательно соединенные аналоговый интегратор, блок сравнения, первый реверсивный счетчик и преобразователь кода в напряжение, причем выход блока сравнения подключен к разрядному входу интегратора, введены формирователь временных интервалов, блок сравнения временных интервалов,

второй реверсивный счетчик и дешифратор, соединенные последовательно, причем выход дешифратора подключен к выходу управления постоянной времени интегрирования аналогового интегратора и входу управления коэффициентом пересчета первого реверсивного счетчика, а выход блока сравнения соединен с вторым входом блока сравнения временных интервалов и входом формирователя временных интервалов.

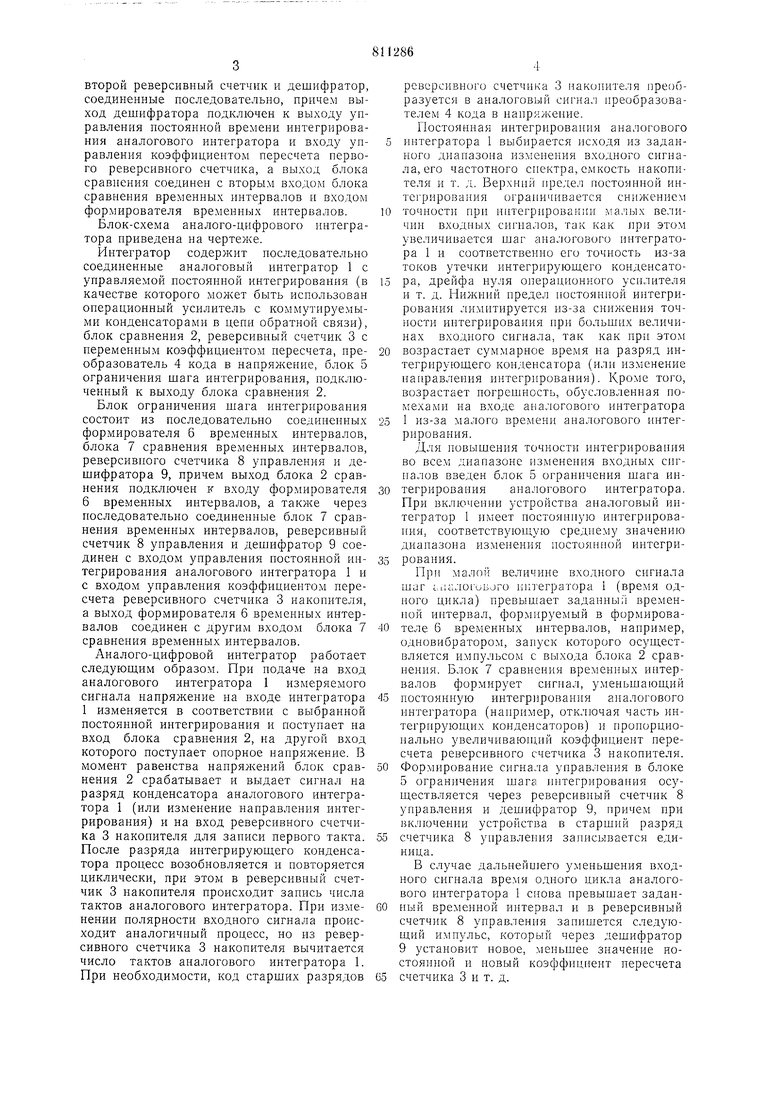

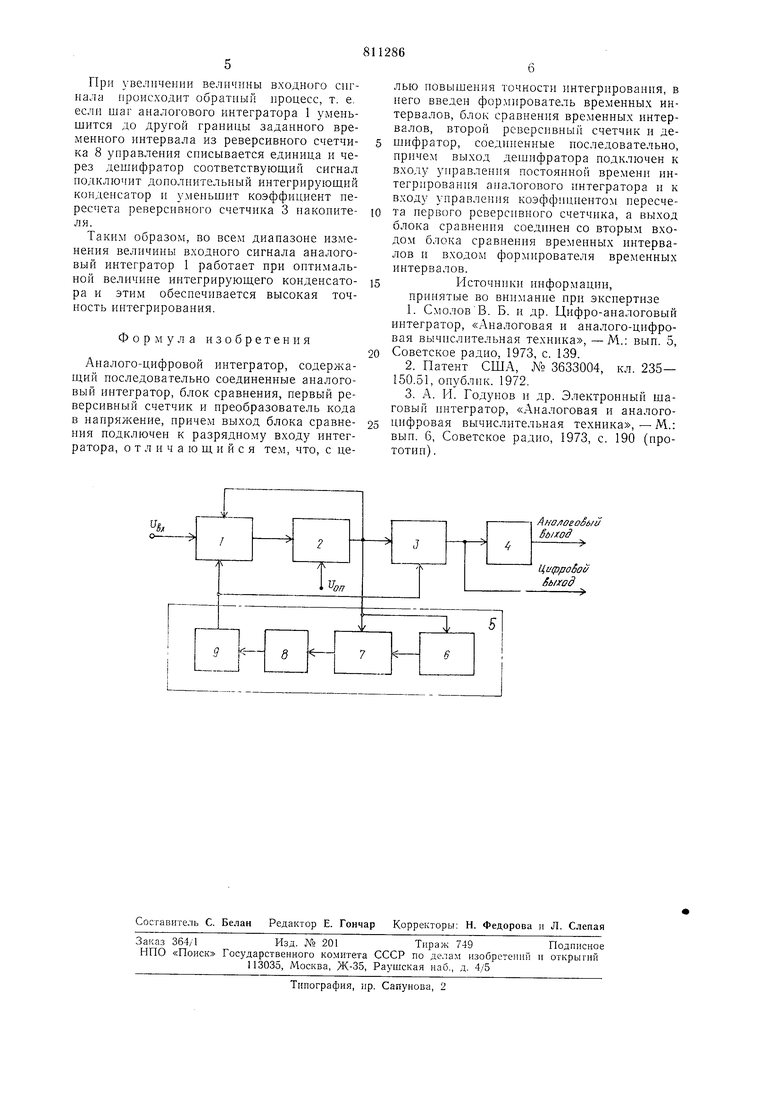

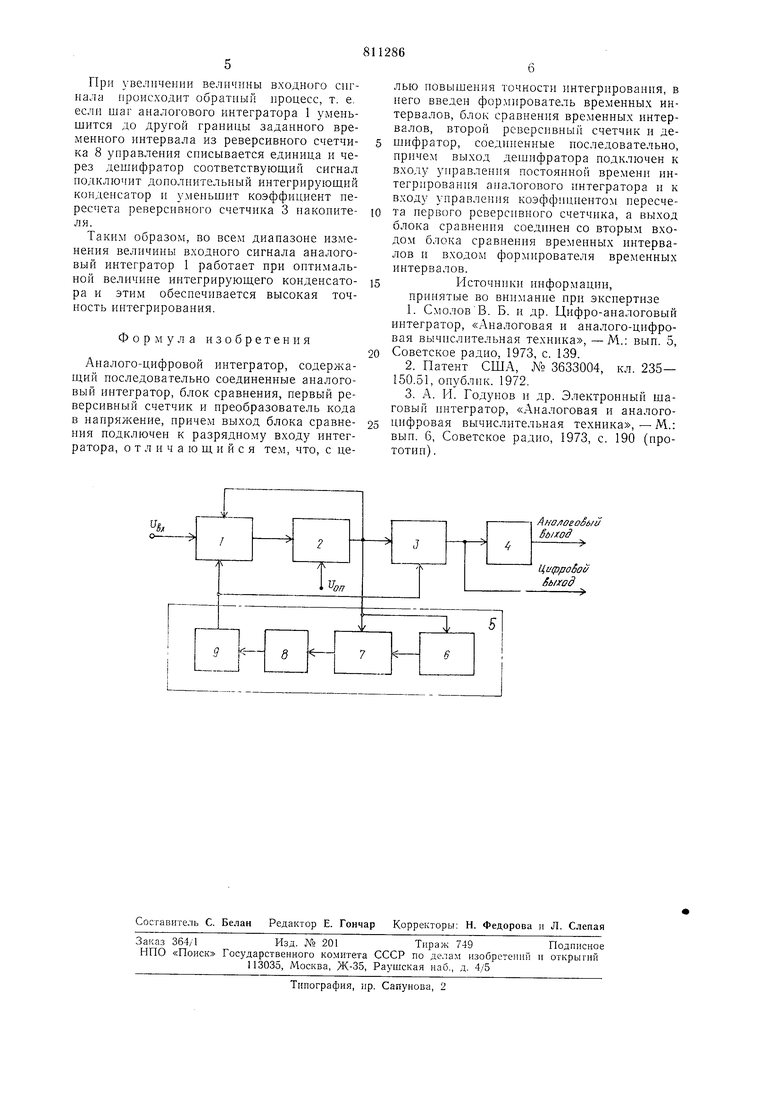

Блок-схема аналого-цифрового интегратора приведена на чертеже.

Интегратор содержит последовательно соединенные аналоговый интегратор 1 с управляемой постоянной интегрирования (в качестве которого может быть использован операционный усилитель с коммутируемыми конденсаторами в цепи обратной связи), блок сравнения 2, реверсивный счетчик 3 с переменным коэффициентом пересчета, преобразователь 4 кода в напряжение, блок 5 ограничения шага интегрирования, подключенный к выходу блока сравнения 2.

Блок ограничения шага интегрирования состоит из последовательно соединенных формирователя 6 временных интервалов, блока 7 сравнения временных интервалов, реверсивного счетчика 8 управления и дешифратора 9, причем выход блока 2 сравнения подключен к входу формирователя 6 временных интервалов, а через последовательно соединенные блок 7 сравнения временных интервалов, реверсивный счетчик 8 управления и дешифратор 9 соединен с входом управления постоянной интегрирования аналогового интегратора 1 и с входом управления коэффициентом пересчета реверсивного счетчика 3 накопителя, а выход формирователя 6 временных интервалов соединен с Другим входом блока 7 сравнения временных интервалов.

Аналого-цифровой интегратор работает следуюшим образом. При подаче на вход аналогового интегратора 1 измеряемого сигнала напряжение на входе интегратора 1 изменяется в соответствии с выбранной постоянной интегрирования и поступает на вход блока сравнения 2, на другой вход которого поступает опорное напряжение. В момент равенства напряжений блок сравнения 2 срабатывает и выдает сигнал на разряд конденсатора аналогового интегратора 1 (или изменение направления интегрирования) и на вход реверсивного счетчика 3 накопителя для записи первого такта. После разряда интегрирующего конденсатора процесс возобновляется и повторяется циклически, при этом в реверсивный счетчик 3 накопителя происходит запись числа тактов аналогового интегратора. При изменении полярности входного сигнала происходит аналогичный процесс, но из реверсивного счетчика 3 накопителя вычитается число тактов аналогового интегратора 1. При необходимости, код старших разрядов

реверсивного счетчика 3 накопителя преобразуется в аналоговый сигнал преобразователем 4 кода в напряжеиие.

Постоянная интегрирования аналогового интегратора 1 выбирается исходя из заданного диапазона изменения входного сигнала, его частотного спектра, емкость накопителя и т. д. Верхний предел постоянной интегрирования ограничивается снижением

точности при интегрировании малых величин входных сигналов, так как при этом увеличивается шаг аналогового интегратора 1 и соответственно его точность из-за токов утечки иитегрируюш,его коиденсатора, дрейфа нуля операционного усилителя и т. д. Нижний предел постоянной интегрирования лимитируется из-за снижения точности интегрирования при больших величинах входного сигнала, так как при этом

возрастает суммарное время на разряд интегрируюш,его конденсатора (или изменение направления интегрирования). Кроме того, возрастает погрешность, обусловленная помехами на входе аналогового интегратора

1 из-за малого времени аналогового интегрирования.

Для повышения точности интегрирования во всем диапазопе изменения входных сигналов введен блок 5 ограничения шага интегрирования аналогового интегратора. При включении устройства аналоговый интегратор 1 имеет постоянную интегрирования, соответствуюпдую среднему значению диапазона изменения постоянной интегрирования.

При малой величине входного сигнала Djar йиалогоБого интегратора 1 (время одного цикла) превышает заданный временной интервал, формируемый в формирователе 6 временных интервалов, например, одновибратором, запуск которого осуш,ествляется импульсом с выхода блока 2 сравнения. Блок 7 сравнения временных интервалов формирует сигиал, уменьшаюш,ий

постоянную интегрирования аналогового интегратора (например, отключая часть интегрирующих конденсаторов) и пропорционально увеличивающий коэффициент пересчета реверсивного счетчика 3 накопителя.

Формирование сигнала управления в блоке 5 ограничения шага интегрирования осуществляется через реверсивный счетчик 8 управления и дешифратор 9, причем при включении устройства в старший разряд

счетчика 8 управления записывается единица.

В случае дальнейшего уменьшения входного сигнала время одного цикла аналогового интегратора 1 снова превышает заданный временной интервал и в реверсивный счетчик 8 управления запишется следующий импульс, который через дешифратор 9 установит новое, меньшее значение постоянной и новый коэффициент пересчета

счетчика 3 и т. д.

При увеличении величины входного сигнала происходит обратный нроцесс, т. е. если шаг аналогового интегратора 1 уменьшится до другой границы заданного временного интервала из реверсивного счетчика 8 управления списывается единица и через дешифратор соответствующий сигнал подключит дополнительный интегрирующий конденсатор и уменьшит коэффициент пересчета реверсивного счетчика 3 накопителя.

Таким образом, во всем диапазоне изменения величины входного сигнала аналоговый интегратор 1 работает при оптимальной величине интегрирующего конденсатора и этим обеспечивается высокая точность интегрирования.

Формула изобретения

Аналого-цифровой интегратор, содержащий последовательно соединенные аналоговый интегратор, блок сравнения, первый реверсивный счетчик и преобразователь кода в напряжение, причем выход блока сравнения подключен к разрядному входу интегратора, отличающийся тем, что, с целью повышения точности интегрирования, в него введен формирователь временных интервалов, блок сравнения временных интервалов, второй реверсивный счетчик и дешифратор, соединенные последовательно, причем выход дешифратора подключен к входу управления постоянной времени интегрирования аналогового интегратора и к входу управления коэффициентом пересчета первого реверсивного счетчика, а выход блока сравнения соединен со вторым входом блока сравнения временных интервалов и входом формирователя временных интервалов.

Источники информации,

принятые во внимание при экспертизе

1.СмоловВ. Б. и др. Цифро-аналоговый интегратор, «Аналоговая и аналого-цифровая вычислительная техника, -М.: вып. 5,

Советское радио, 1973, с. 139.

2.Патент США, 3633004, кл. 235- 150.51, опублик. 1972.

3.А. И. Годунов и др. Электронный шаговый интегратор, «Аналоговая и аналогоцифровая вычислительная техника,-М.: вып. 6, Советское радио, 1973, с. 190 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство регулирования компенсатора реактивной мощности | 1990 |

|

SU1830524A1 |

| Аналого-дискретное интегрирующее устройство | 1986 |

|

SU1377875A1 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| Аналого-цифровое интегрирующее устройство | 1980 |

|

SU868784A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1985 |

|

SU1414127A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU849236A1 |

| Способ аналого-цифрового преобразования с весовым интегрированием и устройство для его реализации | 1981 |

|

SU953722A1 |

| Способ интегрирующего аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1381709A1 |

| Преобразователь частоты следования импульсов в напряжение постоянного тока | 1984 |

|

SU1250977A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

Авторы

Даты

1981-03-07—Публикация

1979-02-07—Подача