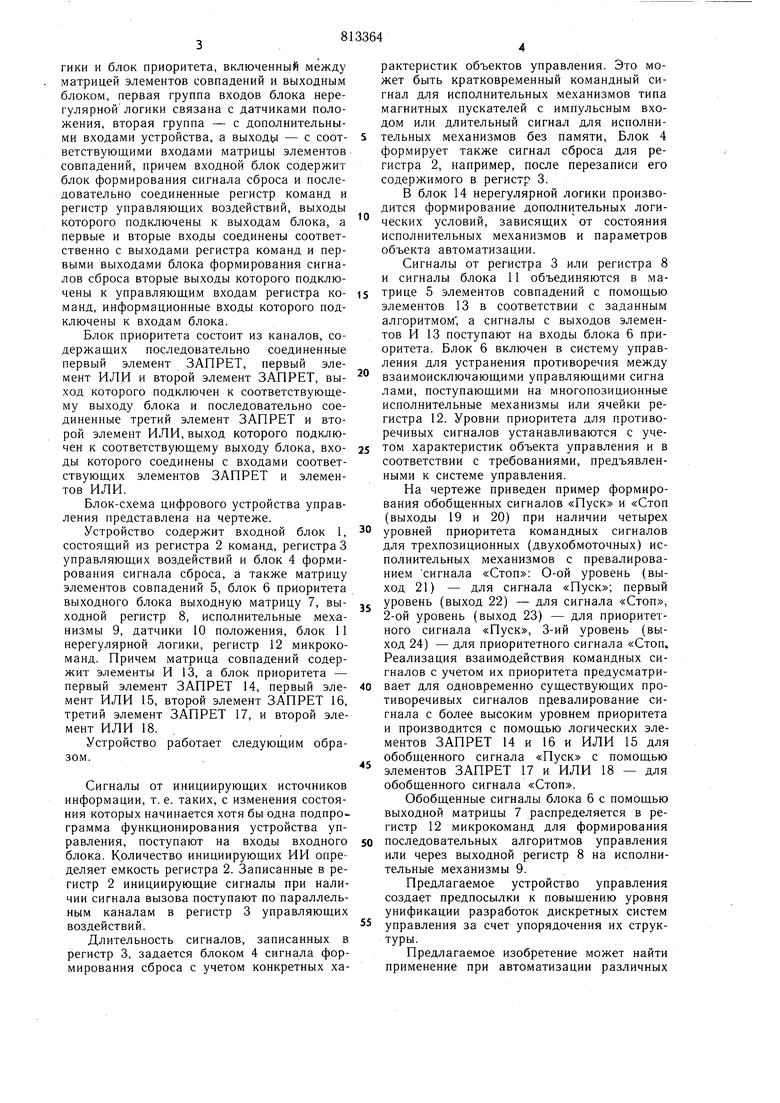

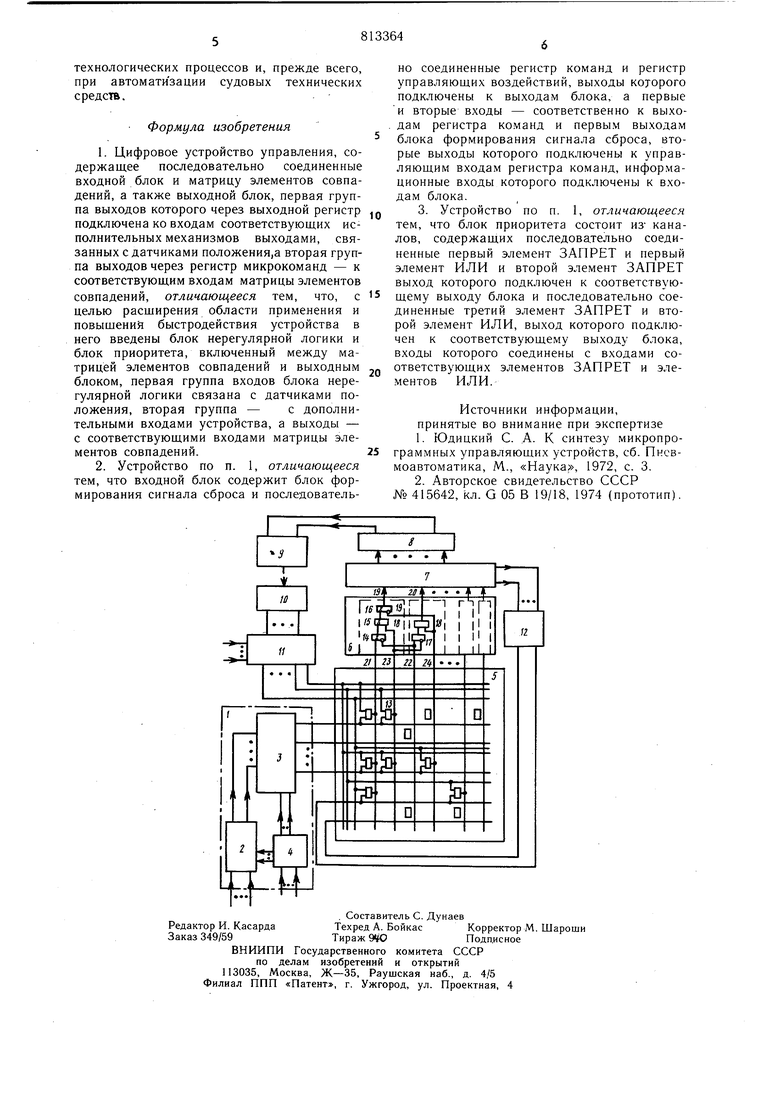

Изобретение относится к автоматическому управлению и может быть применено при автоматизации различных технологических процессов, в частности при управлении судовыми техническими средствами. Известно устройство управления, содержащее блок предст-авления событий (БПС) и микропрограммный автомат (МА). БПС получает информацию от высших, инициирующих источников информации (ИИ), определяющих изменение условий работы объекта управления и дополнительных ИИ, связанных с состоянием датчиков исполнительных механизмов. БП.С вырабатывает сигналы логических условий для МА, поступающие на ячейки матрицы совпадений вместе с сигналами микрокоманд - «предщественников. Выход-ы блока микрокоманд связаны непосредственно с усилителями блока выходов. Такое устройство может быть использовано для независимых выходных сигналов, поступающих, например, для управления одновходовыми ИИ 1. Недостаток этого устройства - ограниченная область применения, что не позволяет управлять многопозиционными исполнительными механизмами. Наиболее близким по технической сущности и достигаемому результату к предлагаемому является управляющее устройство, содержащее последовательно соединенные входной блок и матрицу элементов совпадений, а также выходной блок, первая группа выходов .которого через выходной регистр подключена ко входам соответствующих исполнительных механизмов выходами, связанных с датчиками положения, а вторая группа выходов через регистр микрокоманд - к соответствующим входам матрицы элементов совпадений 2 Недостатком данного устройства является недостаточное быстродействие вследствие последовательного способа обработки информации, а также невозможность управлять многопозиционными исполнительными механизмами. Цель изобретения - расширение области применения и повыщение быстродействия устройства-. Указанная цель достигается тем, что в устройство введены блок нерегулярной логики и блок приоритета, включенный между матрицей элементов совпадений и выходным блоком, первая группа входов блока нерегулярной логики связана с датчиками положения, вторая группа - с дополнительными входами устройства, а выходы - с соответствующими входами матрицы элементов совпадений, причем входной блок содержит блок формирования сигнала сброса и последовательно соединенные регистр команд и регистр управляющих воздействий, выходы которого подключены к выходам блока, а первые и вторые входы соединены соответственно с выходами регистра команд и первыми выходами блока формирования сигналов сброса вторые выходы которого подключены к управляющим входам регистра команд, информационные входы которого подключены к входам блока. Блок приоритета состоит из каналов, содержащих последовательно соединенные первый элемент ЗАПРЕТ, первый элемент ИЛИ и второй элемент ЗАПРЕТ, выход которого подключен к соответствующему выходу блока и последовательно соединенные третий элемент ЗАПРЕТ и второй элемент ИЛИ, выход которого подключен к соответствующему выходу блока, входы которого соединены с входами соответствующих элементов ЗАПРЕТ и элементов ИЛИ. Блок-схема цифрового устройства управления представлена на чертеже. Устройство содержит входной блок 1, состоящий из регистра 2 команд, регистра 3 управляющих воздействий и блок 4 формирования сигнала сброса, а также матрицу элементов совпадений 5, блок 6 приоритета выходного блока выходную матрицу 7, выходной регистр 8, исполнительные мех-анизмы 9, датчики 10 положения, блок 11 нерегулярной логики, регистр 12 микрокоманд. Причем матрица совпадений содержит элементы И 13, а блок приоритета - первый элемент ЗАПРЕТ 14, первый элемент ИЛИ 15, второй элемент ЗАПРЕТ 16, третий элемент ЗАПРЕТ 17, и второй элемент ИЛИ 18. Устройство работает следующим образом. Сигналы от инициирующих источников информации, т. е. таких, с изменения состояния которых начинается хотя бы одна подпро грамма функционирования устройства управления, поступают на входы входного блока. Количество инициирующих ИИ определяет емкость регистра 2. Записанные в регистр 2 инициирующие сигналы при наличии сигнала вызова поступают по параллельным каналам в регистр 3 управляющих воздействий. Длительность сигналов, записанных в регистр 3, задается блоком 4 сигнала формирования сброса с учетом конкретных характеристик объектов управления. Это может быть кратковременный командный сигнал для исполнительных механизмов типа магнитных пускателей с импульсным входом или длительный сигнал для исполнительных механизмов без памяти. Блок 4 формирует также сигнал сброса для регистра 2, например, после перезаписи его содержимого в регистр 3. В блок 14 нерегулярной логики производится формирование дополнительных логических условий, зависящих от состояния исполнительных механизмов и параметров объекта автоматизации. Сигналы от регистра 3 или регистра 8 и сигналы блока 11 объединяются в матрице 5 элементов совпадений с помощью элементов 13 в соответствии с заданным алгоритмом , а сигналы с выходов элементов И 13 поступают на входы блока 6 приоритета. Блок 6 включен в систему управления для устранения противоречия между взаимоисключающими управляющими сигна лами, поступающими на многопозиционные исполнительные механизмы или ячейки регистра 12. Уровни приоритета для противоречивых сигналов устанавливаются с учетом характеристик объекта управления и в соответствии с требованиями, предъявленными к системе управления. На чертеже приведен пример формирования обобщенных сигналов «Пуск и «Стоп (выходы 19 и 20) при наличии четырех уровней приоритета командных сигналов для трехпозиционных (двухобмоточных) исполнительных механизмов с превалированием сигнала «Стоп : О-ой уровень (выход 21) - для сигнала «Пуск ; первый уровень (выход 22) - для сигнала «Стоп, 2-ой уровень (выход 23) - для приоритетного сигнала «Пуск, 3-ий уровень (выход 24) - для приоритетного сигнала «Стоп. Реализация взаимодействия командных сигналов с учетом их приоритета предусматривает для одновременно существующих противоречивых сигналов превалирование сигнала с более высоким уровнем приоритета и производится с помощью логических элементов ЗАПРЕТ 14 и 16 и ИЛИ 15 для обобщенного сигнала «Пуск с помощью элементов ЗАПРЕТ 17 и ИЛИ 18 - для обобщенного сигнала «Стоп. Обобщенные сигналы блока 6 с помощью выходной матрицы 7 распределяется в регистр 12 микрокоманд для формирования последовательных алгоритмов управления или через выходной регистр 8 на исполнительные механизмы 9. Предлагаемое устройство управления создает предпосылки к повышению уровня унификации разработок дискретных систем управления за счет упорядочения их структуры. Предлагаемое изобретение может найти применение при автоматизации различных

технологических процессов и, прежде всего, при автоматизации судовых технических средств.

Формула изобретения

1.Цифровое устройство управления, содержащее последовательно соединенные входной блок и матрицу элементов совпадений, а также выходной блок, первая группа выходов которого через выходной регистр подключена ко входам соответствующих исполнительных механизмов выходами, связанных с датчиками положения,а вторая группа выходов через регистр микрокоманд - к соответствующим входам матрицы элементов совпадений, отличающееся тем, что, с целью расщирения области применения и повышения быстродействия устройства в него введены блок нерегулярной логики и блок приоритета, включенный между матрицей элементов совпадений и выходным блоком, первая группа входов блока нерегулярной логики связана с датчиками положения, вторая группа - с дополнительными входами устройства, а выходы -

с соответствующими входами матрицы элементов совпадений.

2.Устройство по п. 1, отличающееся тем, что входной блок содержит блок формирования сигнала сброса и последовательно соединенные регистр команд и регистр управляющих воздействий, выходы которого подключены к выходам блока, а первые и вторые входы - соответственно к выходам регистра команд и первым выходам блока формирования сигнала сброса, вторые выходы которого подключены к управляющим входам регистра команд, информационные входы которого подключены к входам блока.

3. Устройство по п. 1, отличающееся тем, что блок приоритета состоит из каналов, содержащих последовательно соединенные первый элемент ЗАПРЕТ и первый элемент ИЛИ и второй элемент ЗАПРЕТ выход которого подключен к соответствующему выходу блока и последовательно соединенные третий элемент ЗАПРЕТ и второй элемент ИЛИ, выход которого подключен к соответствующему выходу блока, входы которого соединены с входами соответствующих элементов ЗАПРЕТ и эле.ментов ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Юдицкий С. А. К синтезу микропрограммных управляющих устройств, сб. Пневмоавтоматика, М., «Наука, 1972, с. 3.

2.Авторское свидетельство СССР

№ 415642, кл. G 05 В 19/18, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство микропрограммного управления | 1981 |

|

SU1003086A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для отладки программ | 1983 |

|

SU1322290A2 |

| Устройство для контроля канала ввода-вы-ВОдА ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU840869A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Устройство микропрограммного управления | 1984 |

|

SU1265770A1 |

Авторы

Даты

1981-03-15—Публикация

1978-07-18—Подача