Изобретение относится к вычислительной технике и может быть использовано при построении устройств сопряжения с вычислительными устройствами, функционирующими в системе остаточных классов (СОК), а также в аппаратуре передачи данных, использующей коды СОК,

Цель изобретения - повышение быст- родействия.

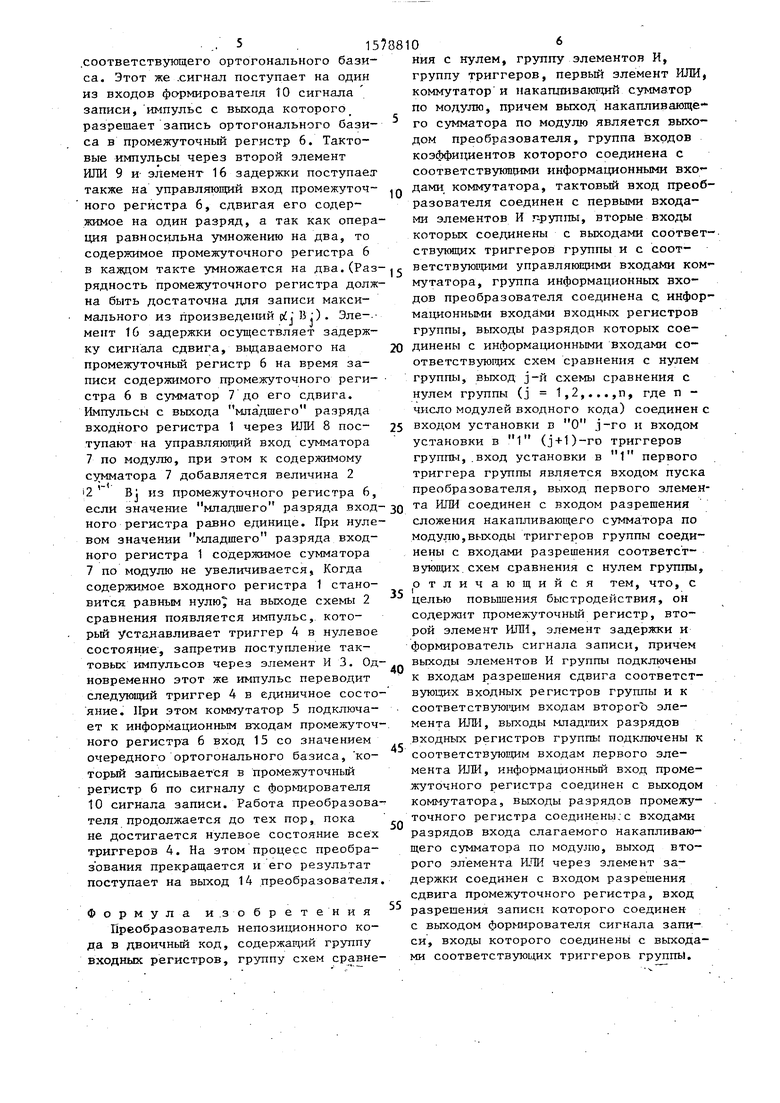

На чертеже представлена схема предлагаемого преобразователя непозиционного кода в двоичный код.

Преобразователь содержит группу входных регистров 1, группу схем 2 сравнения с нулем, группу элементов ИЗ, группу триггеров 4, коммутатор 5 э промежуточный регистр 6, накапливающий сумматор 7 по модулю, первый и второй элементы ИЛИ 8 и 9, формирователь 10 сигнала записи, группу информационных входов 11 преобразователя, вход 12 пуска преобразователя, тактовый вход 13 преобразователя, выход 14 преобразователя, группу входов 15 ко™ эбфициентов преобразователя и элемент 16 з адержки.

Преобразователь работает следующим образомо

В качестве алгоритма функционирования используется метод преобразования с помощью ортогональных базисов, согласно которому число Л, представленно остатками ь(( , 2,„.., tfn, в позиционной системе представляется как

А О/, В , + и,,, Вг+... +оЈпВп, (1)

где В - ортогональные базисы СОК;

п - количество оснований Р. СОК, 1 по которым представлено ис- ходное число.

Запишем выражение (1) в виде n w;

А Ј, Ха | 2

i-i

В

4(2)

где Ј- количество двоичных

разрядов для представления исходного числа в СОК по основанию; J С ближайшее большее 50

целое;

а- 0,1 - значение двоичного разряда входных регистров.

Из выражения (2) видно, что преоб- 55 разователь реализует операцию последовательного суммирования произведений ортогональных базисов на веса соотQ

. ,

35

45

50

55 ветствующих двоичных разрядов, представляющих вычеты исходного числа в СОК.

Входные регистры 1 группы и промежуточный регистр 6 являются сдвиговыми, причем содержимое входных регистров 1 группы в каждом такте сдвигается в сторону младших, а промежуточного регистра 6 -- в сторону старших разрядов на один разряд.

В исходном состоянии сумматор 7 по модулю и промежуточный регистр 6 о§- нулены, триггеры 4 установлены в нулевое состояние. Остатки о/, , Ы2,...., ci по входам 11 заносятся во входные регистры 1. Сдвиг информации и ее выдача со стороны младших разрядов входных регистров 1 группы разрешается только по поступлению импульсов на их управляющие входы. Схемы 2 сравнения группы производят сравнение содержимого соответствующих входных регистров 1 группы с нулем и выдают сигнал при их обнулении. Вследствие того,что все триггеры 4 установлены в нулевые состояния, нулевые потенциалы на их выходах, прикладываемые к управляющим входам схем 2 сравнения, запрещают появление rfa выходах сигналов сравнения с нулем, тем самым предотвращаются ложные запуски триггеров 4 в случае равенства хотя бы одного из остатков Ы нулю.

Посде подготовки преобразователя к работе на вход 12 поступает импульс запуска, который переводит триггер 4 в единичное состояние, разрешая тем самым сравнение содержимого регистра 1 с нулем. Если значение остатка по основанию Р равно нулю, то сразу же по приходу разрешающего сигнала с триггера 4 на выходе 2 появляется сигнал, который сбрасывает триггер 4 в нулевое и переводит следующий триггер 4 в единичное состояние. Если значение первого остатка не равно нулю,то открывается элемент И 3 сигналом с триггера 4, и тактовые импульсы с входа 13 поступают на управляющий в-ход входного регистра 1 группы. Каждый тактовый импульс сдвигает содержимое входного регистра 1 на один разряд. Одновременно управляющий сигнал с триггера 4 поступает на первый вход коммутатора 5, который подключает к информационным входам промежуточного регистра 6 группу входов 15 коэффициентов. На эти входы подается значение

соответствующего ортогонального базиса. Этот же сигнал поступает на один из входов формирователя ТО сигнала записи, импульс с выхода которого разрешает запись ортогонального базиса в промежуточный регистр 6. Тактовые импульсы через второй элемент ИЛИ 9 и элемент 16 задержки поступает также на управляющий вход промежуточного регистра б, сдвигая его содержимое на один разряд, а так как операция равносильна умножению на два, то

ния с нулем, группу элементов И, группу триггеров, первый элемент ИЛИ, коммутатор и накапливающий сумматор по модулю, причем выход накапливающее го сумматора по модулю является выходом преобразователя, группа входов коэффициентов которого соединена с соответствующими информационными входами коммутатора, тактовый вход преобразователя соединен с первыми входами элементов И г-руппы, вторые входы которых соединены с выходами соответствующих триггеров группы и с соотсодержимое промежуточного регистра 6 в каждом такте умножается на два.(Раз-, ветствующими управляющими входами ком- рядность промежуточного регистра долж- мутатора, группа информационных вхо- на быть достаточна для записи максидов преобразователя соединена с. информационными входами входных регистров группы, выходы разрядов которых соемального из произведешш vi В :) . Элемент 16 задержки осуществляет задержку сигнала сдвига, выдаваемого на промежуточный регистр 6 на время записи содержимого промежуточного регистра 6 в сумматор 7 до его сдвига. Импульсы с выхода младшего разряда входного регистра 1 через ИЛИ 8 поступают на управляющий вход сумматора 7 по модулю, при этом к содержимому сумматора 7 добавляется величина 2 2 Bj из промежуточного регистра 6,

дов преобразователя соединена с. инфо мационными входами входных регистров группы, выходы разрядов которых сое20 динены с информационными входами соответствующих схем сравнения с нулем группы, выход j-й схемы сравнения с нулем группы (j 1,2,...,n, где п - число модулей входного кода) соединен

25 входом установки в О j-ro и входом установки в 1 (j+1)-ro триггеров группы, вход установки в 1 первого триггера группы является входом пуск преобразователя, выход первого элеме

35

40

если значение младшего разряда вход- зо та И™ соединен с входом разрешения ного регистра равно единице. При нулевом значении младшего разряда входного регистра 1 содержимое сумматора 7 по модулю не увеличивается, Когда содержимое входного регистра 1 становится равным нулю на выходе схемы 2 сравнения появляется импульс, который устанавливает триггер 4 в нулевое состояние, запретив поступление тактовых импульсов через элемент И 3. Одновременно этот же импульс переводит следующий триггер 4 в единичное состояние. При этом коммутатор 5 подключает к информационным входам промежуточного регистра 6 вход 15 со значением очередного ортогонального базиса, который записывается в промежуточный регистр 6 по сигналу с формирователя 10 сигнала записи. Работа преобразователя продолжается до тех пор, пока не достигается нулевое состояние всех триггеров 4. На этом процесс преобразования прекращается и его результат поступает на выход 14 преобразователя.

45

50

сложения накапливающего сумматора по модулю,выходы триггеров группы соеди нены с входами разрешения соответствующих схем сравнения с нулем группы отличающийся тем, что, с целью повышения быстродействия, он содержит промежуточный регистр, второй элемент ИЛИ, элемент задержки и формирователь сигнала записи, причем выходы элементов И группы подключены к входам разрешения сдвига соответст вующих входных регистров группы и к соответствующим входам второго элемента ИЛИ, выходы младших разрядов входных регистров группы подключены соответствующим входам первого элемента ИЛИ, информационный вход промежуточного регистра соединен с выходом коммутатора, выходы разрядов промежуточного регистра соединены.с входами разрядов входа слагаемого накапливающего сумматора по модулю, выход второго элемента ИЛИ через элемент задержки соединен с входом разрешения сдвига промежуточного регистра, вход разрешения записи которого соединен с выходом формирователя сигнала записи, входы которого соединены с выхода ми соответствующих триггеров группы.

Формула изобретения

Преобразователь непозиционного кода в двоичный код, содержащий группу входных регистров, группу схем сравне

ния с нулем, группу элементов И, группу триггеров, первый элемент ИЛИ, коммутатор и накапливающий сумматор по модулю, причем выход накапливающее го сумматора по модулю является выходом преобразователя, группа входов коэффициентов которого соединена с соответствующими информационными входами коммутатора, тактовый вход преобразователя соединен с первыми входами элементов И г-руппы, вторые входы которых соединены с выходами соответствующих триггеров группы и с соответствующими управляющими входами ком- мутатора, группа информационных вхо-

ветствующими управляющими входами ком- мутатора, группа информационных вхо-

дов преобразователя соединена с. информационными входами входных регистров группы, выходы разрядов которых соединены с информационными входами соответствующих схем сравнения с нулем группы, выход j-й схемы сравнения с нулем группы (j 1,2,...,n, где п - число модулей входного кода) соединен с

входом установки в О j-ro и входом установки в 1 (j+1)-ro триггеров группы, вход установки в 1 первого триггера группы является входом пуска преобразователя, выход первого элемен5

0

о та И™ соединен с входом разрешения

5

0

5

сложения накапливающего сумматора по модулю,выходы триггеров группы соединены с входами разрешения соответствующих схем сравнения с нулем группы, отличающийся тем, что, с целью повышения быстродействия, он содержит промежуточный регистр, второй элемент ИЛИ, элемент задержки и формирователь сигнала записи, причем выходы элементов И группы подключены к входам разрешения сдвига соответствующих входных регистров группы и к соответствующим входам второго элемента ИЛИ, выходы младших разрядов входных регистров группы подключены к соответствующим входам первого элемента ИЛИ, информационный вход промежуточного регистра соединен с выходом коммутатора, выходы разрядов промежуточного регистра соединены.с входами разрядов входа слагаемого накапливающего сумматора по модулю, выход второго элемента ИЛИ через элемент задержки соединен с входом разрешения сдвига промежуточного регистра, вход разрешения записи которого соединен с выходом формирователя сигнала записи, входы которого соединены с выходами соответствующих триггеров группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Преобразователь кодов | 1987 |

|

SU1450112A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Преобразователь кода | 1989 |

|

SU1619401A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

Изобретение относится к вычислительной технике, работающей в системе остаточных классов. Цель изобретения - повышение быстродействия преобразователя. Преобразователь содержит группу входных регистров 1, группу схем 2 сравнения с нулем, группу элементов И 3, группу триггеров 4, коммутатор 5, промежуточный регистр 6, накапливающий сумматор 7 по модулю, первый и второй элементы ИЛИ 8 и 9, формирователь 10 сигнала записи, группу информационных входов 11 преобразователя, вход 12 пуска преобразователя, тактовый вход 13 преобразователя, выход 14 преобразователя, группу входов 15 коэффициентов преобразователя, элемент 16 задержки. Группа входных регистров 1 и промежуточный регистр 6 являются сдвиговыми. Во входные регистры 1 заносятся остатки преобразуемого числа, после запуска преобразователя содержимое первого входного регистра 1 сдвигается в сторону "младших" разрядов. В промежуточный регистр 6 записывается значение ортогонального базиса, которое в каждом такте сдвигается на один разряд в сторону "старших" разрядов. Значение содержимого промежуточного регистра 6 поступает в сумматор 7, если значение "младшего" разряда входного регистра 1 равно единице. При нулевом значении "младшего" разряда входного регистра содержимое сумматора 7 по модулю не увеличивается. Процесс преобразования заканчивается после того, как содержимое всех входных регистров 1 обнулится. 1 ил.

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-15—Публикация

1988-08-25—Подача