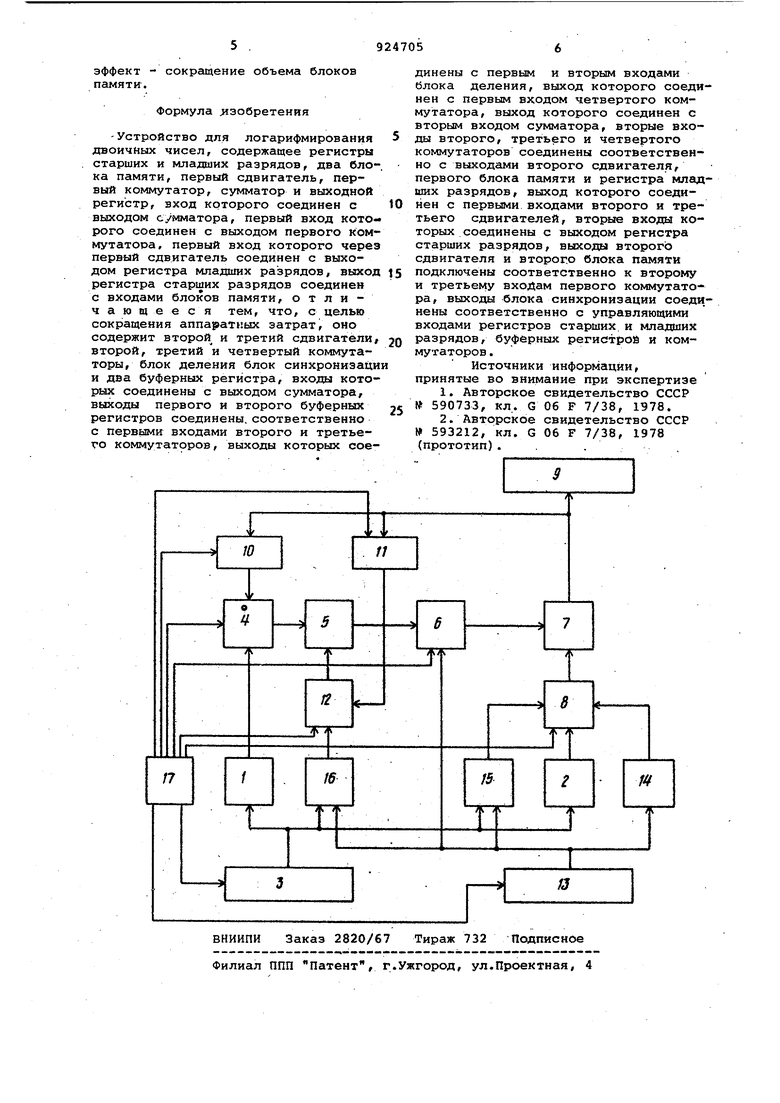

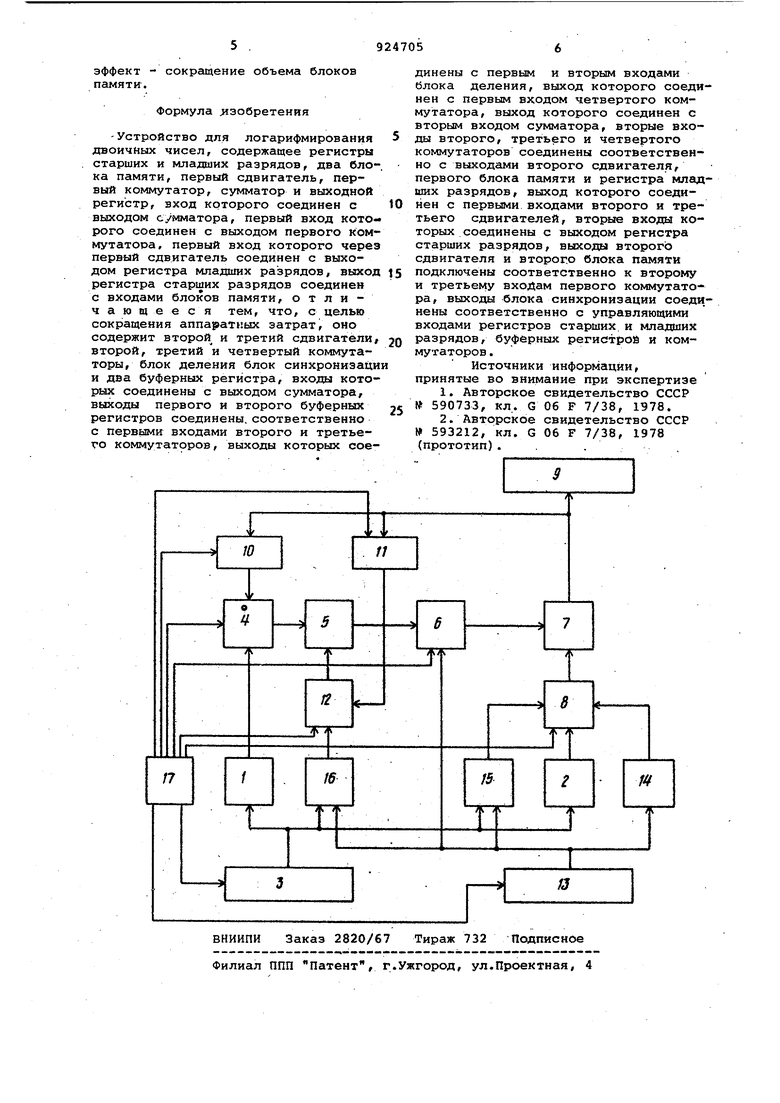

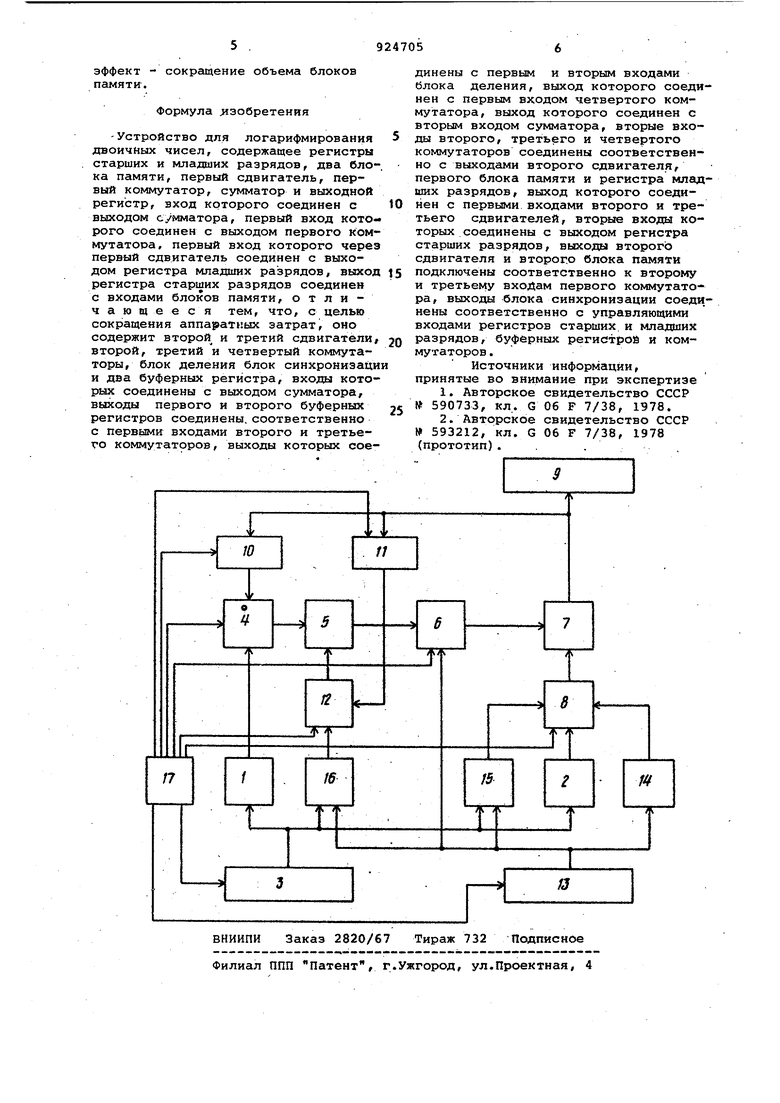

Изобретение относится к вычислительной технике и может быть исполь зовано в качестве цифрового генератора значений логарифмической функции. Известно устройство, содержащее регистры числа и результата, блок деления, схему сравнения, накопител сдвиговый регистр и блок управления 1 . Недостатком данного устройства является низкое быстродействие. Наиболее близким по технической сущности к предлагаемому является устройство для логарифглирювания дво ичных чисел, которое содержит регис старших разрядов аргумента, соединенный с адресными входами двух бло ков памяти и регистр младших разря дов аргумента, выход которого через сдвисЬтель, первый коммутатор и .сум матор подключен к выходному регистру 12. Недостатком известного устройства является большой объем постоянной памяти, требуемой для хранения таблиц коэффициентов что существен но сужает область применения подобных устройств и позволяет использовать их лишь в малоразрядных ЦВМ (не более 12 - 16 разрядов). Для аргумента длиной 24 двоичных разряда объем таблиц составляет 119.2 . бит., что не позволяет применять данное устройство в качестве узла универсальных ЭВМ. Цель изобретения - сокращение аппаратных затрат. Поставленная цель достигается тем, что в устройство, содержащее регистры старших и младших разрядов, два блока памяти, первый сдвигатель, первый коммутатор, сумматор и выходной регистр, вход которого соединен с выходом сумматора, первый вход которого соединен с выходом первого коммутатора, первый вход которого через первый сдвигатель соединен с выходом регистра младших разрядов, выход регистра старших разрядов соединен с входами блоков памяти, содержит второй и третий сдвигатели, второй, третий и четвертый коммута- : торы, блок деления, блок синхронизации и два буферных регистра, входы которых соединены с выходом сумматора, выходы первого и второго буферных регистров соединены соответственно с первыми входами второго и третьего коммутаторов, выходы которых соединены с первым и вторым вх дами блока деления, выход которого соединен с первым входом четвертого коммутатора, выход которого соединен с вторым входом сумматора, втор входы второго, третьего и четвертого коммутаторов соединены соответст венно с выходами второго сдвигателя первого блока памяти и регистра млад ших разрядов, выход которого соедине с первыми входами второго л третьего сдвигателей, вторые входы которых соединены с выходом регистра старших разрядов, выходы второго сдвига теля и второго блока памяти подклю чены соответственно к второму и третьему входам первого коммутатора выходы блока синхронизации соединены соответственно с управляющими входами регистров старших и младших разрядов, буферных регистров и коммутаторов. Вычисление натурального логарифм от нормализованного аргумента X (1/2 v X 1) производится в предлагаемом устройстве на основе еледующих соотношений L пХ cir U(x) , где. u(,x)enX(j4 - Здесь Хд - опорная часть аргумента, представленная k старшими разрядами аргумента, а дх - приращение аргумента, представленное n-k-двоичными разрядами, где п - общее количество разрядов требуемого для представления аргумента X. Значения Еп XgU-l , зависящие только от опорной части аргумента, вычисляются предварительно и заносятся в таблицы, реализованные на блоках постоянной памяти. Значение параметра k для получения верными всех п двоичных разрядо результата необходимо при этом взять из выражения k Г(п - 1)/ST. Расчеты, проведенные при , показывают, что потребуется хранить лишь 32 константы длиной 24 разряда Таким образом, для рассмотренного устройства по сравнению с устройством-прототипом получается йыигрыш в объеме блоков памяти более чем в 300 раз. На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит блоки 1 и 2 , регистр 3 старших разрядов , коммутатор 4, блок 5 деле ния, коммутатор 6, сумматор 7, коммутатор 8, выходной регистр 9 результата, регистры 10 и 11 буферные, коммутатор 12, регистр 13 младших разрядов (аргумента), сдвигатели 14 - 16, блок 17 синхронизации. Сдвигатели 15 и 1ё реализуют операции 4Xo+iXr +ЛХ соответственно, которые заключаются в добавлении между старшими и младшими разрядами аргумента соответствующего числа нулей (двух и одного). Устройство для логарифмирования двоичных чисел работает следующим образом. В первом такте по сигналу с блока синхронизации 17 адрес XQ, передаваемый с выхода регистра старших разрядов аргумента 3,поступает на входы блоков памяти 1 и 2, на выходах этих блоков памяти появляются соответственно значения - 2 Х и пХр, а на выходах сдвигателей 15 и 16 - соответственно значения 4X(j+ + ЛХ и 2X0 +ДХ. Значения 2Х с выхода первого блока 1 памяти через коммутатор 4 по сигналу с блока 17 поступает на вход делимого блока 5 деления, значение 2Х Q +л X с выхода сдвигателя 16 через коммутатор 12 по сигналу с блока 17, поступает на вход делителя блока 5 деления, на выходе которого образуется промежуточный результат Pjf -2Xg/ /(2Х о + дХ) . Одновременно с этим значение ДХ с выхода регистра младших разрядов аргумента 13 через коммутатор б по сигналу с блока 17 поступает на второй вход сумматора 7,на первый вход которого поступает значение 24Х, образованное на выходе сдвигателя 14, передаваемое через коммутатор 8, по сигналу с блока 17. Результат, равный ЗдХ запоминается в буферном регистре 10. Во втором такте по управляющим сигналам с блока синхронизации 17 происходит сложение промежуточного результата Р, поступающего на сумматор 7 через коммутатор 6, и значения 4Хо + дХ, поступающего с выхода сдвигателя 15 через коммутатор 8 на вход сумматора 7. Промежуточный результат- Р/2 4Х0 + лХ + Р/1 запоминается на втором буферном регистре. В третьем такте значения ЗдХ с выхода буферного регистра 10 через коммутатор 4. поступает на вход делимого блока 5 деления, промежуточный результат Р с выхода буферного регистра 11 через коммутатор 12 поступает на вход делителя блока 5 деления. Промежуточный результат Р 5 ЗДХ/Р(2 с выхода блока 5 деления через коммутатор б передается на вход сумматора 7. На другой вход последнего поступает значение с выхода второго блока 2 памяти, передаваемое на сумматор 7 через коммутатор 8. Результат Р ВпХо+ Pj с выхода сумматора 7 поступает на вход регистра результата 9.. . Таким образом, предлагаемое устройство обеспечивает положительный

эффект - сокращение объема блоков памяти.

Формула лзобретения

- Устройство для логарифмирования двоичных чисел, содержащее регистры старших и младших разрядов, два блока памяти, первый сдвигатель, первый коммутатор, сумматор и выходной регистр, вход которого соединен с выходом сумматора, первый вход которого соединен с выходом первого коммутатора, первый вход которого через первый сдвигатель соединен с выходом регистра младших разрядов, выход регистра старших разрядов соединен с входами блоков памяти, отличающееся тем, что, с целью сокращения аппаратных затрат, оно содержит второй и третий сдвигатели второй, третий и четвертый коммутаторы, блок деления блок синхронизаци и два буферных регистра, входы которых соединены с выходом сумматора, выходы первого и второго буферных регистров соединены, соответственно с первыми входами второго и третьего коммутаторов, выходы которых соединены с первым и вторым входами блока деления, выход которого соединен с первым входом четвертого коммутатора, выход которого соединен с вторым входом сумматора, вторые входы второго, третьего и четвертого коммутаторов соединены соответственно с выходами второго сдвигателя, первого блока памяти и регистра младших разрядов, выход которого соединен с первыми входами второго и третьего сдвигателей, вторые входы которых соединены с выходом регистра старших разрядов, выходы второго сдвигателя и второго блока памя1ги подключены соответственно к второму и третьему входам первого коммутатора, выходы блока синхронизации соединены соответственно с управляющими входами регистров старших и младших разрядов, буферных регистров и коммутаторов .

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 590733, кл. G Об F 7/38, 1978.

2.Авторское свидетельство СССР 593212, кл. G 06 F 7/38, 1978 (прототип). . .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логарифмирования двоичных чисел | 1981 |

|

SU1059572A1 |

| Множительное устройство | 1978 |

|

SU824206A1 |

| Устройство для вычисления функций двух переменных | 1983 |

|

SU1123034A1 |

| Устройство для вычисления функций | 1984 |

|

SU1206767A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1236465A1 |

| Цифровое устройство для воспроизве-дЕНия фуНКций | 1979 |

|

SU809126A1 |

| Устройство для логарифмирования массивов двоичных чисел | 1979 |

|

SU926654A1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Функциональный преобразователь | 1983 |

|

SU1126968A1 |

Авторы

Даты

1982-04-30—Публикация

1980-07-30—Подача