(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВОИЧНЫХ ЧИСЕЛ В ДОПОЛНИТЕЛЬНЫХ КОДАХ

ды регистров множимого и множителя соединены с входными шинами множимого и множителя устройства соответственно, выход регистра множимого соединен со вторым входом этого регистра, выход элемента И соединен с нервым входом узла суммирования, выход узла суммирования соединен со входом регистра результата, выход регистра результата с выходной шиной результата устройства и со вторым входом узла суммирования, введены триггер модификации сдвига и два нреобразователя кода в дополнительный, причем выход регистра множимого подключен к установочному входу триггера модификации сдвига, управляющий вход которого соединен с управляющим входом устройства, выходы триггера модификации сдвига и регистра множителя с информационными входами первого и второго преобразователей кода в дополнительный соответственно, управляющие входы которых соединены с выходом знакового разряда регистра множителя, выходы первого и второго преобразователей кода в дополнительный соединены с первым и вторым входами элемента И соответственно.

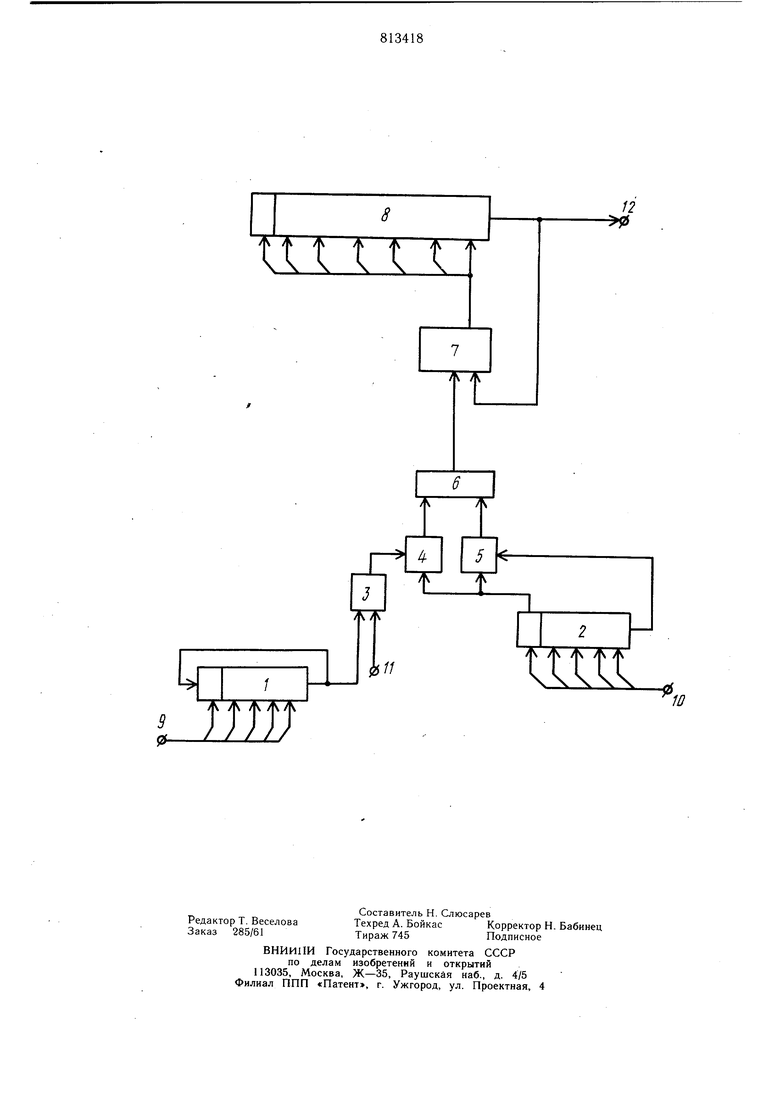

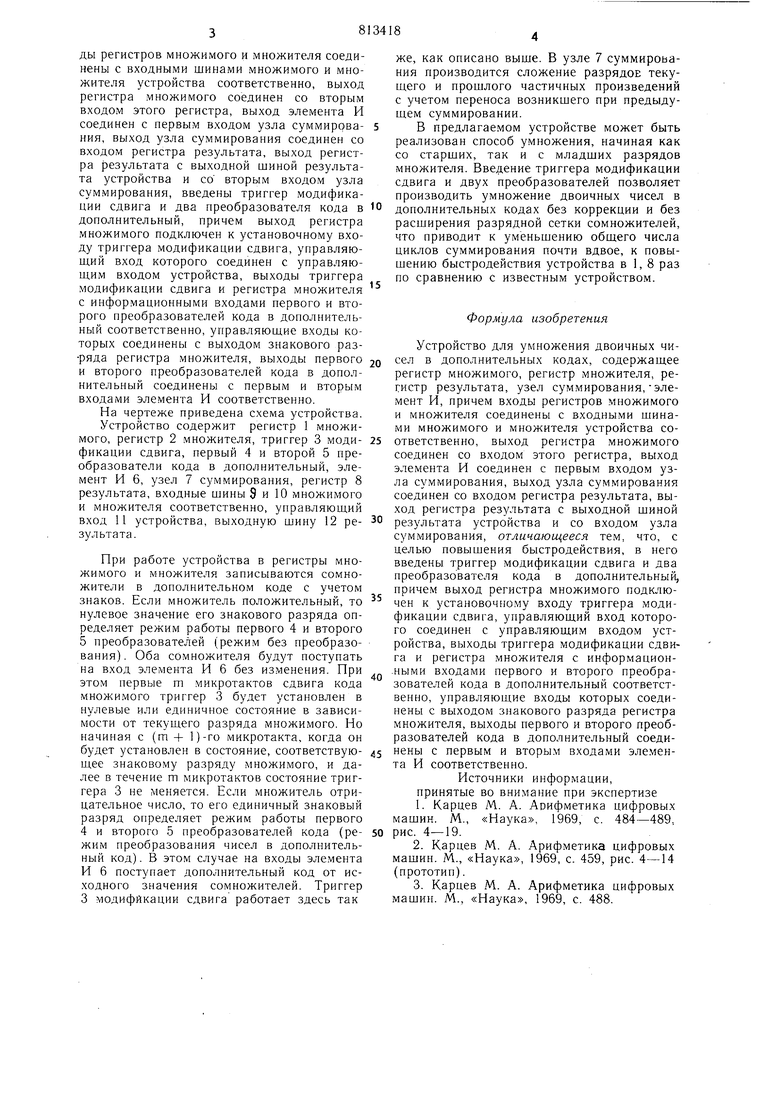

На чертеже приведена схема устройства.

Устройство содержит регистр 1 множимого, регистр 2 множителя, триггер 3 модификации сдвига, первый 4 и второй 5 преобразователи кода в дополнительный, элемент И 6, узел 7 суммирования, регистр 8 результата, входные щины 9 и 10 множимого и множителя соответственно, управляющий вход 11 устройства, выходную щину 12 результата.

При работе устройства в регистры множимого и множителя записываются сомножители в дополнительном коде с учетом знаков. Если множитель положительный, то нулевое значение его знакового разряда определяет режим работы первого 4 и второго 5 преобразователей (режим без преобразования) . Оба сомножителя будут поступать на вход элемента И 6 без изменения. При этом первые m микротактов сдвига кода множимого триггер 3 будет установлен в нулевые или единичное состояние в зависимости от текущего разряда множимого. Но начиная с (т + 1)-го микротакта, когда он будет установлен в состояние, соответствующее знаковому разряду множимого, и далее в течение ш микротактов состояние триггера 3 не меняется. Если множитель отрицательное число, то его единичный знаковый разряд определяет режим работы первого 4 и второго 5 преобразователей кода (режим преобразования чисел в дополнительный код). В этом случае на входы элемента И 6 поступает дополнительный код от исходного значения сомножителей. Триггер 3 модификации сдвига работает здесь так

же, как описано выще. В узле 7 суммирования производится сложение разрядов текущего и прощлого частичных произведений с учетом переноса возникщего при предыдущем суммировании.

В предлагаемом устройстве может быть реализован способ умножения, начиная как со старщих, так и с младщих разрядов множителя. Введение триггера модификации сдвига и двух преобразователей позволяет производить умножение двоичных чисел в дополнительных кодах без коррекции и без расщирения разрядной сетки сомножителей, что приводит к уменьщению общего числа циклов суммирования почти вдвое, к повышению быстродействия устройства в 1, 8 раз по сравнению с известным устройством.

Формула изобретения

Устройство для умножения двоичных чисел в дополнительных кодах, содержащее регистр множимого, регистр множителя, регистр результата, узел суммирования, элемент И, причем входы регистров множимого и множителя соединены с входными шинами множимого и множителя устройства соответственно, выход регистра множимого соединен со входом этого регистра, выход элемента И соединен с первым входом узла суммирования, выход узла суммирования соединен со входом регистра результата, выход регистра результата с выходной щиной результата устройства и со входом узла суммирования, отличающееся тем, что, с целью повышения быстродействия, в него введены триггер модификации сдвига и два преобразователя кода в дополнительный, причем выход регистра множимого подключен к установочному входу триггера модификации сдвига, управляющий вход которого соединен с управляющим входом устройства, выходы триггера модификации сдвига и регистра множителя с информацион-ными входами первого и второго преобразователей кода в дополнительный соответственно, управляющие входы которых соединены с выходом знакового разряда регистра множителя, выходы первого и второго преобразователей кода в дополнительный соединены с первым и вторым входами элемента И соответственно.

Источники информации,

принятые во внимание при экспертизе

1.Карцев М. А. Арифметика цифровых машин. М., «Наука, 1969, с. 484-489, рис. 4-19.

2.Карцев М. А. Арифметика цифровых машин. М., «Наука, 1969, с. 459, рис. 4-14 (прототип).

3.Карцев М. А. Арифметика цифровых мащин. М., «Наука, 1969, с. 488.

Ж А Ж А А

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чиселВ дОпОлНиТЕльНыХ КОдАХ | 1978 |

|

SU822181A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU932489A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU550637A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Устройство для умножения двоичных чисел | 1978 |

|

SU748412A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

А А А Ж А

0ff Лч ж А

.

/

Авторы

Даты

1981-03-15—Публикация

1978-08-21—Подача