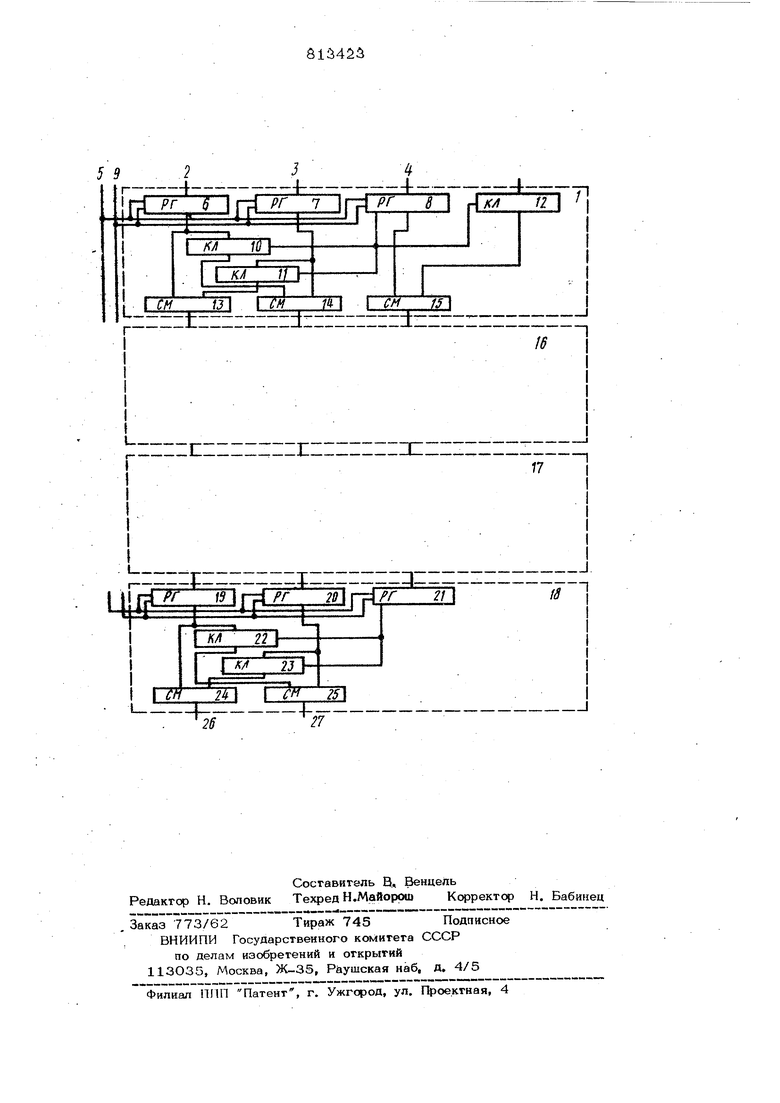

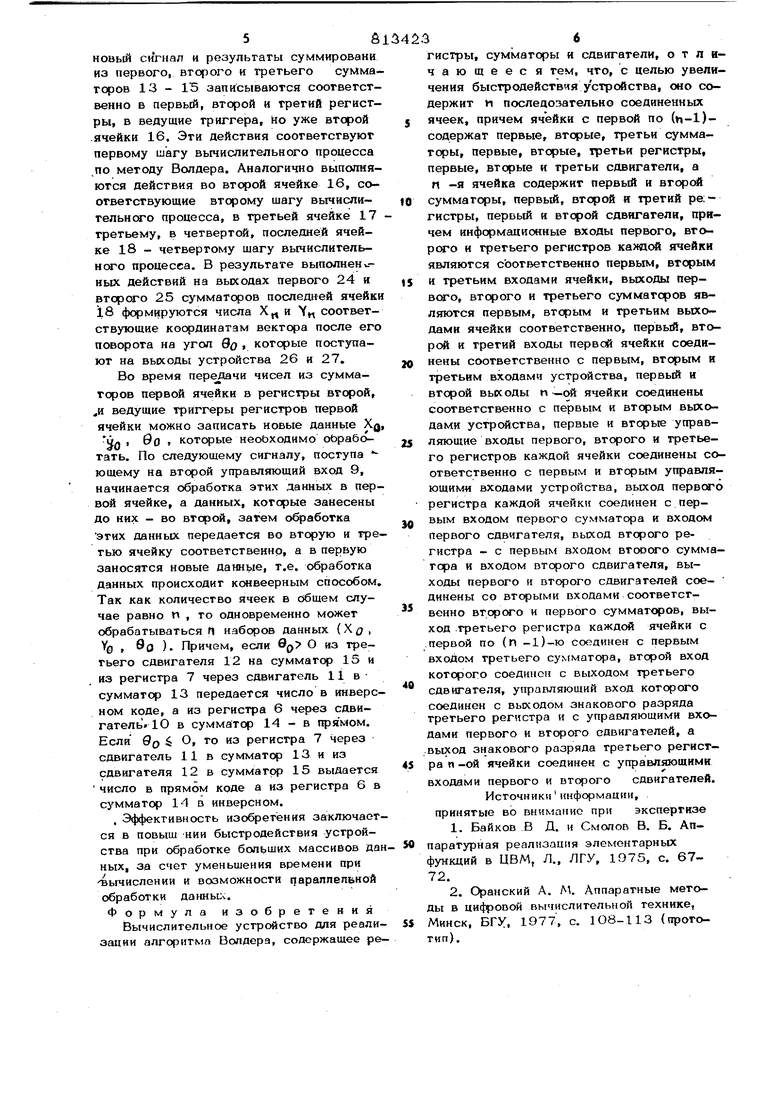

Изобретение относится к вычиспигёпь ной технике и можег быть использовано цифровых вычислительных машинах для вычисления элементарных функций. Известны устройства, выполняющие преобразование координат вектора 1фи его повороте на угол QO по методу Волдера, заключающемуся в итеративном процессе, состоящем из п шагов, каждый шаг которого есть , . .9i.9,-, . V-N.,-V,-.,r . где номер шага, изменяющийся от 1 до п, Хд ,YO - исходные координаты вектора до его поворота, X щие координаты вектора во время выпол нения поворота, Хр , УП - конечные координаты вектора после его поворота, 1Ъ arci{ - 1, Недостатками устройств является низ кое быстродействие, вследствие тсно, что каждое новое данное можно начать обрабатывать только после того, как закончена обработка предыдущего. Известно вычислительное устройство параллельно-параллельнсио типа, содержащее сумматс ы, регистры и запоминающее устройство для хранения констант fl Недостатком устройства является малое быстродействие при обработке больших массивов данных. Наиболее близким к предлагаемому является арифметическое устройство, соCTOHJiee из одной ячейки, содержащей три сумматора параллельного действия, два сдвигающих регистра с параллельными приемом и выдачей информации, выполняющие сдвиг информации вправо, трех параллельных регистров и ПЗУ для хранения констант 2j. Недостатком арифметического устройства является малое быстродействие при обработке большого количества данных в невозможность обработки новых данных до окончания обработки предыдущих. Цель изобретения - увеличение быстродействия вычислительнсяго устройства, раJбогаюшего по методу Волдера при обработке большого количества данных. Поставленная цель достигается тем, что вычислительное устройство, содержащее регистры, сумматоры и сдвигатели, состоит из п последовательно соединенных ячеек, причем каждая из первых )ячеек содержит первый, второй и третий сумматоры, первый, втсфой и fpe(гий регистры, первый, второй и третий сдвигатели, а ц -ая ячейка содержит первый и второй сумматоры, первый, вто рой и третий регистры, первый и второй сдвигатели I причем информационные входы первого второго и третьего регистров каждой ячейки являются соответственно первым, вторым и третьим входами ячейки, выходы первого, второго и третьего сумматоров являются первым, вторым и третьим .выходами ячейки со ответственно, первый, втфой и третий входы первой ячейки соединены соответственно с первым, втсрым и третьим вхо дами устройства, аервый и второй выход л -ой ячейки соединены-соответственно с первыми вторым вьвсодами устройства, первые и вторые управляющий входы пер вото, второго и третьего регистров каждой ячейки соединены соответственно с первым и вторым управляющими входами устройства, выход первого регистра каждой ячейки соединен с первым входом первого сумматора и входом первого сдв гателя, а вькод второго регистра - с первым входом втсрого сумматора и вхо дом второго сдвигателя, выходы первого и второго сдвигателей соединены со вто рыми входами соответственно второго и первого сумматоров, вЬгходы третьего ре гистра каждой из первых (и -1) ячеек соединены с первым входом третьего сумматора, второй вход которого соединен с выходом третьего сдвигателя, уп- равляющий вход которого соединен с вы ходом знакового разряда Третьего регис ра и с управляющими входами первого и второго сдвигателей, а выход знаково го разряда третьего регистра н-ой ячей ки соединен с управляющими входами первого и второго сдвигателей. На чертеже представлена функционал ная схема вычислктеяьнсно устройства, состоящего из четырех ячеек. Устройство содержит первую ячейку 1, входы которой соединены с первым, вторым и третьим входами 2, 3 и 4 устройства, первый управляющий вход 5 устройства, соединенный с первыми управляющими входами регистров 6-8, 3 входящих в состав первой ячейки 1, вторые управляющие входы которьЬс соединены со вторым управляющим входом 9устройства. Ячейка содержит также сдвигатели 10-12 и cyMiviaTOpbi 13-15, Все последующие ячейки 16 и 17, кроме последней (п-ой) ячейки 18 выполнены аналогично ячейке 1. -ая ячейка содержит первый, второй и третий регистры 19 -21, первый и второй сдвигатели 22 и 23, аервый и второй сумматоры 24 и 25, первьй и второй . выходы устройства 26 и 27. Сдвигатели 10и 11 выполняют прямую передачу чисел из регистров в сумматоры. Соответствующие сдвигатели второй ячейки выполняют косую передачу, что равносильно арифметическому сдвигу на один разряд вправо. Сдвигатели третьей ячейки выполняют косую передачу, соответствующую арифметическому сдвигу на два разряда вправо, сдвигатели кода четвертой ячейки - на три разряда вправо. Вход третьего сдвигателя кода соединен с шиной земля или питание. Устройство работает следующим образом. На первую ячейку 1 на первьгй, второй и третий входы данных устройств 2, 3 и 4 подаются соответственно значения 0 YO . QO По сигналу, подаваемому на первый управляющий вход 5, эти значения переписываются в ведущие триггера первого, второго и третьего регистров 6,7 и 8 первой ячейки. После этого сигнал с первого управляющего входа 5 снимается, а на второй управляющий вход 9 подается, в результате чего числа из ведущих триггеров переписываются в ведомые. Затем из регистров непосредственно и через первый 1О и второй 11 сдвигатели из третьего сдвигателя 12 осуществляется подача чисел в сумматоры 1315. На первый сумматор 13 из первого регистра 6 подается ( -q;)o ИЗ второго регистра 7 через второй сДвигатсль 11, на второй сумматор 14 подается Yg , а из первого регистра 6 через периый сдвигатель 1О подается СЕ-ХО--- . На -третий сумматор 15 из третьего регистра 8 подается звТачение 00 и из третьего сдвигателя 8-значение ( (L принимает значения +1 или -1 в зависймости от знака 8у , находящегося в третьем регистре 8, Затем сигнал со второго управляющего 9 устройства снимается, а на первый управляющий вход 5 подается новый сигнал и резульгагы суммировани из первого, BTOfJoro и третьего сумма торов 13 - 15 записываются соответственно в первый, второй и третий регистры, в ведущие триггера, йо уже второй .ячейки 16. Эти действия соответствуют первому шагу вычислительного процесса по методу Волдера, Аналогично выполняются действия во второй ячейке 16, соответствующие второму шагу вьиислительного процесса, в третьей ячейке 17 третьему, в четвертой, последней ячейке 18 - четвертому шагу вычислительнсйго процесеа. В результате выполнен.ных действий на выходах первого 24 и второго 25 сумматоров последней ячейк 18 формируются числа Х и „ соответствующие координатам вектора после его поворота на угол Во . которые поступают на выходы устройства 26 и 27. Во время передачи чисел из сумматоров первой ячейки в регистры второй, J/L ведущие триггеры регистров первой ячейки можно записать новые данньте Xjj UQ , 00 , которые неоЬходимо оЬработать. По следующему сигналу, поступа ющему на второй управляющий вход 9, начинается обработка этих данных в первой ячейке, а данных, которые занесены до них - во второй, затем обработка этих данных передается во вторую и третью ячейку соответственно, а в первую заносятся новые данные, т.е. обработка данных происходит конвеерным способом, Так как количество ячеек в общем случае равно t , то одновременно может обрабатываться М наборов данных {Xj, YO ®0 ) Причем, если 9р О из третьего сдвигателя 12 на сумматор 15 и из регистра 7 через сдвигатель 11 в сумматор 13 передается число в инверсном коде, а из регистра 6 через сдвигатель.Ю в сумматор 14 - в прямом. Если QQ $ О, то из регистра 7 через сдвигатель 11 в сумматор 13 и из сдвигателя 12 в сумматор 15 выдается число в прямом коде а из регистра 6 в сумматор 14 в инверсном. , Эффективность изобретения заключается в повыш НИИ быстродействия устройства при обработке больших массивов дан ных, за счет уменьшения времени при Вычислении и возможности параппепьной обработки дafшы:. Формула изобретения Вычислительное устройство для реализации алгоритма Волдера, содержащее регистры, сумматоры и сдвигатели, отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит и последозательно соединенных ячеек, причем ячейки с первой по (-1)содержат первые, вторые, третьи сумматоры, первые, вторые, третьи регистры, первые, вторые и третьи сдвигатели, а п -я ячейка содержит первый и второй сумматоры, первый, второй и третий регистры, первый и второй сдвигатели, причем информационные входы первого, второт-о и третьего регистров кахясй ячейки являются соответственно первым, вторым и третьим входами ячейки, выходы первого, второго и третьего сумматоров являются первым, вторым и третьим выходами ячейки соответственно, первый, второй и третий входы первой ячейки соединены соответственно с первым, вторым и третьим вх одами устройства, первый и второй вькоды п -ой ячейки соединены соответственно с первьгм и вторым выходами устройства, первые и вторые управляющие входы первого, второго и третьего регистров каждой ячейки соединены соответственно с первым и вторым управляющими входами устройства, выход первого регистра каждой ячейки соединен с первым входом первого сумматора и входом первого сдвигателя, выход второго регистра - с первьгм входом втооого сумма- тара и входом второго сдвигателя, выходы первого и второго сдвигателей соединены со вторыми входами соответственно второго и первого сумматоров, выход третьего регистра каждой ячейки с первой по (п -1)-ю соединен с первым вхоДом третьего сумматора, второй вход которого соединен с выходом третьего сдвигателя, упракшяющий вход которого соединен с выходом знакового разряда третьего регистра и с управляющими вхоами первого и сдвигателей, а ыход знакового разряда третьего регист- ра п -ой ячейки соединен с управляющими входами первого и второго сдвигателей. Источникиинформации, принятые во внимание при экспертизе 1. Байков В Д. и Смолов В. Б. Ап- аратурная реализация элементарных ункций в ЦВМ, Л., ЛГУ, 1975, с. 672. 2. Оранский А, А1. Аппаратные метоы в цифровой вычислительной технике, инск, БГУ, 1977, с. 1О8-113 (протоип). 59 2 J4 .II L- j I pf 71-T / I ° ifft H I /f/ fg fl /(/f /Г f--I I CM 131 I CM 14- i fM ITZZZZtHZZIZIZZltllllllZIZltZ г 1( L., ,.i:. X--3 itiff rf j rpr г r-l / ц I I K/r 22 H- I j K/t 2Jh-I I I / I гЛ. 26 ГГ / --I 7 I -TTyf 7П / I HAVf/2 I fj- ZZrZZZZIIZZ ----- J I I I I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Устройство для вычисления элементарных функций по алгоритму Волдера | 1982 |

|

SU1068933A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

| Устройство для поворота вектора | 1983 |

|

SU1144104A1 |

| Устройство для вычисления синусно- косинусных функций | 1978 |

|

SU750495A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для умножения с накоплением комплексных чисел | 1987 |

|

SU1478211A1 |

| Вычислительное устройство для поворота вектора | 1987 |

|

SU1520511A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1035604A1 |

Авторы

Даты

1981-03-15—Публикация

1979-02-13—Подача