(54) СИСТЕМА ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи дискретной информации | 1976 |

|

SU738185A1 |

| Система передачи дискретной инфор-МАции | 1976 |

|

SU818026A1 |

| Система передачи дискретной информации | 1985 |

|

SU1262741A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

| Устройство для кодирования и декодирования сигналов в системах передачи цифровых данных | 1980 |

|

SU1046959A1 |

| Система передачи дискретной информации | 1976 |

|

SU688082A1 |

| Система для дистанционной проверки объекта по телефонной сети | 1990 |

|

SU1794278A3 |

| Устройство тактовой синхронизации | 1980 |

|

SU1008920A1 |

| Устройство для передачи и приема дискретных сигналов | 1990 |

|

SU1758894A1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

1

Изобретение относится к электросвязи и может использоваться для передачи цифровой информации.

Известна система передачи дискретной информации, содержащая на передающей стороне источник дискретной информации, и формирователь импульсного сигнала и блок синхронизации, а на приемной сторонепоследовательно соединенные линейный усилитель, блок оптимальной обработки сигнала, выпрямитель и рещающий блок, причем другой выход блока оптимальной обработки сигнала через блок формирования напряжения порога и блок восстановления границ линейных посылок подключен к другим входам режущего блока, а также потребитель дискретной информации 1.

Однако Б данной системе недостаточна пропускная способность.

Цель изобретения - повыщенле пропускной способности.

Указанная цель достигается тем, что в систему передачи дискретной информации, содержащую на передающей стороне источник дискретной информации, формирователь импульсного сигнала и блок синхронизации, а на приемной стороне - последовательно соединенные линейный усилитель, блок оптимальной обработки сигнала, выпрямитель и рещающий блок, причем другой выход блока оптимальной обработки сигнала через блок формирования напряжения порог а и блок восстановления границ, линейных посылок подключен к другим входам рещаю цего блока, а также потребитель дискретной информации, на передающей и приемной сторонах введены соответственно блок двукратного снижения скорости перео дачи и блок восстановления скорости передачи, при этом источник дискретной информации через блок двукратного снижения скорости передачи, другой вход которого соединен с выходом блока синхронизации, подключен к входу формирователя импульсно5 гб сигнала, выходы рещающего блока через блок восстановления скорости передачи подключены к входу потребителя дискретной информации, причем формирователь импульсного сигнала выполнен в виде формирователя двукратного амплитудно-разностного моноимпульсного сигнала, а решающий блок выполнен трехуровневым.

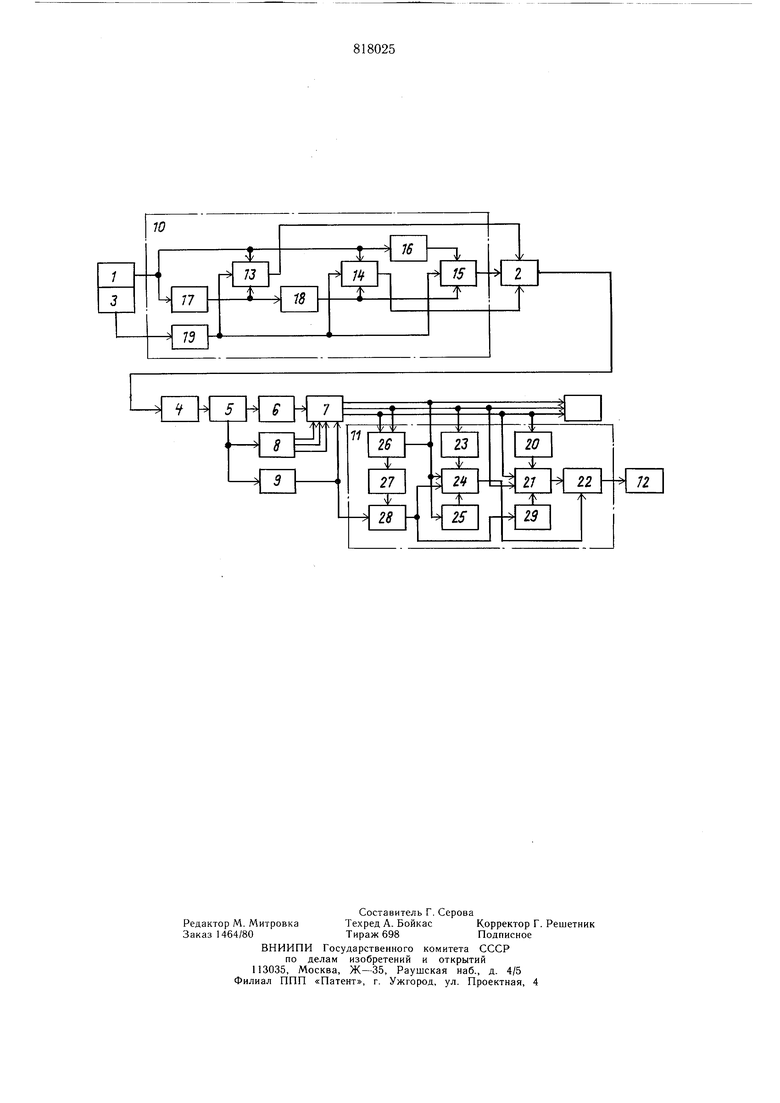

Блок двукратного снижения скорости передачи выполнен в виде трех выходных элементов И, причем выход источника дискретной информации подключен к первым входам первого и второго выходных элементов И непосредственно, к первому входу третьего выходного элемента И - через первый инвертор, а также к входу элемента задержки, выход которого подключен ко второму входу первого выходного элемента И непосредственно, а ко вторым входам второго и третьего выходных элементов И - через второй инвертор, выход блока синхронизации через делитель импульсов подключен к третьим входам выходных элементов И. Блок восстановления скорости передачи выполнен в виде последовательно соединенных первого элемента задержки, первого элемента ИЛИ и выходного триггера, другой вход которого соединен с выходом последовательно соединенных второго элемента задержки и второго элемента ИЛИ, причем первый выход трехуровневого решающего блока подключен к входу первого элемента задержки и ко второму входу первого элемента ИЛИ, второй выход трехуровневого решающего блока подключен к входу второго элемента задержки и третьему входу первого элемента ИЛИ, третий выход трехуровневого решающего блока подключен ко второму входу второго элемента ИЛИ непосредственно, к третьему входу второго элемента ИЛИ - через третий элемент задержки, а также к первому входу третьего элемента ИЛИ, два других входа которого подключены к первому и второму выходам трехуровневого решающего блока, выход третьего элемента ИЛИ через последовательно соединенные расширитель импульсов и элемент запрета подключен к четвертому входу второго элемента ИЛИ непосредственно, а к четвертому входу первого элемента ИЛИ - через четвертый элемент задержки, выход блока восстановления границ линейных посылок подключен к другому входу элемента запрета. На чертеже изображена структурная электрическая схема предлагаемой системы. Система содержит источник 1 дискретной информации, формирователь 2 импульсного сигнала, блок 3 синхронизации, линейный усилитель 4, блок 5 оптимальной обработки сигнала, выпрямитель 6, решающий блок 7, блок 8 формирования напряжения порога, блок 9 восстановления траниц линейных посылок, блок 10 двукратного снижения скорости передачи, блок 11 воестановления скорости передачи, потребитель 12 дискретной информации, причем блок 10 содержит выходные элементы 13-15 И, инвертор 16, элемент 17 задержки, инвертор 18, делитель 19 импульсов. Блок 11 восстановления скорости передачи содержит элемент 20 задержки, элемент 21 ИЛИ, выходной триггер 22, элемент 23 задержки, элемент 24 ИЛИ, элемент 25 задержки, элемент 26 ИЛИ, расширитель 27 импульсов, элемент 28 запрета, а также элемент 29 задержки. Система работает следующим образом. Цифровой сигнал источника 1 поступает в элемент 17 задержки и в инвертор 16, а задержанный сигнал - в инвертор 18. На два входа выходного элемента 13 И подается напряжение с выходов источника 1 и элемента 17 задержки. На входы выходного элемента 14 И напряжение поступает с выходов источника 1 и инвертора 18, а на входы выходного элемента 15 И - с выходов инверторов 16 и 18. Частота следования коротких импульсов блока 3 синхронизации изменяется два раза в делителе 19 импульсов и импульсы на границах вторичных рабочих посылок подаются на третьи свободные входы всех выходных элементов 13-15 И. Импульсы с выходов всех выходных элементов Й поступаю7на трй ра;лельн ьГхформирователя 2. На выходе н к F формирователя 2 создается сигнал, содержащий в относительном виде полную информацию об исходном двоичном сигнале при двукратном снижении частоты повторения вторичных рабочих посылок по сравнению с частотой рабочих посылок источника 1. поступает в линейный усили . обрабатывается в блоке 5 и выпрямителя 6 поступает в решаю„ g f д принятия решений по обработанного сигнала в блоке 8 формирования создаются три различные постоянные напряжения, а в блоке 9 восстановления формируются короткие им границах вторичных рабочих посьшокt-fРешения, принятые по максимальному, среднему и минимальному уровням обработанного сигнала поступают в элемент 26 ИЛИ,а их сумма через расширитель 27 импульсов в элементе 28 запрета запрещает совпадающие импульсы канала восстановления границ вторичных рабочих посылок. В результате этого импульсы на выходе элемента 28 запрета характеризуют прием сигнала с неизменным напряжением на двух соседних вторичных рабочих посылках. На один вход элемента 24 ИЛИ через элемент 23 задержки поступают импульсы с среднего уровня трехуровневого решлющего блока 7, на два других входа по максимального УР°« непосредственно и через элемент 25 задержки, а его четвертый вход управляется импульсами, прошедшими элемент 28 запрета. На два входа элемента 21 ИЛИ подается импульсная последовательность с выхода минимального уровня решающего блока 7, причем на один из входов импульсы поступают через элемент 20 задержки Третий вход элемента 21 ИЛИ управляется импульсами с выхода среднего уровня, а четвертый - через элемент 29 задержки импульсами элемента 28 запрета. Импульсы, возникающие на выходе элемента 24 ИЛИ, устанавливают выходной триггер 22 с раздельным запуском в состояние «1, а с выхода элемента 21 ИЛИ - в состояние «О. В результате этого на выходе выходного триггера 22 формируется сигнал, совпадающий с исходным. Увеличение длительности линейных посылок но сравнению с исходными приводит к удвоению минимальной длительности импульса линейного сигнала. Поэтому при равном объеме передаваемой информации требуется в два раза ниже верхняя граничная частота или при равной полосе частот в два раза увеличивается пропускная способность линейной связи. Формула изобретения 1. Система передачи дискретной информации, содержащая на передающей стороне источник дискретной информации, формирователь импульсного сигнала и блок синхронизации, а на приемной стороне - последовательно соединенные линейный усилитель, блок оптимальной обработки сигнала, выпрямитель и рещающий блок, причем другой выход блока оптимальной обработки сигнала через блок формирования напряжения порога и блок восстановления границ линейных посылок подключен к другим входам рещающего блока, а также потребитель дискретной информации, отличающаяся тем, что, с целью повыщения пропускной способности, на передающей и приемной сторонах введены соответственно блок двукратного снижения скорости передачи и блок восстановления скорости передачи, при этом источник дискретной информации через блок двукратного снижения скорости передачи, другой вход которого соединен с выходом блока синхронизации, подключен к входу формирователя импульсного сигнала, выходы рещающего блока через блок восстановления скорости передачи подключены к входу потребителя дискретной информации, причем формирователь импульсного сигнала выполнен в виде формирователя двукратного амплитудно-разностного моноимпульсного сигнала, а рещающий блок выполнен трехуровневым. 2. Система по п. 1, отличающаяся тем, что блок двукратного снижения скорости передачи выполнен в виде трех выходных элементов И, причем выход источника дискретной информации подключен к первым входам первого -и второго выходных элементов И непосредственно, к первому входу третьего выходного элемента И - через первый инвертор, а также к входу элемента задержки, выход которого подключен ко второму входу первого выходного элемента И непосредственно, а ко вторым входам второго и третьего выходных элементов И - через второй инвертор, выход блока синхронизации через делитель импульсов подключен к третьим входам выходных элементов И. 3. Система по пп. I и 2, отличающаяся тем, что блок восстановления скорости передачи выполнен в виде последовательно соединенных первого элемента задержки, первого элемента ИЛИ и выходного триггера, другой вход которого соединен с выходом последовательно соединенных второго элемента задержки и второго элемента ИЛИ, причем первый выход трехуровневого рещающего блока подключен к входу первого элемента задержки и ко второму входу первого элемента ИЛИ, второй выход трехуровневого рещающего блока подключеен к входу второго элемента задержки и третьему входу первого элемента ИЛИ, третий выход трехуровневого решающего блока подключен ко второму входу второго элемента ИЛИ непосредственно, к третьему входу второго элемента ИЛИ - через третий элемент задержки, а также к первому входу третьего элемента ИЛИ, два других вхоД которого подключены к первому и второму выходам трехуровневого рещающего блока, выход третьего элемента ИЛИ через последовательно соединенные расщиритель импульсов и элемент запрета подключен к четвертому входу второго элемента ИЛИ непосредственно, а к четвертому входу первого элемента ИЛИ - через четвертый элемент задержки, выход блока восстановления границ линейных посылок подключен к другому входу элемента запрета. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 524469, кл. Н 04 L 27/22, 1973 (прототип).

Авторы

Даты

1981-03-30—Публикация

1976-05-20—Подача