1

Изобретение относится к вычисли,тельной технике и может быть применено, например, в цифровых однородных сеточных моделях для решения уравнения теплопроводности.

Известно устройство для решения дифференциальных уравнений, содержащее сумматоры, блоки умножения, блок задержки, регистр, элементы И 1 .

Недостатком этого устройства является низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для решения уравнения теплопроводности, содержащее сумматор, блок умножения, регистр результата, блоки шаговой перекоммутации 21.

Недостатком данного устройства также является низкое быстродействие

Цель изобретения - повышение быстродействия.

Поставленная цель достигается те что в устройство содержащее регистр результата, выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу первого блока элементов И, первый вход которого соединен с выходом первого регистра, второй вход блока элементов и является первым входом устройства, дополнительно введены второй, третий, четвертый и пятый блоки элементов И, второй, третий,четвертый и пятый регистры и шифратор, причем выходы :второго-, третьего, четвертого и пятого регистров подключены соответственно к первым входам одноименных блоков элементов И, выходы

0 второго, третьего, четвертого и пятого блоков элементов И соединены соответственно с третьим, четвертым пятым и шестым входами сукматора, выходы всех разрядов которого соеди5нены со входом регистра результата, выходы трех старших разрядов сумматора соединены со входом шифратора, выход которого является выходом устройства, вторые входы второго, тре0тьего, четвертого и пятого блоков элементов И являются соответственно вторым, третьим,четвертым и пятым входами устройства, второй вход регистра результата является седьмым

5 входом устройства.

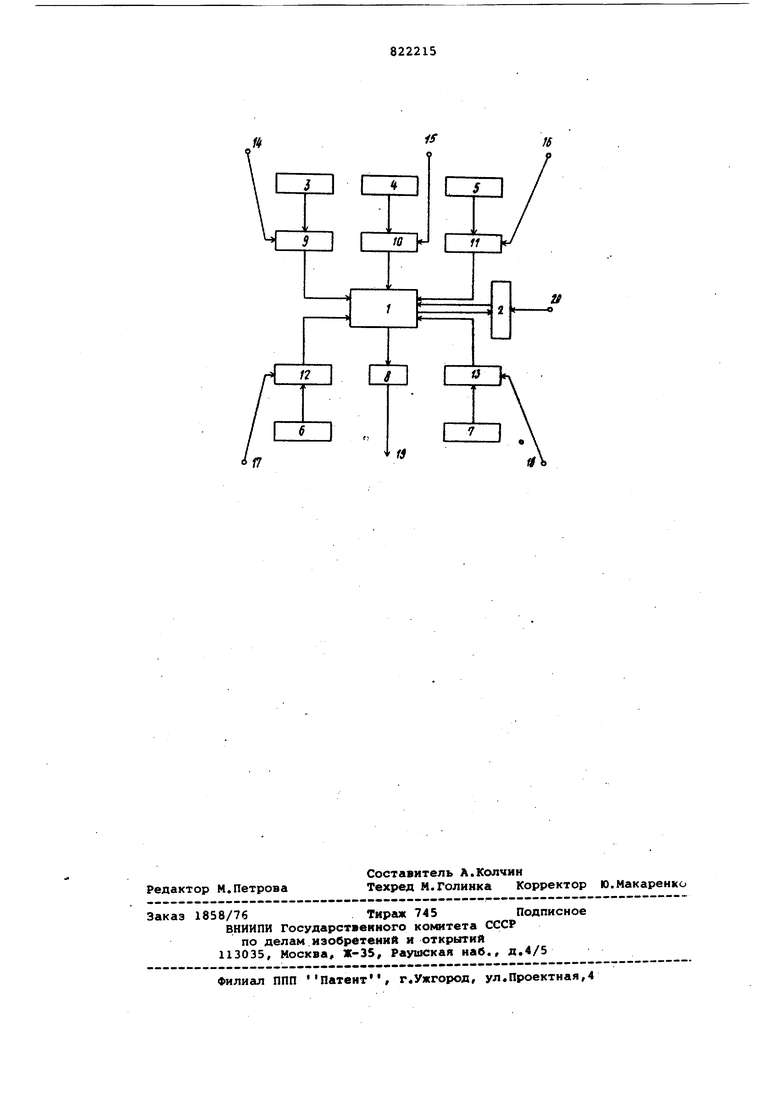

На чертеже схематически представлено предлагаемое устройство.

Устройство содержит сукиатор 1, регистр 2 результата, регистры 3-7,

0

шифратор 8, блоки элементов И 9-13, входы 14-18, выход 19 и вход 20.

Устройство работает следующим образом.

Шифратор 8 представляет собой комбинационуую схему, содержащую логические элементы, связанные между собой в соответствии с системой переключательных функций:

f4 aHatva3), (ajv а),

где индексы аргументов соответствуют номерам разрядов сумматора 1, а номера функций - номерам выходов шифратора- 8. В исходном состоянии (цепи установки исходного состояния на чертеже не показаны) в регистры 2-7 кгикдого i-ro устройства записывается значение коэффициентов уравнения теплопроводности.

В каждом -ом цикле вычислений на ишны 14-16 i-ro устройства цоступают цифры операндов УД ,У , У-. , имеющие вес 2 и принимающие значения из множества l,0,lj, где к - число разрядов, после которых фиксируется запятая. Эти цифры управляют выдачей содержимого регистров 3-5 на сумматор 1 таким образом, что на сумматор 1 выдаются прямые коды регистров 3-5, если соответствующие цифры равны плюс единице дополнительные коды, .если соответствующие цифры равны минус единице, и коды регистров 3-5 не выдаются, если соответствующие цифры равны нулю. Шифратор 8, анализируя содержимое трех старших разрядов сумматора 1, формирует цифру результата, которая поступает на выходную шину 19 и описанным способом управляет выдачей кода регистра б в i+1-ом устройстве и кода регистра 7 в i-1-ом устройстве.Цифра результата Ч имеет вес р, равна плюс единице,если на выходе трех старших разрядов сумматора 1 001 игч 010,минус единица - если на выходе указанных разрядов 110 или 101 остальных случаях цифра результата равна нулю. После окончания переходного процесса в схеме следует сигнал в тактирующей шине 20, по кэторому коды сформированные на выходах сумматоров 1 принимаются на регистры результата 2.

Предлагаемое устройство по сравнению с известными обладает большим быстродействием.

Формула изобретения

Устройство для решения уравнения

теплопроводности, содержащее регистр, результата, выход которого соединен с первым входом сумматора, второй вход которого подключен к выходу первого блока элементов И, первый вход

5 которого соединен с выходом первого регистра, второй вход блока элементов И является первым входом устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство дополнительно введены второй, третий, четвертый и пятый блоки элементов И, второй, третий, четвертый и пятый регистры и шифратор, причем выходы второго, третьего, четвертого и пятого регистров подключены соответственно к первым входам одноименных блоков элементов И, выходы второго, третьего, четвертого и пятого блоков элементов И соединены соответственно

с третьим, четвертым, пятым и шестым входами сумматора, выходы всех разрядов которого соединены со входом регистра результата, выходы трёх старших разрядов сумматора соединены со входом шифратора, выход которого является выходом устройства, вторые входы второго, третьего, четвертого и пятого блоков элементов И являют-, ся соответственно вторым, третьим, 0 четвертым и пятым входами устройства, второй вход регистра результата является седьмым входом устройства.

Источники информации, 5 принятые во внимание при экспертизе

1.Авторское свидетельство СССР

633025,. кл. G 06 F 15/32, 1977.

2.Авторское свидетельство СССР 0 373735, кл. О Об G 7/56, 1971

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления интегра-лОВ | 1976 |

|

SU840901A1 |

| Устройство для преобразования координат | 1980 |

|

SU898426A1 |

| Устройство для преобразования избыточного двоичного кода в код со смешанным основанием | 1975 |

|

SU618737A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для нормализации чисел | 1980 |

|

SU953636A1 |

| Конвейерный сумматор | 1983 |

|

SU1137460A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

| Устройство для вычисления квадратного корня | 1985 |

|

SU1254477A1 |

| Устройство для ввода информации | 1983 |

|

SU1092486A1 |

Авторы

Даты

1981-04-15—Публикация

1979-06-19—Подача