Изобретение относится к области авгo faтики и вычислительной техники и может быть применено в устройствах с использованием различных систем счисления.

Известно устройство для преобразования кодов, содержащее сдвиговые ригистрьг на статических триггерах и логические блоки коррекции ij.

Однако такое устройство позволяет выполнять преобразование только неиэбыточных двоичных чисел.

Наиболее близким техническим решением к изобретению является устройство для преобразования кодов 2j , содержащее П последовательно соединенных сдвиговых регистров, h блоков коррекции.

Первый вход i -го ( i 2 - h ) блока коррекции соединен с выходом старше го разряда ( 1 - i )-го сдвигового per стра, а первый вьгход i -го блока коррекции - с управляющим входом i -го сдвигового регистра. Выход И -го сдвигового регистра соединен с первым входом первого блока коррекции. Первый

выход блока управления соединен со вхо- ,дами сдвига всех регистров сдвига.

Недостатком этого устройства является отсутствие возможности преобразования исходного кода в код со смешанным произвольно заданным основанием. Предлагаемое устройство отличается тем, что в него пополнительно введены fl сумматоров связанных с соответствуюшимн сдвиговыми регистрами, П регистров основания, выходы которых соединены с информационнь7ми входами соответствующих сумматоров, элемент ИЛИ, входы которого соединены с выходами первого блока коррекции, триггер исходного состояния и три элемента И. Первые входы элементов И соединены со вторым выходом блока управления, вторые входы первого и второго элемента И

соединены с единичным и нулевым выхо дом триггера исходного состояния ссответственво, третьи входы соединены с входной шинсй приема положительной единицы, а выходы - со входами сложения

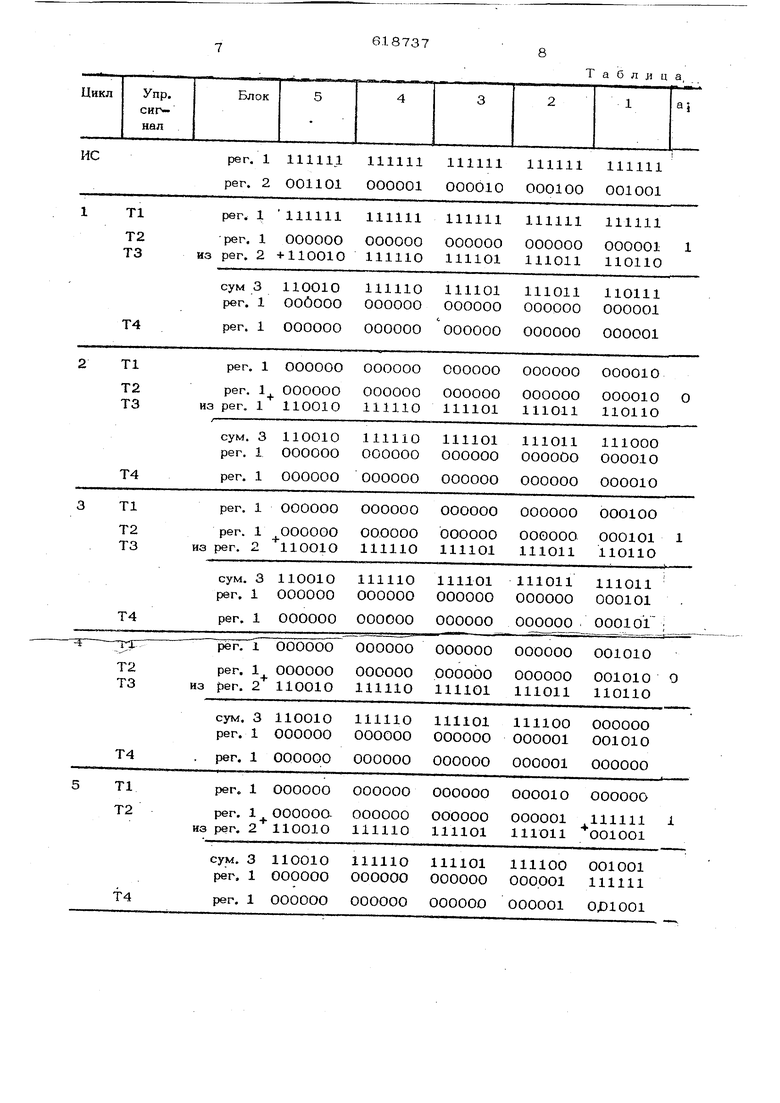

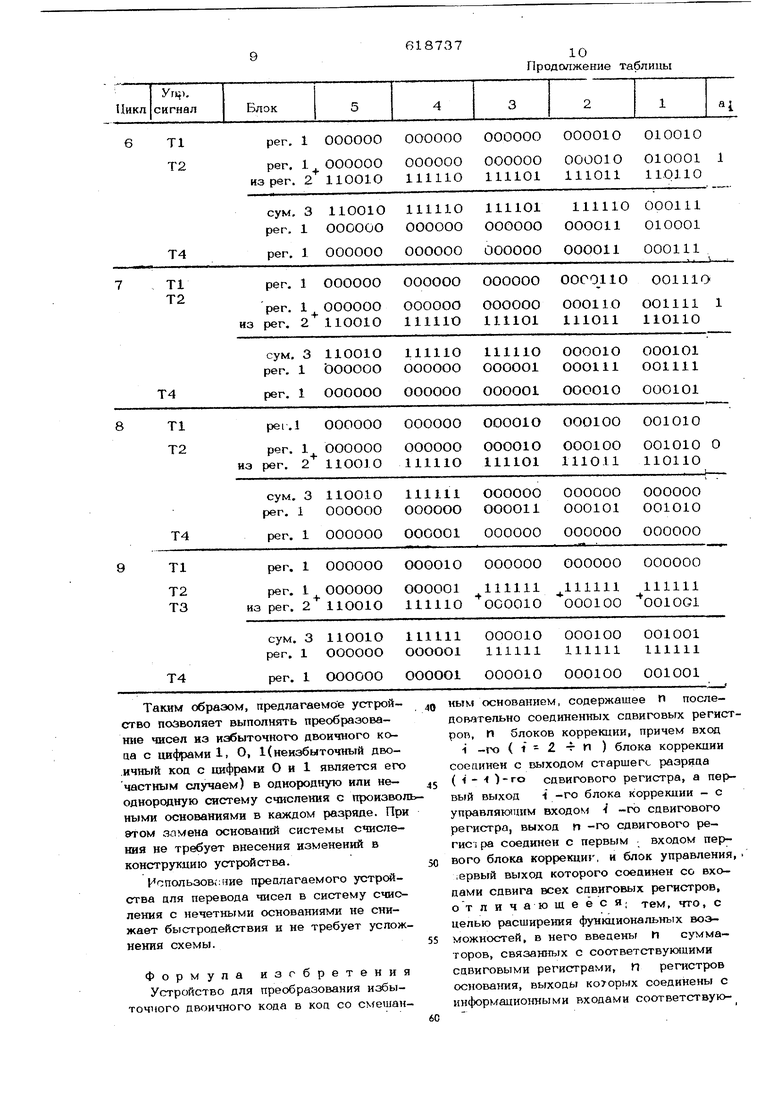

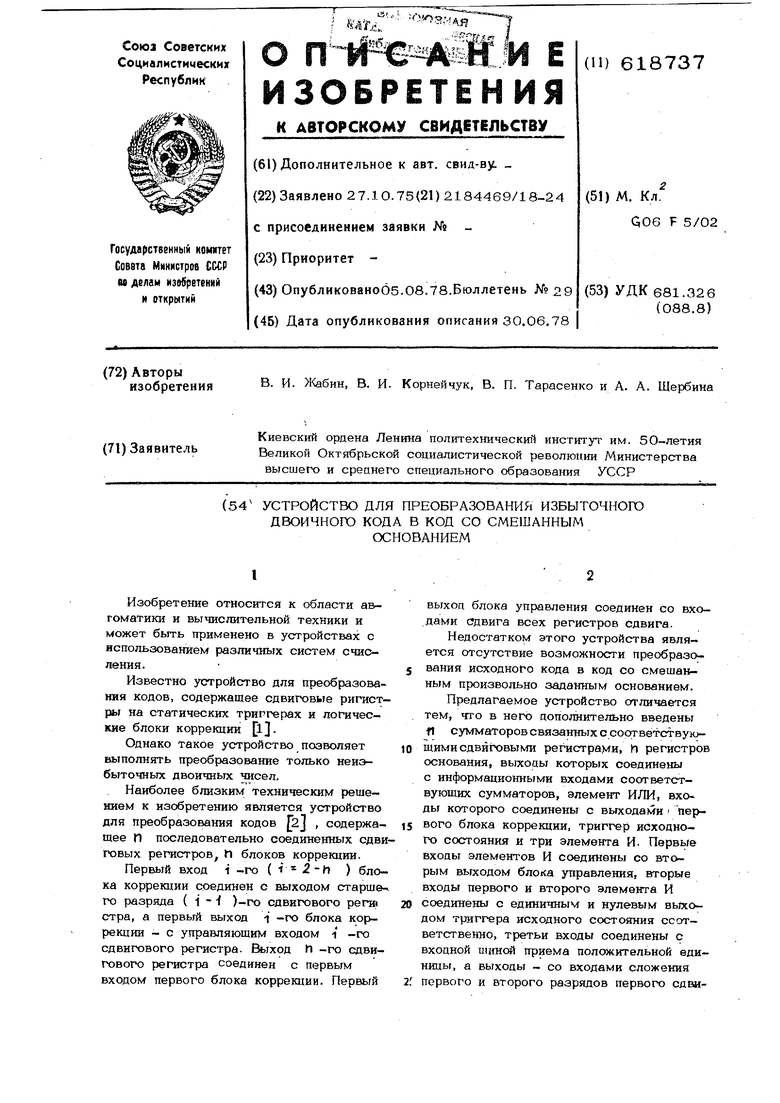

первого и второго разрядов первого сдви3.6 roDoro регистра соответствет о. Второй вход третьего элемента И соединен с входной шиной приема отрицательной еди ницы а выход - со входом вычитаггая первого сдвигового регистра. Выход старшего разряда i -го ( ( - и ) и сумматора соединен со вторым входом i -го блока коррекции, выход переполне ния 1 -го сумматора ( 1 - t -г и ) сое динен с третьим входом ( i 4 )-го блока коррекции, второй выход которого соединен с входом первого разряда ( i + i )- го сумматора. Выход старш го разряда i -го сдвигового регистра . ( 1 -1 -f П ) соединен со входом прямой или инверсной передачи регистра основания. Выход старшего разряда h-го сдвигового регистра соединен, кроме того, с четвертыми входами всех блоков коррекции и с первым входом первого блока коррекции. Входы передачи кодов всех сдвиговых регистров и всех регистров оснований соединены с третьим выходом блока управления, четЪертый выход которого соединен с пятыми входами всех блоков коррекции. Шестой BXOii 1 -го блока коррекции ( 1 « 2 -г п) соединен с третьим выходом ( 1 - ) - го блока коррекции Третий выход второго блока коррекции соединен со входом первого разряда первого .cy vfMaTOpa. Выход переполнения П - Го сумматора соединен с шестым входом ц -го блока коррекции и третьим входом первого блока коррекции. Структурная :схема предлагаемого устройства приведена на чертеже. Устройство содержит Л последовател но соедш1енных сдвиговых регистров 1, имеюыци цепи сдвига влево на один разряд и обладаюших свойствами реверсивных счетчиков, П регистров основания 2 и Ц комбинационных су.лматоров 3. Выходы кадкаждого -t -го регистра 1 и 2 связаны со входами i -го сумматора 3, выходы которого соединены со входами -го регистра 1. Выход старшего разряда i -го регистра 1 подключен к управляющему входу i -го регистра 2. Устройство также содержит И блоков коррекции 4, триггер исходного состояния 5, элемент ИЛИ 6 л элементы 7-9. Блок управления 10 размешен вне устройства, и его первый выход подключен к цепям сдвига регистров 1, второй выход соединен с управляющими входами элементов И 7.-9, а третий - с цепями выдачи кода всех регистров 1 и 2 и с шиной установки в триггера 5, нулевой выход которого подключен ко вхо74ду элемента И 7, а единичный - к элементу И 8. Выходы этих элементов связаны с пер15ыми управляющими входами соответственно второго и первого разрядов первого регистра 1. Второй управляющий вход первого разряда этого регистра соедииен с выходом элемента И 9, Первая входная шина преобразователя кода подключены ко входам элементов И 7 и 8, а вторая - ко входу элемента И 9. Каждый блок коррекции 4 реализует систему ура внений -,, 2 Ъ i,S- -X4VX, 4 а 2МХр-Х)У Х(Х, ), V причем для каждого J -го ( d - 3,4 «. I ) блока коррекции входами соответственно являются выход старшего разряда d -го сумматора 3, выход старшего разр$ща ( - Y ) -го регистре 1, шина переноса из старшего разряда ( j --/ ) -го сумматора 3, выхоц старшего разряда П -го регистра 1, четвертый выход блока управления 10 и пятый выход / -го блока коррекции (для 77 -го блока коррекции входом Xg служит шина переноса из старТиего П -го сумматора З).. Выходы f f. и f j каждого i -го блока коррекции подключень к соответствующим управляющим входам -го регистра 1, выход f4 связан с шиной пэреноса в младший разряд J/ -го сумматора 3, а к шине переноса в младший разряд первого сумматора 3 подведен выход f-. второго блока коррекции. Входами первого блока коррекции соответственно являются выход старшего разряда пррвого сумматор, 3, выход старшего разряда П - го регистра 1, шина переноса из старшего разряда h -го сумматора 3, выход старшего разряда И -го регистра 1 и четвертый выход блока управления 1О, Выходы f, и f первого блока коррекции подключения ко входам элемента ИЛИ 6, а выход f g - к трет .ему управляющему входу первого регистра 1. Остальные входы и выходы первого блока коррекции схемы не задействованы. Следует заметить, чго сигналы, подающиеся на входы всех блоков ко| рекции и на управляющий вход регистров 2, не зависят от цепей выдачи кода иэ регистров. В исходном состоянии (цепи установки исходного ссхзтоянмя на чертеже не показаны) во всех разрядах регистров 1 записаны единицы триггер 5 находится в cocTosmHji 0, вкаждом «-ом регистре 2 записано число -1, основания основание i -и цифры. Чисгдело раэряцов в каждом 1 -ом регист ре 1, регистре 2 и сумматоре 3 должно удовлетворять условию. e,,,p; и может быть разным.для разных i В каждом цикле на вход устройства поступает очередная цифра двоичного числа. Наличие сигнала на первой входнсй шине означает, что принимаемая цифра равна 1, наличие сигнала на вторсй входной шине, что пpини аемая цифра равна Т, нулю соответствует отсутствие сигналов на обеих входных шинах. В каждом цикле вычесления блок управле ия 10 выра6aTFi)BaeT последовательность из четырех управляющих сигналов Т1, Т2, ТЗ, Т4 (номер сигнала соответствует хода блока управления 10). По сигналу Т1 осуществляется сдвиг влево на орин разряд содержимого регистров 1. СигналТ2 поступает на входы элементов И 7-9 и разрешает прием очередно цифры преобразуемогхэч-сла, который заключается в том, что в первый регистр 1 прибавляется или вычитается единица. Причем если в первом цикле принимается цифра равна 1, то она прибавляется ко второму разряду первого регистря 1, поскольку триггер 5 находится в состоянии О. В дальнейшем прием очередных цифр 1 происходит ггутём прйбавлё вия ёйкнйцьг вттерВБтйгрн э ряд первого регистра 1, так как следующий упр1авляюш.ий сигнал ТЗ в -первом же такте: устанавливает триггер 5 в сос тояние 1 . Прием цифры I всегда соетоит в вычитании единицы из первого разряда первого регистра 1. По сигналу ТЗ осуществляется выдача на сумматоры 3 содержимого всех регистров 1 и 2, причем если в з«аковом разряде -го регистра 1 записана единица, тосодержимое 1 -го регистра 2 передается на сумматор 3 6 7 в прямом коде, а если нуль, то в обратном. Во время суммирования работа блоков коррекции состоит в том, что они либо объединяют отдельные; сумматоры 3, охватывая их единой цепочкой циклического переноса из стг,ршего разряда в младший в случае, если значение знаковых (старижх) разрядов соответствующих им решстров 1 совпадает со значением знака всего числа (старшего разряда П -го регистра ij, либо наоборот разоб111ают сумматоры 3, охватывая каждый из них собственной цепочкой циклического переноса ( в с;дчае,еспи знак всего числа и знак регистра 1, соответствующего данному сумматору, различны). Кроме того, во время суммирования к содержимому i -го регистра 1 может прибавляться единица по сигналу ., , либо вычитаться едиьиця по сигналу -г° блока коррекции. С задержкой на время срабатывания сумматора 3 и регистров 1 после сигнала ТЗ блок управления 1О вырабатывает упрйвляющий сигнал Т4, который поступает на входы Хд всех блоков коррекции. При этом ,если значение старшего (знакового ) разряда 1 - го сумматора 3 совпадает со знамением старшего разряда П -го регистра 1 (знака всего числа), -1 -и блок коррекции вырабатывает сипнал IJ , по которому происходит прием кода сумматора 3 на i -И регистр.. Для выполнения преобразования необходимо выполнить m циклов, где m - разрядность двоичного числа. - -tjayj -jmfc-f .pjaj n qn f jn---ltO Mдом регистре и сумматоре преобразователя кода равно шести. Необходимо выполнить преобразование двоичного числа 1010111О1 в неоднородную систему счисления с основаниями 14, 2, 3, 5 и 10. Результатом такого перевода должно быть число 00 1249, Работа устройства для данного числового примера поясняется табл. 1, где ИС-исходное состояние, а - принимаемая цифра двоичного числа.

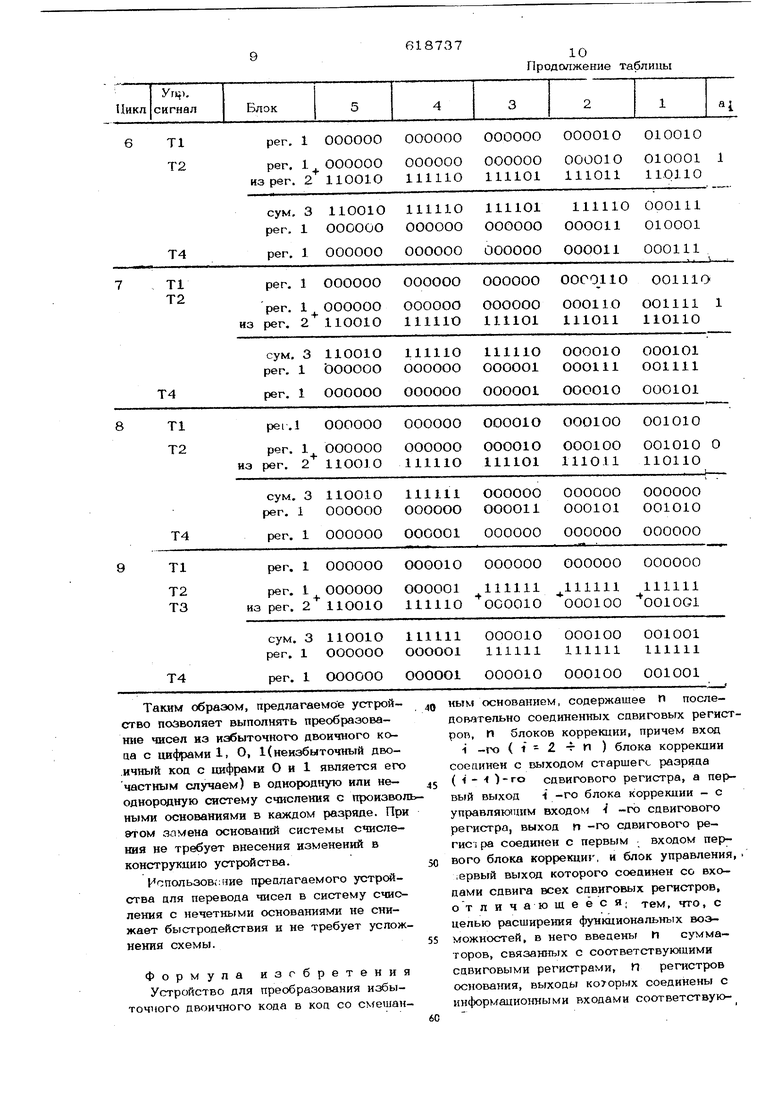

Т а б л л ц а сум. 3 11ОО1О . 1 ОООООО per. 1 ОООООО . 1 ОООООО per. 1 ОООООО Таким образом, предлагаемое устройство позволяет выполнять преобразование чисел из избыточного двоичного коца с цифрами 1, О, 1 (неизбыточный двоичный код с цифрами О и 1 является его частным случаем) в однородную или неоднородную систему счисления с произво ными основаниями в каждом разряде. При этом замена основа1шй системы счисления не требует внесения изменений в конструкцию устройства. Использование предлагаемого устройства для перевода чисел в систему счисления с нечетными основаниями не снижает быстродействия и не требует услож нения схемы. Формула изобретения Устройство для преобразования избыточного двоичного кода в коц со смешан 11 О0001О ООО1ОО ОО10О1 1 111111 111111 111111 1 111111 111111 111111 1 ОООО10 ООО100 001001 1 ОООО1О ООО1ОО ОО1ОО1 ным основанием, содержащее П последовательно соединенных сдвиговых регистров, П блоков коррекции, причем вход 1 jxj ( f 2 -г n ) блока коррекции соеаинен с выходом старшего разряда ( 1 - j-ro сдвигового регистра, а первый выход 1 -го блока коррекции - с управляющим входом -го сдвигового регистра, выход п -го сдвигового регис I ра соединен с первым входом первого блока коррекциг, и блок управления, .ервый выход которого соединен со входами сдвига всех сдвиговых регистров, от л ичающеес Я; тем, что, с целью расширения функциональных воэможностей, в него введены h сумматоров, связанных с соответствующими сдвиговыми регистрами, П репютров основатгая, выходы которых соединены с информационными входами соответствую- тих сумматоров, элемент ИЛИ, вхоаы которого соединены с вьтхопами первого блока коррекции, триггер исходного состояния и три элемента И, первые входы которых соединен со вторым выходом блока управления; вторые входы первого и второго элементов И соедине}ц с единичным и нулевым выходом триг ера исходного состояния соответсгвенло, -третьи входы соединены с входной шиной приема положительной един1шы, а выходы - со входами сложения первого и второго разрядов первого сдвигового регистра соответственно; второй вход третьего элемента И соединен с входной шиной приема отрицательной единицы, а выход - с входом вычитания первого сдви гового регистра; выход старшего разряда ) -го ( -t « -f т П ) сумматора соединен со вторым входом 1 -го блока коррекции, выход переполнения i -го сумматора { 1 - 1 -г п ) через трепй вход и второй выход (-1 -f ) -го блока кор- регахии соединен о входом первого разряна ( i + i ) -го сумматора; выход старшего разряп -го сдвигового регистра ( -J е -f 4 П ) соединен со входом 6 37 прямой или инверсной передачи регистра основания; BL ход старшего разряда П -го сдвигового регистра соединен с четвертыми входами всех блоков корре1сции и с первым входом первого блока коррекции; входы передачи кодов всех сдвиговых регистров и всех регистров оснований соединены с третьим выходом блока управления, четвертый выход которого соединен с пятыми входа- ми Ьсех блоков коррекции, шестой вход j -го блока коррекции ( 1 2 П ) соецинен с третьим выходом ( i - -/ )го коррекции; третий выход второ- г: шока коррекции соединен с входом пьрвого разряда первого сумматора; выход переполнения И -го сумматора соедш ен с шестым входом п -го блока коррекции и третьим входом первого блока корреюши. Исто--ники информации, принятые во внимание при экспертизе. 1. Авторское свидетельство СССР МЬ 144642, кл. G06 F 5/02, 1965, 2- Патент Шликобритагпш № 1257075, кл. Cj 4 А, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Устройство для умножения п-разрядных чисел,представленных последовательным кодом | 1975 |

|

SU631919A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСя-ТичНОгО B дВОичНый | 1979 |

|

SU809155A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь двоичного кода в двоично-десятичный и двоично-десятичного в двоичный | 1979 |

|

SU860051A1 |

Авторы

Даты

1978-08-05—Публикация

1975-10-27—Подача