(54) ЦИФРОВОЙ ИНТЕГРАТОР

первый выход которого является выходом положительных приращений интеграла интегратора, сумматор приращений интеграла, первый вход которого является положительной независимой переменной интегратора, выход счетчика подключен к информационному входу сумматора подынтегральной функ .ции, выход которого соединен со входом регистра подынтегральной функции первый выход которого подключен к первому входу сумматора подынтегральной функции, второй шлход подключен к информационному входу сумматора положительных приращений интеграла, выход которого подключен к первому входу регистра положительных приращений интеграла, второй вход которого подключен ко второму входу cyNffl aTopa положительных приращений интеграла, введены регистр отрицательных приращений интеграла и сумматор отрицательных прираще Ий интеграла, причем первый вход сумматора отрицательных приращений интеграла подключен к второму шлходу регистра подынтегральной функции,вход отрицательной независимой переменной интегратора подключен к входу сброса регистра положительных приращений интеграла и к второму входу cvMvjaTopa отрицательных приращений интеп ал,а, выход которого соединен с первым входом регистра отрицательных приращений интеграла, вход сброса которого соединен с входом положительной независимой переменной интегратора, первый выход регистра отрицательных приращений интеграла подключен к выходу отрицательных приращений интеграла интегратора, второй выход - к третьему входу сумматора отрицательных приращений интеграла.

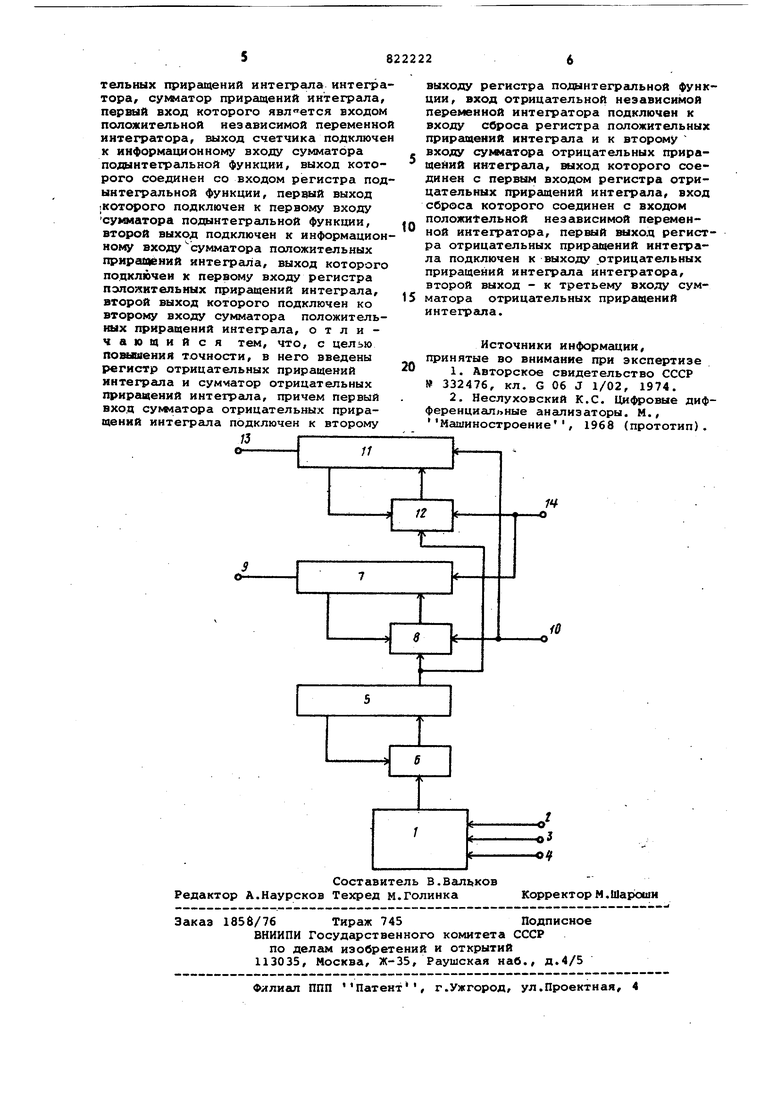

На чертеже представлена блок-схема цифрового интегратора.

Интегратор содержит счетчик 1, входы 2,3 и 4 приращений подынтегральной функции, регистр 5 и сумматор б подынтегральной функции, регистр 7, сумматор 8 и выход 9 положительных приращений интеграла,вход 10 положительной независимой переменной, регистр И, сумматор 12 и выход 13 отрицательных приращений интеграла, вход 14 отрицательной независимой переменной.

Цифровой интегратор работает следующим образом.

Через входы 2,3 и 4, сЧетчик 1 и сумматор 6 в регистр 5 записывается код требуемого масштабного коэффициента, который там и хранится в течение всего процесса масштабирования Через вход 10 на положительный вход приращений сумматора 8 и на вход сброса регистра 11 поступают положительные приращения. При этом по каждому пришедшему положительному приращеиню сумматор 8 будет суммировать содержимое регистра 7 с кодом масштабного коэффициента, который поступает на информационный вход этого сумматора из регистра 5, и эти же приращения являются сигналами для регистра 11. при переполнении регистра 7, с него на выход 9 проследует одно положительное приращение, вес которого будет в i раз больше веса приращений, пришедших на вход 10, т.е. это и будет отмасштабированное на определенный масштабный коэффициент положительное приращение. При перемене знака приращений интеграла, последние поступают через вход 14 на положительный вход приращений сумматора 12 и вход сброса регистра 7. По каждому пришедшему отрицательному приращению через вход 14 на вход сброса регистра 7 поступает сигнал сброса, а сумматор 12 суммирует содержимое регистра 11 с кодом масштабного коэффициента, поступающим на информационный вход этого сумматора из регистра Ь. При переполнении регистра 11, с него на выход 13 проследует одно отрицательное приращение, вес которого в 4 раз больше веса приращений, пришедших на вход 14, т.е. это и есть отмасштабированное на определенный масштабный коэффициент отрицательное приращение.

Таким образом, масштаблый интегратор работает только с прямым кодом масштабного коэффициента, и, следовательно, ошибка масштабирования, накапливающаяся во времени и связанная с переменой знака приращений, отсутствует.

Предлагаемый ци1Йовой интегратор,. выполняющий функции масштабного интератора, при незначительных аппаратурных затратах (увеличение схемы цифрового интегратора на 2 элемента), позволяет увеличить точность вычислительных устройств. Так, при решении навигационных задач использование предлагаемого цифрового интегратора позволяет значительно точнее проводить прокладку курса судна и определение его местоположения, что в конечном итоге приводит к значительному выигрышу времени плавания, а еледовательно/к экономии жизненных и энергетических ресурсов судна.

Формула изобретения

Цифровой интегратор, содержащий счетчик, входы которого являются входами приращений подынтегральной функции интегратора, регистр подынтегральной функции и сумматор подынтегральной функции, регистр положительных приргшений интеграла, первый выход которого является выходом положи

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный преобразователь | 1981 |

|

SU1064280A1 |

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Цифровой интегратор | 1979 |

|

SU805362A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Устройство для моделирования нейрона | 1979 |

|

SU883927A2 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

Авторы

Даты

1981-04-15—Публикация

1979-07-09—Подача