1

Изобретение относится к вычислительной технике и предназначено для использования в цифровых интегри.рующих структурах.

Известен цифровой интегратор, содержащий регистр и сумматор подынтегральной функции , множительное устройство,, регистр и сумматор остатка .интеграла, схему выделения приращения и восстановления знака, коммутатор и схему блокировки знака 1.

Недостатком этого цифрового интегратора является отсутствие контроля за достоверностью функционирования, что очень важно при использовании цифровых интегрирующих структур в системах управления.

Известен также цифровой интегратор, содержащий входной блок, регистр и сумматор подынтегральной функции, блок умножения, регистр и сумматор остатка интеграла, выходной блок и стохастический переключатель.. Один вход сумматора подынтегральной функции соединен с выходом регистра подынтегральной функции, второй вход через входной блок со входной клеммой приращений

подынтегральной функции, а выход со входом стохастического переключателя и входом регистра подынтегральной функции, выход которого соединен также со вторым входом стохастического переключателя, выход которого соединен со входом блока умножения, второй вход которого соединен со входной клеммой

10 приращений переменной интегрирования, а выход - со входом сумматора остатка интеграла, второй вход которого соединён с выходом регистра остатка интеграла, а выход - со

15 входом регистра остатка интеграла и через выходной блок - с выходной клеммой интегратора 2.

Недостатком его также является отсутствие контроля за достовер20ностью функционирования.

Цель изобретения - повышение достоверности функционирования интегратора путем введения контроля промежуточных операций.

25

Поставленная цель достигается тем, что в цифровой интегратор, содержащий масштабный блок, сумматор подынтегральной функции, регистр подынтегральной функции, блок

30

умножения, сумматор остатка интеграла, регистр остатка интеграла, блок квантования, причем первый, вход сумматора подынтегральной функции подключен к выходу регистра подынтегральной функции, первый вход блока умножения подключен к первому выходу сумматора подынтегральной функции, первый вход сумматора остатка интеграла подключен к выходу блока умножения, второй вход сумматора остатка интеграла подключен к выходу регистра остатка интеграла, вход блока квантования подключен к первому выходу сумматора остатка интеграла, второй вход блока умножения является входом приращени переменной интегрирования цифрового интегратора, вход масштабного блока является входом приращения подынтегральной функции цифрового интегратора, выход блока квантования является выходом цифрового интегратора, допсэлнительно введены блок свертки приращения подынтегральной функции , блок свертки подынтегральной функции, блок свертки остатка интеграла, блок коммутации, сумматор по модулю и , счетчик по модулю d, блок сравнения, причем вход блока свертки приращения подынтегральной функции подключен к выходу масштабного блока, второй вход сумматора подынтегральной функции подключен к первому выходу блок свертки приращения подынтегральной функции, вход блока свертки подынтегральной функции подключен кПервому выходу сумматора подынтегральной функции, вход регистра подынтегральной функции подключен к первому выходу блока свертки подынтегральной функции , вход регистра остатка интеграла подключен к первому выходу блока свертки остатка интеграла, вход блока свертки остатка интеграла подключен к первому выходу сумматора остатка интеграла, первый, второй, третий, четвертый, пятый, шестой, седьмой входы блока коммутации подключены соответственно ко второму выходу блока свертки приращения подынтегральной функции, второму выходу сумматора подынтегральной функции, второму шлходу блока свертки подынтегральной функции, первому выходу сумматора подынтеграильной функции, второму выходу сумматора остатка интеграла, второму выходу блока свертки остатка интеграла, первому выходу сумматора остатка интегргша, первый вход сумматора по модулю а. подключен к первому выходу блока коммутации, вход счетчика lo модулю d подключен ко второму выходу блока коммутации, первый и второй входы блока сравнения подключены соответственно к выходу сумматора по модулю d , и выходу счетчика по модулю d , восьмой вход блока коммутации и второй вход сумматора по модулю d объединены со вторым входом блока умножения, выход блока сравнения является выхоJ дом контроля цифрового интегратора.

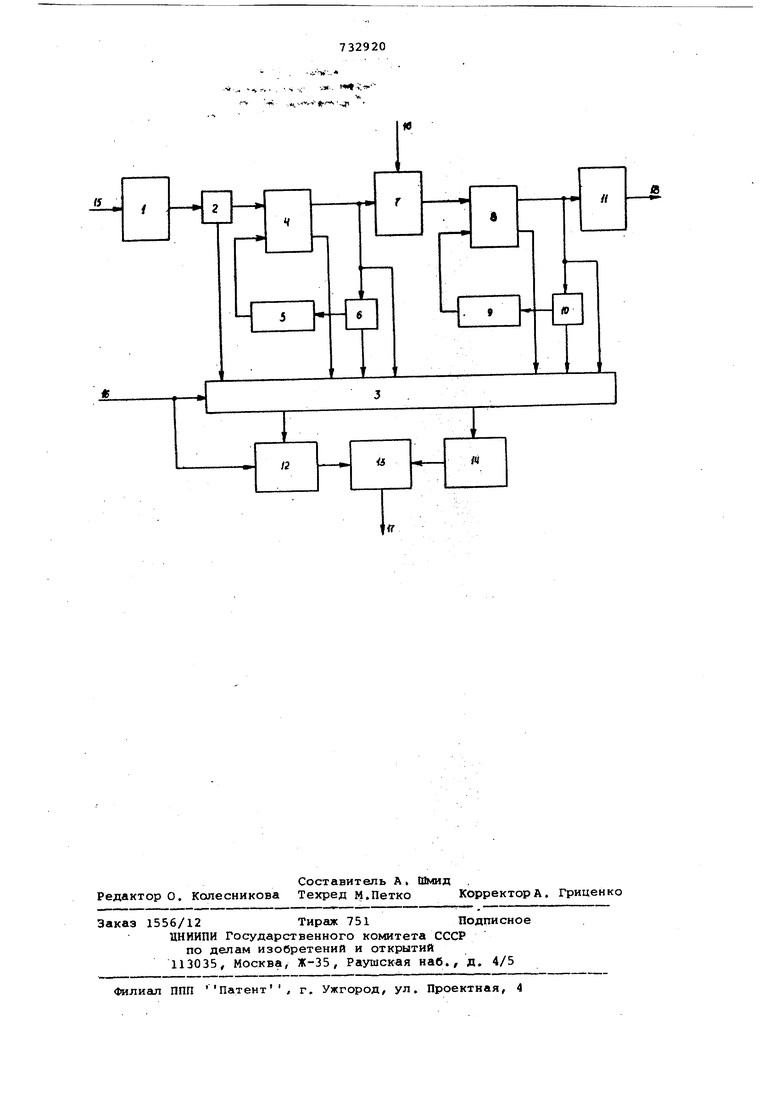

На чертеже представлена блок-схема цифрового интегратора.

Цифровой интегратор содержит иаоитабный блок 1, блок 2 свертки

o 4 иращения подынтегральной функции, блок 3 коммутации, сумматор 4 подынтегральной функции, регистр 5 подынтегральной функции, блок б свертки подынтегральной функции, блок 7 умножения, сумматор 8 остат5 ,ка интеграла, регистр 9 остатка интеграла, блок 10 свертки остатка интеграла, блок 11 квантования, сумматор 12 по модулю 3. , блок 13 сравнения, счетчика 14 по модулю

0 (S. , вход 15 приращения подынтегральной функции, вход 16 приращения переменной интегрирования, выход 17 контроля, выход 18 интегратора.

Цифровой интегратор работает следующим образом.

На входы 15 и 16 интегратора в каждом шаге интегрирования подаются одноразрядные приращения и Д,, подынтегр.альной функции и пеQ ременной интегрирования соответственно. В масштабном блоке 1 приращения масштабируются и поступают на вход блока 2, в котором происходит образование контрольной

Р характеристики величины . с выхода блока 2 приращение поступает на вход сумматора 4, на второй вход которого с регистра 5 поступает значение подынтегральной функции v(, вычисленное на предыдущем шаге интегрирования. В результате выполнения операции суммирования получается новое значение подынтегральной функции:

5 где к - шаг интегрирования.

Новое значение подынтегральной функции у, с первого выхода сумматора 4 поступает на вход блока умножения 7 и через блок 6, в коQ тором происходит образование

контрольной характеристики подынтегральной функции У , на вход регистра 5. На второй вход блока умножения 7 поступают одноразрядные приращения переменной интегрированияд X со входа 16 приращения переменной интегрирования. Результат умножения значения Vvt на приращение с выхода блока 7 поступает на вход сумматора 8 остатка интеграла,на второй вход которого поступает из регистра 9 значение остатка интеграла ) предыдущего шага интегрирования.

Полученное в сумматоре 8 значение неквантованного приращения интеграла . поступает на вход блока 10 и на вход блока 11 квантования. В блоке 10 происходит выделение нового значения остатка интеграла SDK, которое поступает в регистр 9, и происходит образование контрольной характеристики остатка интегргша. В блоке 11 происходит выделение квантованного приращения интеграла на выход интегратора 18,

Для проведения контроля за достоверностью функционирования интегратора необходимо на каждом шаге интегрирования проводить контроль хранения и передачи кодовой информации в регистрах 5 и 9 и контроль выполнения арифметических операций в сумматорах 4 и 8 и блоке 7. С этой целью запишем все выполняемые в интеграторе арифметические операции в виде одной общей

-CVMI K V/ +SO., (1)

и будем производить контроль за выполнением не отдельных арифметических операций, а этой общей операции. Для обеспечения наибольшей достоверности контроля будем испол зовать контроль по модулю 9.

Так как приращение переменной итегрирования д,х может принимать знчения , О, (так как система кодирования приращений тернарная), то в зависимости от знчения эта общая операция, подлежащая контролю и соответственно алгоритм контроля будет принимать разный вид.

Рассмотрим все три случая.

Значение -ь 1, тогда

s-v,)v+s,.,) (2) и контроль выполнения арифметических операций сведется к контролю суммирования трех чисел. Получим алгоритм контроля. При контроле по модулю 5 контрольная характеристика QIC числа а определяется по формуле :

(N Xmoaa)(moda),

где Not - количество единиц в коде

двоичного числа. Тогда контрольные характеристики трех слагаемых будут иметь вид

v,K-,&--(Nvt.M) a))(vnogiа); (з)

л у-Е- - Ч д уУтоа д)1(гпоа вV, {4)

Озо(к-,)(-, а)(тоаа), (з)

в соответствии с правилом,справедливым при сложении чисел в двоичной системе исчисления, известно что

Na Nb-Hc neP, (g)

где NO и Nb - количество единиц в кодах чисел аи и, а N( и

количество единице в сумме и переносе, тогдч в нашем случае

YCк-4 v-V e (7)

М 4-U-гМ 4.V1

с SotK-ч) с2 пеР2 (8) J где N и Nnep. - количество единиц

в сумме и переносе сумматора 4 подынтегральной функции;

0 с, nepj количество единиц

в сумме и переносе cyNwaiopa 8 остатка интеграла. Подставим значение N, из выражения (8) в выражение (7), получим

V(K-,) - Kv ti nePi-HsotKMl H eP д,

тогда

0

,(,.М„,.

откуда

(a-i-Mvt.-.))(an-K,Xd4-K,.,V (.,Н;,е,у

Переходя от выражения для чисел к выражению для их остатков по модулю , палуч аем

р-1-м,,,(тоа av (э- -н утоас1)+

( - soCK-oH oa а) -v(3-3oiHmoaia)(mo6i а)

Ч- С2+Нпе« г перЛ1( 1

откуда

(км)ьк soCK-.( es)

(9) LЧNcl+Hnep HneP) 61),

Полученное выр 1жение позволяет производить контроль выполнения общей операция (1) в случае, если

Л.X + 1.

В этом случае, так как на вход блока 3 коммутации по входу 16 поступает значение + 1, то полученные в соответствии с выражениями (3), (4), (5) в блоках 2, 6, 10 контрольные характеристики QviK-i) г , QSotK-л) j поступают через блок 3 на входы сумматора 12, а н перенос с первого и второго

клходов сумматора 8 и перенос со

второго выхода сумматора 4 поступают через блок 3 в счетчик 14,

Сумматор 12 предварительно устанавливается поступающим с входа 16

значением А + 1 в исходное соегояние () (moa 5 ) и производит вычисление сумки контрольных характеристик QV(K-,b f So(K-) т.е. реализует левую часть контрольного выражения(9).Счетчик 14 по модулю Э производит подсчет по модулю а количества единиц в сумме и переносе, поступающих из сумматора 8 и в переносе, поступающем из сумматора 4, т.е. реализует правую часть контрольного выражения (.9) . Полученные в результате вычислений контрольная характеристика выргтеения (2) в сумматоре 12 и проверочная характеристика в счетчике 14 сравниваются в блоке 13 и в случае их несовпадения блок 13 выдает сигнал сбоя на выход контроля 17. Так производится контроль выполнения арифметических операций в цифровом интеграторе в случае 4-1. Для того, чтобы при этом одновременно производился контроль хранения и передачи кодов в регистрах 5 и 9, контрольные характеристики подынтегральной функции С|У(К-Ч)И остатка интеграла Q So (к./()вычисляются перед занесением их в регистры и хранятся в течение всего шага решения в блоках 6 и 10, тогда в случае искажения информации при хранении и передаче в регистрах 5 и 9 проверочная характеристика в.счетчике 14 будет иметь неверное значение и блок 13 выдает сигнал сбоя.

Во втором случае значение - 1, тогда контролируемая общая операция (1) будет иметь вид.

S УСК-Д) - ,VV(-0 + ,.,)

к-л)..inon: % v.-A), °

где ) vi ° дополнительный код суммы (, и уУ . В соответствии с выражением (6) запишем

Hv.,; (11) . (12)

Йо образование дополнительного кода в цифровом интеграторе при умножении нового значения подынтегральной функции на производится инвертированием значения подынтегральной функции с добавлением единицы в младший разряд при суммировании со значением остатка в сумматоре 8, тогда

Ы

,

где п - количество разрядов в регистре подынтегральной функции.

Подставим значение в исходное выражение (12), получим

(K..rV%eP,

в получившееся выражение подставим значение NC, из выражения (11) тогда

.,fHAv.,eotK-..

ca-x-N.,V(d-A-N V(a-i-Nso(.-.))

(m2-a),.

Переходя от выражения для чисе к выражению для их остатков, получаем:

;CdM-Ny.,)4( )-(cJ4-Ns,,,)V

tmoadl4n42-c3)(mocsa)(moa 3). (,)i

t VM; v;V-Q.,4(n+2-axmoaa)jt

moa )--(,,XmoaaV

Получившееся выражение позволит

контролировать выполнение арифметических операций в интеграторе в случае, если л л - 1.

Контроль достоверности функционирования цифрового интегратора в этом случае производится так же, как и в первом случае, когда + 1/ за тем исключением, что через блок 3 коммутации, на входы сумматора 12 подаются контрольные характеристики Qvi«,) , и () )/ а на вход счетчика l4-Ht2,HneP2 и -Нпер , и сумматор 12 устанавливается в исходное состояние

(n-va-ai)Cmoa а),

в третьем случае с х О , тогда контролируемая операция (1) распадется на две операции:

а)вычисление нового значения подынтегральной функции

)передача информации в регистре 9 остатка интеграла

Sow. SOCK-I).

В соответствии с выражением (6) .запишем

VtK-A-)

OtK-Al tj

Объединим эти два равенства, тогда

,(,..,,. (,,(.,-))

f(3-3ol)-(

) Переходя от выражения для чисел к выражению для их остатков, получаем (l,d-A-Hv,,,4nrvoa avca-A-Hi. av 4. С - -Nc,o(|Y:x(tnoa а) + 4- (з 3 а) а) -(HC, (о 4yi.-4)(K-0+tS-3a)Cmoda) хЧппосЗ ,,ГАс((тоа а). Получившееся выражение позволит контролировать выполнение арифметических операций в интеграторе в слу чае, если .-Q, Контроль за достоверностью функционирования в этом случае производится так же, как и в первом случае, за тем исключением, что через блок 3 на вход счетчика 14 подаются сумма и перенос с первого и второго выходов сумматора 4 и сумма с первого выхода сумматора 8 и сумматор 12 устанавливается в исходное состояние (3-за) . Подобная организация контроля в интеграторе позволяет производить контроль потоаЗпри затратах оборудования составляющих 15%, а контроль по той 7 при затратах оборудования 25%. Формула изобретения Цифровой интегратор, содержащий масштабный блок, сумматор подынтег ральной функции , регистр подынтегральной функции, блок умножения, сумматор остатка интеграла, регист остатка интеграла, блок квантования , причем первый вход сумматора подынтегральной функции подключен .к выходу регистра подынтегральной функции, первый вход блока умножения подключен к первому выходу сум матора подынтегральной функции,пер вый вход сумматора остатка интегра ла подключен к выходу блока умножения , второй вход сумматора остатка интеграла подключен, к выходу регистра остатка интеграла,вход блока квантования подключен к первому выходу сумматора остатка интеграла, второй вход блока умножения является входом приращения переменной интегрирования цифрового интегратора, вход масштабного блока является входом приращения подынтегральной функции цифрового интегратора, выход блока квантования является выходом цифрового интегратора, отличающийся тем, что, с целью повышения достоверности функционирования путем введения контроля .промежуточных операций, в него введены блок свертки приращения подынтегральной функции, блок свертки подынтегральной функции , блок свертки остатка интеграла, блок коммутации, сумматор по модулю а, счетчик по модулю б1 , einoK сравнения, причем вход блока свертки -приращения подынтегральной функции подключен к выходу масштабного блока, второй вход сумматора подынтегргшьной функции подключен к первому выходу блока свертки приращения подынтегральной функции, вход блока свертки подынтегральной функции подключен к первому выходу сумматора подынтегральной функции, вход регистра под нтегральной функции подключен к первому выходу блока сйертки подынтегральной функции, вход регистра остатка интеграла подключен к первому выходу блока свертки остатка интеграла, вход блока свертки остатка интеграла подключен к первому выходу сумматора остатка интеграла, первый,второй,третий,четвертый,пятый, шестой , седьмой входы блока коммутации подключены соответственно ко второму выходу блока свертки приращения -подынтегральной функции, второму выходу сумматора подынтегрсшьной функции, второму выходу блока свертки подынтегральнойфункции, первому выходу сумматора пода нтегральной функции,второму выходу сумматора остатка интегргша,второму выходу блока свертки остатка интеграла, первому выходу сумматора остатка интеграла, первый вход сумматора по модулю 61 подключен к первому выходу блока коммутации, вход счетчика по модулю 3 подключен ко второму выходу блока коммутации, первый и второй входы блока сравнения подключены соответственно к выходу сумматора по модулю d,и выходу счетчика по модулю о1 , восьмой вход блока коммутации и второй вход сумматора по модулю а объединены со вторым входом блока умножения, выход блока сравнения является выходом контроля цифрового интегратора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 328482, G, 06 J 1/02, 1972. 2.Авторское свидетельство СССР № 357570, 5 Об а 7/18, 1972 (прототип) .

ч .,;- . v-. -- , . .,4.,V-K..-,-,

«

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1974 |

|

SU519735A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

Авторы

Даты

1980-05-05—Публикация

1977-11-04—Подача