1

Изобретение относится к области вычислительной техники, а именно к цифровым интегрирующим машинам, и может быть использовано в однородных вычислительных системах.

Известен параллельный цифровой интегратор 1, состоящий из двух сумматоров и множительного устройства. К недостаткам этого устройства следует отнести то, что в процессе программирования приходится производить масштабирование переменных.

Наиболее близким по технической сущности к изобретению является параллельный цифровой интегратор с плавающей запятой 2, содержащий сумматор подынтегральной функции, счетчик, регистр сдвига, первые входы которых являются информационными входами интегратора, сумматор остатка интеграла, выход которого является информационным выходом интегратора, первый дешифратор, умножитель, формирователь сигнала нормализации, первые входы которых являются управляющими входами интегратора, и второй дешифратор.

Недостатком этого интегратора является невысокая точность измерения.

Целью изобретения является повышение точности работы.

Поставленная цель достигается тем, что в предложенный интегратор введены дополнительно третий дешифратор, формирователь сигнала переполнения, две группы элементов И, причем выходы старших К. разрядов сумматора подынтегральной функции соединены соответственно со входами умножителя, выходы которого подключены ко входам сумматора остатка интеграла, выходы старшего и знакового разряда сумматора подынтегральной функции соединены с вторым и третьим входами формирователя сигнала нормализации, первый выход которого соединен со вторыми входами

сумматора подынтегральной функции, первого дешифратора и счетчика и с первым входом третьего дешифратора, первый и второй выходы которого подключены соответственно к первым и вторым входам формирователя сигнала переполнения и второго дешифратора и с вторым и третьим входами регистра сдвига, первый и второй выходы регистра сдвига подключены к третьему и четвертому входам второго дешифратора, первый выход которого соединен с третьим входом формирователя сигнала переполнения и с первыми входами элементов И первой группы, выходы которых подключены к входам младших К разрядов.

сумматора подынтегральной функции, второй выход дешифратора соединен с четвертым входом формирователя сигнала переполнения и с первыми входами элементов И второй группы, выходы которых подключены к входам старших Д разрядов сумматора подынтегральной функции. Третий выход регистра сдвига подключен к вторым входам первых элементов И первой и второй групп, четвертый выход - к вторым входам вторых элементов И первой и второй групп, пятый выход - к вторым входам третьих элементов И первой и второй групп. Второй выход формирователя сигнала нормализации соединен с вторым входом третьего дешифратора, с третьими входами сумматора подынтегральной функции, первого дешифратора и счетчика, выход которого соединен с четвертым входом формирователя сигнала нормализации, выход первого дешифратора соединен с информационным выходом интегратора и с первым входом сумматора остатка интеграла. Третьи входы элементов И первой и второй групп соединены с информационным входом интегратора. Третий вход третьего дешифратора и пятый вход формирователя сигнала нормализации соединен с , управляющим входом интегратора. Выход формирователя сигнала переполнения подключен к управляющему выходу устройства.

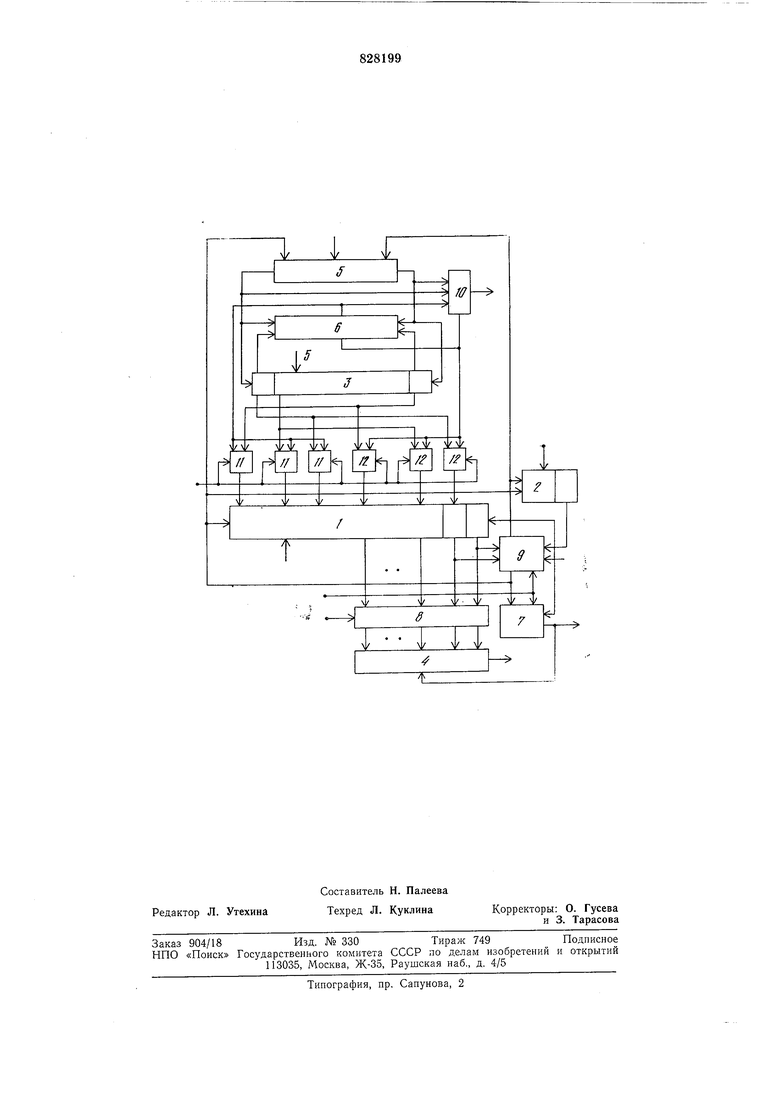

На чертенсе приведена структурная схема интегратора.

Он содержит сумматор 1 подынтегральной функции, счетчик 2, регистр 3 сдвига, сумматор 4 остатка интеграла, дешифраторы 5, 6, 7, умножитель 8, формирователь 9 сигнала нормализации, формирователь 10 сигнала переполнения и группы элементов ИИ, 12.

Интегратор работает следующим образом.

Предварительно выравниваются веса начальных значений подынтегральных функций и их приращений.

В регистре 3 сдвигается импульс, определяющий разность весов подынтегральной функции и ее приращений, влево или вправо по сигналам, вырабатываемым дешифратором 5 увеличения или уменьшения веса входного приращения соответственно. Дешифратор 6 вырабатывает знак разности весов подынтегральной функции и ее приращений. При этом положительный знак разности весов вырабатывается, когда импульс находится в старшем разряде регистра 3 при поступлении из дешифратора 5 сигнала на увеличение веса входного приращения, а отрицательный - когда импульс находится в младшем разряде регистра 3 и при поступлении сигнала из дешифратора 5 на уменьшение веса входного приращения. При повторной записи импульса в младший или старший разряд регистра 3 вырабатывается формирователем

10 сигнал переполнения. При положительном знаке разности весов и сигналу, поступающему из регистра 3, выделяется соответствующим элементом И 12 приращение подынтегральной функции, вес которого больше кванта и суммируется в сумматоре 1 с /С старшими разрядами подынтегральной функции. А при отрицательном знаке разности весов выделяется соответствуюшим элементом И 11, приращение, вес которого меньше кванта и суммируется с К младшими разрядами функции. При этом старшие Л разрядов подынтегральной функции одновременно поступают на входы умножителя 8, где умножаются на приращение переменной интегрирования и результат параллельным кодом суммируется в сумматоре 4 с /( разрядами остатка. И если в результате суммирования возникает переполнение разрядной сетки сумматора 4, то из него выдается приращение интеграла. В конце операции интегрирования вычисленные в сумматоре 1 значения подынтегральной функции анализируются формирователем 9, который вырабатывает сигналы нормализации влево (вправо), в сумматоре 1 код подынтегральной функции сдвигается влево (вправо), в счетчике 2 при этом вычитаются (суммируются) единичные импульсы, а дешифратор 5 вырабатывает сигнал изменения веса входного приращения. Сигнал на увеличение веса входного приращения дешифратор 5 вырабатывает в следующих случаях:

-при поступлении на его вход сигнала увеличения веса входного приращения и при отсутствии сигналов нормализации;

-при поступлении на его вход сигнала увеличения веса входного приращения и при поступлении сигнала нормализации влево;

-при отсутствии сигнала увеличения веса входного приращения и при поступлении сигнала нормализации влево.

Сигнал на уменьшение веса входного приращения вырабатывается при отсутствии сигнала увеличения веса входного приращения и при поступлении сигнала нормализации. Сигнал на увеличение веса выходного приращения вырабатывается дешифратором 7 по сигналу нормализации влево или по сигналу увеличения веса приращения переменной интегрирования. Если эти сигналы поступят одновременно, то дешифратор 7 выдаст один сигнал увеличения веса выходного приращения, а второй запоминается. Последний выдается только тогда, когда не поступает сигнал на увеличение веса приращения переменной интегрирования и отсутствует сигнал нормализации вправо. При выдаче сигнала увеличения веса выходного приращения в сумматоре 4 сдвигается влево код остатка на один разряд.

Введение новых блоков в интегратор позволяет повысить точность вычисления за счет того, что исключена потеря входных приращений, меньших чем квант.

Формула изобретения

Параллельный цифровой интегратор с плавающей запятой, содержащий сумматор подынтегральной функции, счетчик, регистр сдвига, первые входы которых являются информационными входами интегратора, сумматор остатка интеграла, выход которого является информационным выходом интегратора, первый дешифратор, умножитель, формирователь сигнала нормализации, первые входы которых являются управляющими входами интегратора, второй дещифратор, отличающийся тем, что, с целью повышения точности работы, в него введены дополнительно третий дешифратор, формирователь сигнала переполнения, две группы элементов И, причем выходы старших К. разрядов сумматора подынтегральной функции соединены соответственно со входами умножителя, выходы которого подключены ко входам сумматора остатка интеграла, выходы старшего и знакового разряда сумматора подынтегральной функции соединены с вторым и третьим входами формирователя сигнала нормализации, первый выход которого соединен со вторыми входами сумматора подынтегральной функции, первого дешифратора и счетчика и с первым входом третьего дешифратора, первый и второй выходы которого подключены соответственно к первым и вторым входам формирователя сигнала переполнения и второго дешифратора и с вторым и третьим входами регистра сдвига, первый и второй выходы регистра сдвига подключены к третьему и четвертому входам второго Дешифратора, первый выход которого соединен с третьим входом формирователя

сигнала переполнения и с первыми входами элементов И первой группы, выходы которых подключены к входам младших К. разрядов сумматора подынтегральной функции, второй выход второго дешифратора соединен с четвертым входом формирователя сигнала переполнения и с первыми входами элементов И второй группы, выходы которых подключены к входам старШ11Х /С разрядов сумматора подынтегральной функции, третий выход регистра сдвига подключен к вторым входам первых элементов И первой и второй групп, четвертый выход - к вторым входам вторых элементов И первой и второй групп, пятый выход - к вторым входам третьих элементов И первой и второй групп, второй выход формирователя сигнала нормализации соединен с вторым входом третьего дешифратора, с третьими входами сумматора подынтегральной функции, первого дешифратора, и счетчика, выход которого соединен с четвертым входом формирователя сигнала нормализации, выход первого дешифратора соединен с информационным выходом интегратора и с первым входом сумматора остатка интеграла; третьи входы элементов И первой и второй групп соединены с информационным входом интегратора, третий вход третьего дешифратора и пятый вход формирователя сигнала нормализации соединены с управляющим входом интегратора, выход формирователя сигнала переполнения подключен к управляющему выходу устройства.

Источники информации, принятые во внимание при экспертизе

1.Аналоговая и аналого-цифровая вычислительная техника. М., Машиностроение,

.

2.Отчет «Парабола-2 Гос. per. № 69018223, техническое описание, с. 8-29 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

| Цифровой интегратор | 1976 |

|

SU651371A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Цифровой интегратор | 1979 |

|

SU903875A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

Авторы

Даты

1981-05-07—Публикация

1977-03-24—Подача