1

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых интегрирующих структур вычислительных у ::тройств.

Известен цифровой интегратор с тернарным способом кодирования входных и выходных величин, реализующих различные формулы численного интегрирования, содержащий сумматор для получения нового значения подынтегральной функции, блок умножения, сумматор остатка и два регистра для хранения подынтегральной функции и остатка интеграла 1.

Недостатком такого интегратора является наличие погрешности, свяi HHba с выбором того или иного метода численного интегрирования, , и погрешности, накапливающейся во времени при. прерывистом характере процесса интегрирования, т.е. когца независимая переменная изменяет во времени свою величину по модулю и знаку.

Наиболее близким по технической сущности к предлагаемому является интегратор, содержащий регистр и сумматор подынтегральной функции, входной блок и входную клемму приращений подынтегральной функции, стохастический переключатель, бло1 умножения, входную клемму приращег НИИ независимой переменной, сумматор и регистр приращений интеграла, выходной блок и выходную клемму приращений интеграла. Входящий в состав известного устройства стохастический переключатель позволяет в процессе

o интегрирования переходить с метода прямоугольников с недостатком на метод прямоугольников с избытком и наоборот 2.

Однако применение стохастического переключателя, позволяющего усреднять значения интеграла, т.е. снижать погрешность метода интегрирования при незначительном увеличении аппаратурных затрат, не приводит к уменьшению погрешности, накапливающейся во времени при прерывистом характере вычисления с переменным знаком приращений незавиСИМОЙ переменной, и эта погрешность при длительных процессах вычисления может достигать значительной величины.

Цель изобретения - повышение точности.

.Цель достигается тем, что в цифровой интегратор, содержащий сумматор подынтегра льной .функции, первый вход которого соединен через блок ввода со входом при{ а1цений подынтегральной функции интегратора, регистр подынтегральной функции, выход которого подключен к первому входу переключателя и второму входу сумматора подынтегральной функции, выход которого соединен со входом регистра подынтегральной функции и вторым входом переключателя, выход которого соединен с первым входом блока умножения, второй вход которого соединен со входом приращений независимой переменной интегратора, выход блока умножения соединен с первым входом сумматора приращений интеграла, выход которого подключен через блок вывода к выходу интеграюра и через регистр приращений интеграла - ко второму входу сумматора приращений интеграла, введены блок памяти и узел сброса, причем выход блока умножения соединен с первым входом блока памяти, выход которого подключен к третьему входу cyiviMaTopa приращений интеграла, . второй вход блока умножения соединен с первым входом узла сброса, второй вход которого подключен к синхронизирующему входу интегратора выход узла сброса соединен со вторым входом блока памяти.

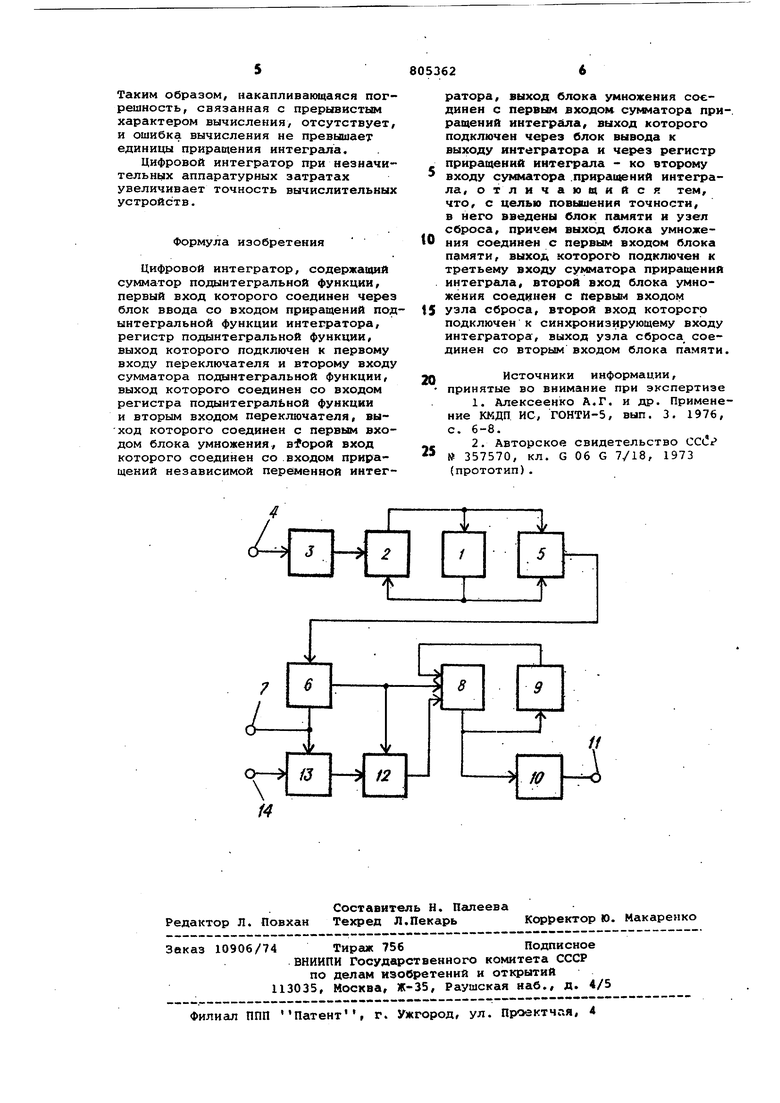

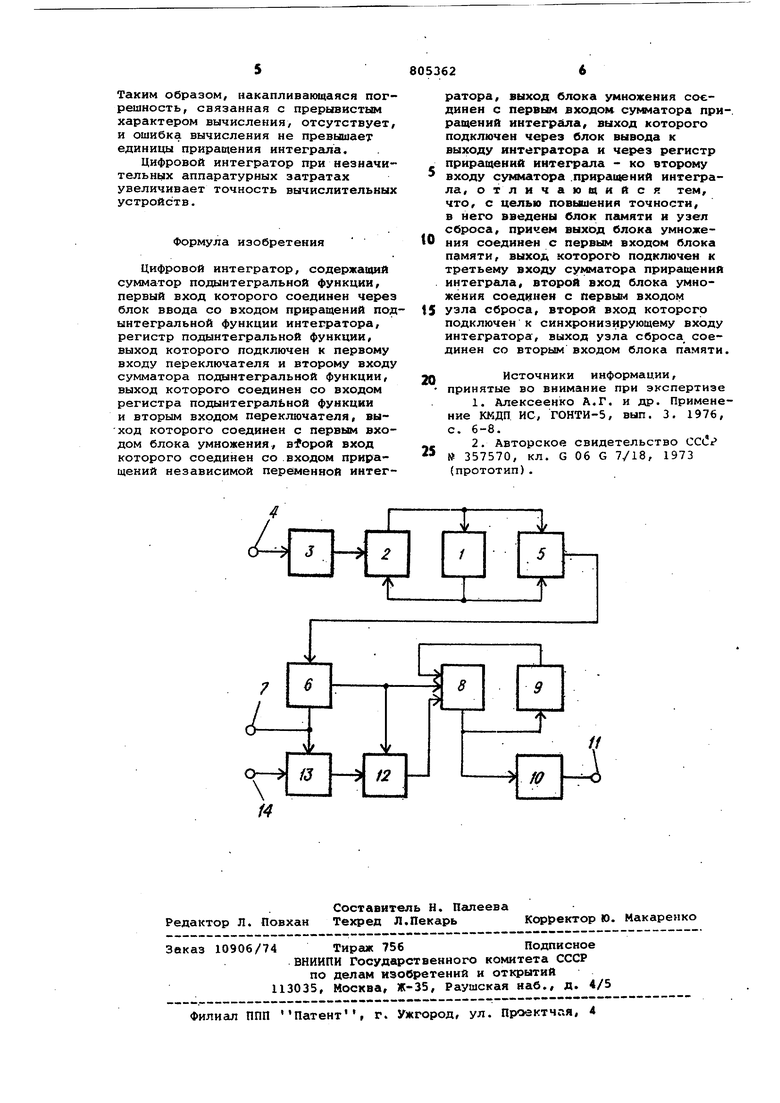

Блок-снема цифрового интегратора представлена на чертеже.

Устройство содержит регистр 1 подынтегральной функции, сумматор 2 подынтегральной функции, блок 3 ввода, вход 4 приращений подынтегральной .функции, -переключатель 5 (стохастический) , блок 6 умножения, вход 7 пр..ращений независимой пере енной, сумматор 8 приращений интеграла, регистр 9 приращений интеграла, блок 10 вывода, выход 11 приращений интеграла., блок 12 памяти, узел 13 сброса, синхронизирующи вход 14. .

Блок памяти 12 предназначен для хранения результата произведения

подынтегральной функции на независимую переменную, т.е., приращения интеграла от предыдущего шага интегрирования и знака этого приращения до В5 зобновления процесса вычисления с тем, чтобы на первом шаге интегрирования после возобновления процесса вычисления, сформировать новое значение интеграла от предыдущего шага интегрирования. Узел 13 сброса предназначен для формировани сигнала сброса для блока памяти 12 после каждого шага интегрирования, если процесс вычисления носит непрерывный характер.

Цифровой интегратор работает следующим образом.

Приращения подынтегральной функции со входа 4 через блок 3 поступают на один из входов сумматора 2 и записываются .в регистре 1, где и хранятся все время, пока будет идти процесс вычисления. Приращения независимой переменной через вход 7 поступают на один из входов блока 6 умножения, на другой вход которого поступают значения подынтегральной функции из регистра 1 и сумматора 2 через стохастический переключатель 5. В блоке б умножения идет процесс умножения значения подынтегральной функции на независимую переменную. Приращения интеграла, полученные в результате умножения, поступают на одиц из входов сумматора 8 приращений интеграла и записываются в регистре 9. Приращения интеграла с вьхода сумматора 8 через блок 10 поступают на выход 11. Стохастически переключатель 5 позволяет перехбдить в процессе вычисления по случайному закону с метода интегрирования по прямоугольникам с избытком на метод интегрирования по прямоугольникам с недостатком. Приращения независимой переменной со входа 7 поступают также и на один из входов узла 13 сброса, на второй вход которого поступают импульсы синхронизации со входа 14. Если на 1-том шаге интегрирования на выходе блока б умножения появится приращение интеграла, то оно. запишется не только в регистре 9, но и в блоке 12 памяти, пройдя На один из его входов. Если процесс вычисления не прекратится,

то узел 13 сброса сформирует сигнал сброса блока 12 памяти , и процесс интегрирования протекает обычным путем. Узел 13 сброса формирует сигнал сброса при непрерывном характере процесса вычисления на каждом шаге интегрирования. Зсли на i-том шаге интегрирования процесс вычисления прекратится, то сигнал сброса не сформируется и при наличии на выходе блока 6 умножения приращения инт-еграла, на данном шаге интегрирования последний запишется в блоке 12 памяти (модуля и знака приращения интеграла) и будет храниться в нем со своим знаком до возобновления процесса вычисления. При возобновлении процесса вычисления на первом же (1 + 1) шаге интегрирования это приращение интеграла, пройдя на один из входов сумматора 8,.просуммируется с текущим значением интеграла, хранящимся в регистре 9, и таким образом сформируются новае значение интеграла от п едыдущего i-toro щага интегрирования. Информация о приращении интеграла, хранящаяся в блоке 12 памяти, сбросится сигналом от узла 13 сброса, и далее процесс вычисления протекает обычным путем.

Таким образом, накапливающаяся погрешность, связанная с прерывистым характером вычисления/ отсутствует, и ошибка вычисления не превышает единицы приращения интеграла.

Цифровой интегратор при незначительных аппаратурных затратах увеличивает точность вычислительных устройств.

Формула изобретения

Цифровой интегратор, содержащий сумматор подынтегральной функции, первый вход которого соединен через блок ввода со входом приращений подынтегральной функции интегратора, регистр подынтегральной функции, выход которого подключен к первому входу переключателя и второму входу сумматора подынтегральной функции, выход которого соединен со входом регистра подынтегральной функции и вторым входом переключателя, выход которого соединен с первым входом блока умножения, вfopoй вход которого соединен со .входом приращений независимой переменной интегратора, выход блока умножения соединен с первым входом сумматора при-, ращений интеграла, выход которого подключен через блок вывода к выходу интегратора и через регистр приращений интеграла - ко второму 5 входу сумматора .приращений интеграла, отличающийся тем, что, с целью повышения точности, в него введены блок пгшяти и узел сброса, причем выход блока умножения соединен с первым входом блока памяти, выход которогй подключен к третьему входу сумматора приращений интеграла, второй вход блока умножения соединен с первыси входом

5 узла сброса, второй вход которого подключен к синхронизирующему входу интегратора, выход узла сброса соединен со вторым входом блока памяти.

Источники информации, принятые во внимание при экспертизе

1.Алексеенко А.Г. и др. Применение КМДП ИС, ГОНТИ-5, вып. 3. 1976,

С. 6-8.,

2.Авторское свидетельство ССсг 357570, кл. G 06 G 7/18, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Цифровой интегратор | 1979 |

|

SU903875A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1064280A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU409248A1 |

| Детерминированно-вероятностный интегратор | 1979 |

|

SU857990A1 |

| ИНТЕГРАТОР ДЛЯ ПАРАЛЛЕЛЬНОЙ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ МАШИНЫ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1973 |

|

SU388278A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

Авторы

Даты

1981-02-15—Публикация

1979-03-05—Подача