а выход подкпючеи к выходу ограничителя,

4.Интегратор поп. l.OTnHHaro щ и и с я тети, что -ограничитель сдвига пош штеграпьной функции содержит сумматор по модугао два и элемент НЕ, причем первый вход cyhiMaropa по модупю два подкгаочен к знаковому входу огранкчитегта, второй вход - к информационному входу ограничителя, а выход че рез элемент НЕ соединен с выходом ограничитепя.

5,Интегратор поп. 1, отпичаю щ и и с я тем, что ограничитель сдвига масштабного коэффициента содер шт три элемента И, два элемента ИЛИНЕ, элемент НЕ, причем знаковый вход t ограничителя соединен с первым входом первого элемента И и через элемент НЕ с первым входом второго элемента И, выходы первого и второго элементов И соединены с первым и вторым входами первого элемента ИЛИ-НЕ соответственно, выход первого элемента ИЛИ-НЕ соединен с выходом ограничителя, инфо1 мадионные входы ограничителя соединены с входами второго элемента ИЛИ-НЕ и третьего элемента И, выход второго элемента ИЛИ-НЕ соединен с вторым входом второго элемента И,а выход третьего элемента И соединен с вторым входом первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1986 |

|

SU1334145A2 |

| Устройство масштабирования цифрового дифференциального анализатора | 1983 |

|

SU1156069A1 |

| Цифровой интегратор | 1979 |

|

SU822222A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

1. 1Ш4 РОВОЙ ИНТЕГРАТОР, содержащий регистр немасштабированного интеграпа, регистр масштабированного интеграпа, два сумматора, регистр под,ынтегральной функции и регистр масштабного коэффициента, причем информационные выходы регистра немасштабированного интеграпа соединены с первыми входами первого сумматора, выходы которого соединены с информационными входами ре гистра немасштабированного интегр&па, выход переполнения которого соединен с управляющим входом второго сумматора, выхощ 1 которого подключены к информационный входам регистра масштабированного интеграла, информационные выходы ко торого соединены с первыми входами второго сукп атора, а выход переполнения с выходом интегратора, вход управления первого сумматора соединен с входом приращения независимой переменной интегратора, выходы регистра подынтеграль ной функции соединены с вторыми входами первого сумматора, а выходь регист|ра масштабного коэффициента соединены с вторыми входами второго сумматора, отличающийся тем, что, с цепью увелйе1тя точности представления интеграла, в него введены ограничитель сдвига подынтегральной функции, ограничитель сдвига масштабного коэффициента, элемент НЕТ и элемент И, причем инфо{ мационщ 1й вход ограничителя сдвига подынтегральной функции соединен с выходом старшего разряда регистра подынтегральной функции, а знаковый вход ограничителя сдвига подынтегральной функции соединен с выходом знакового разряда регистра подынтегральной функции, знаковый вход ограничителя сдвига масштабного коэффициента соединен со знаковым выходом ре гистра масштабного коэффициента, информационные входы ограничителя сдвига масштабного коэффициента соединены с информационными выходами регистра мае- о штабного коэффициента, вход синхронизации интегратора соединен с первым входом элемента И, выход которого соединен с входами сдвига регистра подынтеграль ной функции и регистра масштабного коэффициента, вход элемента НЕ подключен к входу прирашения независимой переменной интегратора, выход элемента НЕ соединен с вторым входом элемента И, третий вход которого подключен к выходу ограничителя сдвига подынтегральной функции, четвертый вход элемента И подключен к выходу ограничителя сдвига масштабного коэффициента. 2.Интегратор по п. 1, отличающий с я тем, что ог1Х1НИчитепь сдвига подынтегральной функции содержит элемент НЕ, вход которого подкгаочен к информационному входу ограничителя, а 1ход соединен с выходом ограничителя. 3.Интегратор по п. 1, отличающий с я тем, что ограничитель сдвЯг га масштабного коэффициента содержит элемент ИЛИ, входы которого соединены с информационными входами ограничителя.

Изобретение относится к вычислитель ной технике и предназначено для испопьзовашш в цифровых дифференциальных анапизаторах (ЦДЛ.). Вычислительные оп рации в ЦДА выполняются как правило с масштабированными величинами. При этом часто встречается необходимость в умножении результата интегрирования на некоторый постоянный масштабный коэффициент К, который по абсолютной велиЧ 1не может быть как больше, так и мень ше единицы. В известных устройствах умножение результата интегрирования }щ постоянный масштабный коэффициент реапизуется с помощью масштабного интегратора (ми), подынтегральной функцией которого явгшется К, если , и--если |К 1. В случае )К| 1 МИ включается поспецовательно с цифровым интегратором, в случае МИ включа ется в обратную связь цифрового интегратора по схеме следящего интегратора При этом как цифровой, так и мас штабный интеграторы содержат регистр подынтегральной функции, регистр интеграла, сумматор, обеспечивающий сумми рование с текущим значением интеграла или В1з:чкташта из него содержимого ре гисгра подынтегральной функции по сигнапам приращений независимой перемеилюй tl. Накбопее близким техническим решеHVI6M является цифровой интегратор, содержащий регистр подынтегральной функции, регистр масштабного коэффициента, регистр масштабированного интеграла, регистр немасштабированного интеграла и два сумматора, причем выход переполнения регистра немасштабированного интеграла соединен с входом управления первого сумматора, информационные выходы этого регистра соединены с nepv яыми входами второго сумматора, выходы которого соединены с входами этого регистра, выход переполнения регистра масштабированного интеграла соединен с выходом интегратора, выходы этого регистра соединены с первыми входами первого сумматора, выходы которого подключены к входам этого регистра, выходы регистра масштабного коэффициента соединены с вторыми входами первого сумматора, а .выходы регистра подынтегральной функции соединены с вторыми входами второго сумматора 2 }. Недостатком известных устройств я&пяется постоянная абсолютная погрешность представления интеграла, опредепяемая ве{шчиной масштабного коэффициввта К, так как каждому импульсу пр ращения интеграла соответствует увели- . чение В71И уменыиение интеграла ка вететину К. Это приводит к существенным относительным погрешностям представпения интеграла при малых скоростях иэмекешш последнего, т.е. при малых значениях модуля подынтегральной функции. Цель изобретения - увеличение точноо ти представления интеграла.

Посгавпенная цепь достигается тем, что в цифровой интегратор, содержащий регистр немасштабирова иного интеграпа, регистр масштабированного интеграла, Ива сумматора, регистр подынтегральной функции и регистр масштабного коэффициента, причем информационные выходы регистра немасштабированногр интеграла соединены с первыми входами первого сумматора, выходы которого соединены с информационными входами регистра немасштабированного интеграпа, выход переполнения которого соединен с управляющим входом второго сумматора, выходы которого подключены к информационным входам регистра масштабированного ив теграпа, информационны. выходы которого соедкнёиы с первыми входами второго сумматора, а выход переполнения - с н 1ходом интегратора, вход управления первого сумматора соединен с входом приращения независимой переменной интегратора, вь1хбды регистра подынтеграпь ной функции соединены с вторыми входами первого сумматора, а выходы регистра масштабного коэффициента соединены с вгррымв входами второго сумматора, введень ограничитель сдвига подынтегральной функции, ограничитель сдвига масштабного коэффициента, элемент НЕ и элемент И, причем информационный вход ограничитедя сдвига подынтегральной функции соединен с выходом старшего разряда регистра подынтегральной функции а знаковый вход ограничителя сдвига пош 1нтеграпьной функции соединен с выходом знакового разряда регистра подынтегральной функции, з.наковый вход ограничителя сдвига масштабного коэффипиентасоединенс знаковым выходом регистра масштабного коэффициента, информационные входы ограничителя сдвига масштабного ко- Эгффициёнта соединены с информационными выходами регистра масштабного коэффициента,вход синхронизации интегратора соединен :с первым входом элемента И,выхоп кото- рого соединен е входами сдвига регистра цояынгеграпьной функции н регистра масштабного коэффициента, вход элемента НЕ подключен к входу прирашения независимой йеременвой ийтегратора, выход эпемента НЕ соединен с вторым входом апемента И, третий вход которого подК71ЮЧ&Н к выходу ограничителя сдвига подывтеграпьной функции, четвертый вход элемента И подключен к выходу огранигчителя сдвига масштабного коэффициента.

При кодировании подынтегральной функции прямым кодом ограничитель сдвва подынтегральной функции содержит элемент НЕ, вход которого подключен к информационному входу ограничителя, а выход соединен с s iходом ограничителя. При кодировании масштабного коэффи-i циента прямым кодом ограничитель сдвига масштабного коэффициента содержит элемент ИЛИ, входы которого соединены с информационными входами ограничителя, а выход подключен к выходу ограничителя.

При кодировании подынтегральной функции, обратным кодом, ограничитель сдвига подынтегральной функции содержит сумматор по модулю два и элемент НЕ, причем первый вход сумматора по модутпо два подключен к знаковому входу ограничителя, второй вход - к информационному входу ограничителя, а выход через элемент НЕ соединен с выходом ограничителя.

При кодировании масштабного коэффициента обратным кодом ограничитель сдви га масштабного коэффициента содержит три элемента И, два элемента ИЛИ-НЕ и элемент НЕ, тфичем знаковый вход ограничителя сдвига соединен с первым входом первого элемента И и через элемент НЕ с первым входом второго элемента И, Еыхо№1 первого и второго элементов И соединены с первым и вторым входами первого элемента ИЛИ-НЕ. соответствевно, выход первого элемента ИЛИ-НЕ соединен с выходом ограничителя, информационные входы ограничителя соединены с входами второго элемента ИЛИ-НЕ и третьего элемента И, выход второго элемента ИЛИ-НЕ соединен с вторым входом второго элемента И,а выход третьего элемента И соеаинен со , входомпервого элемента И..

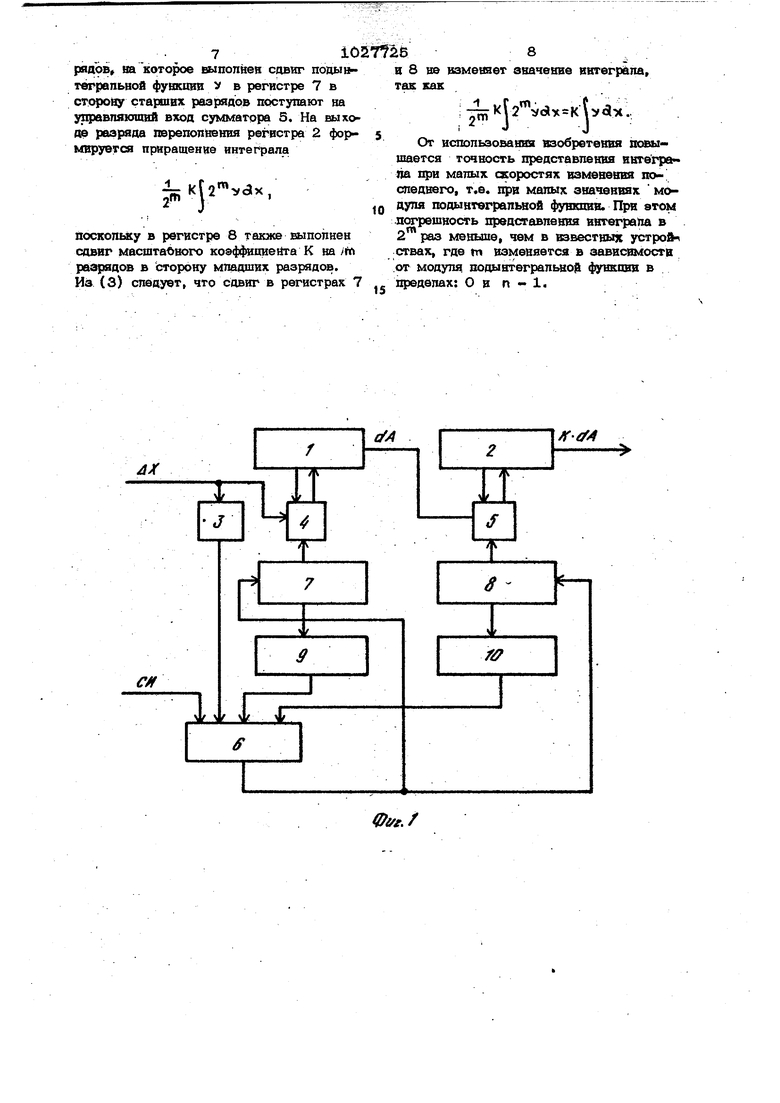

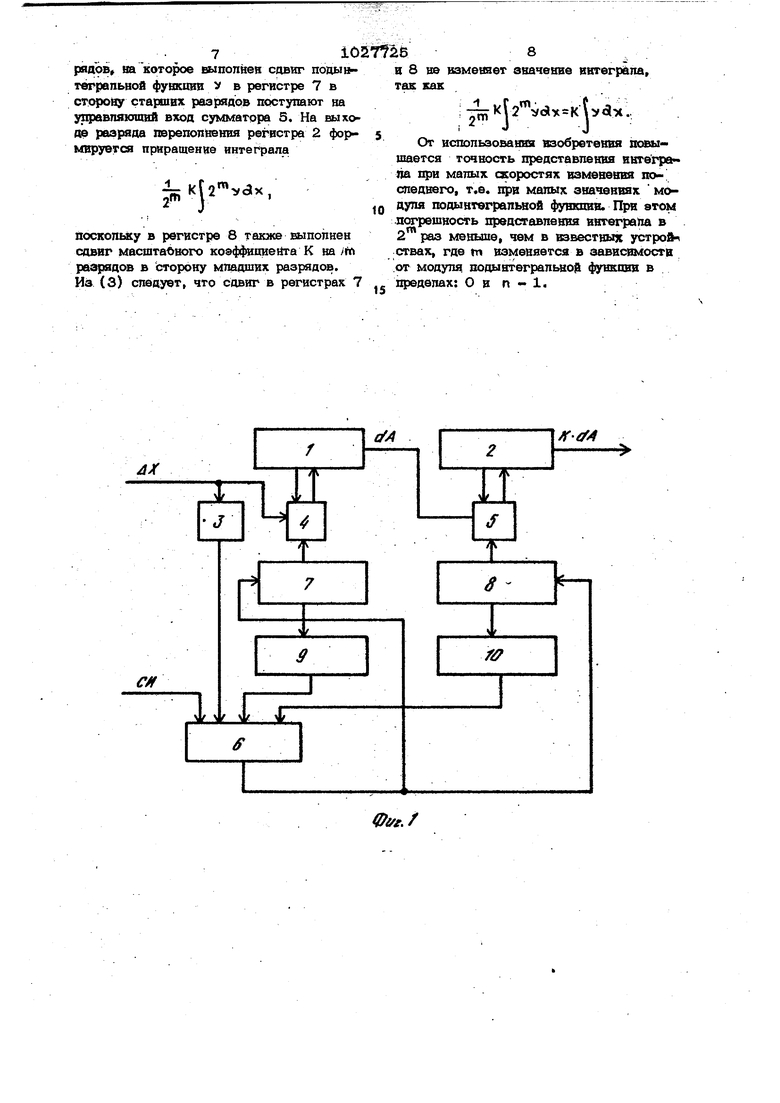

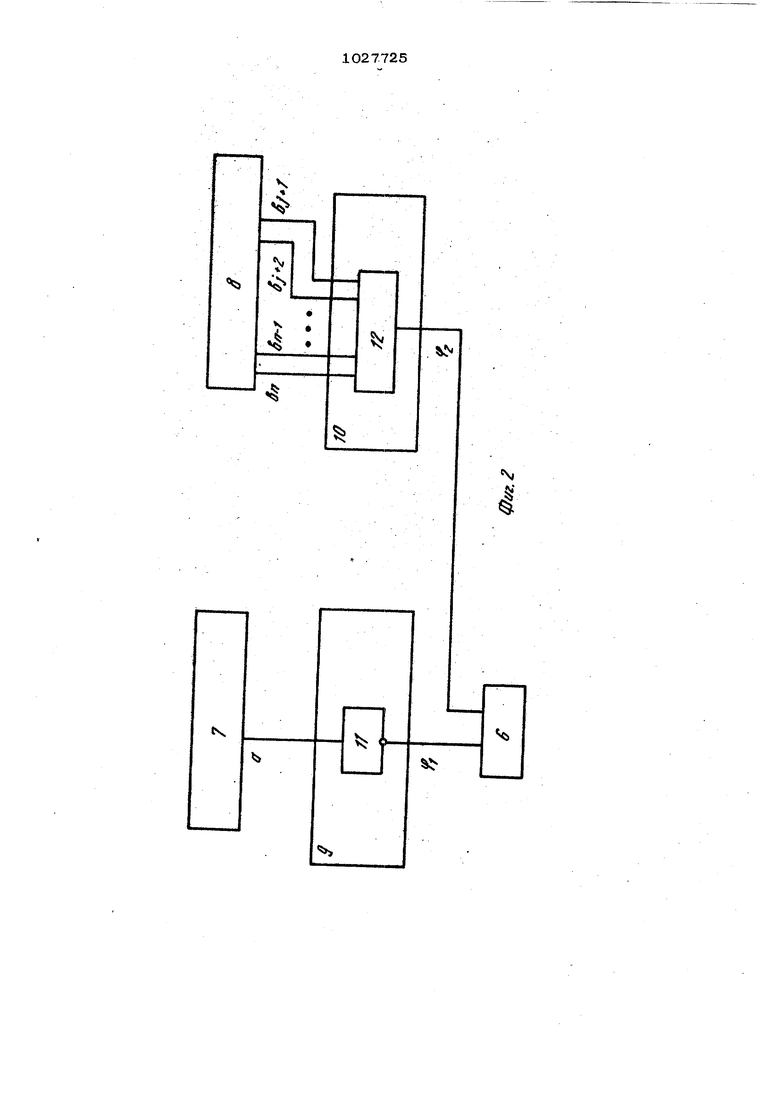

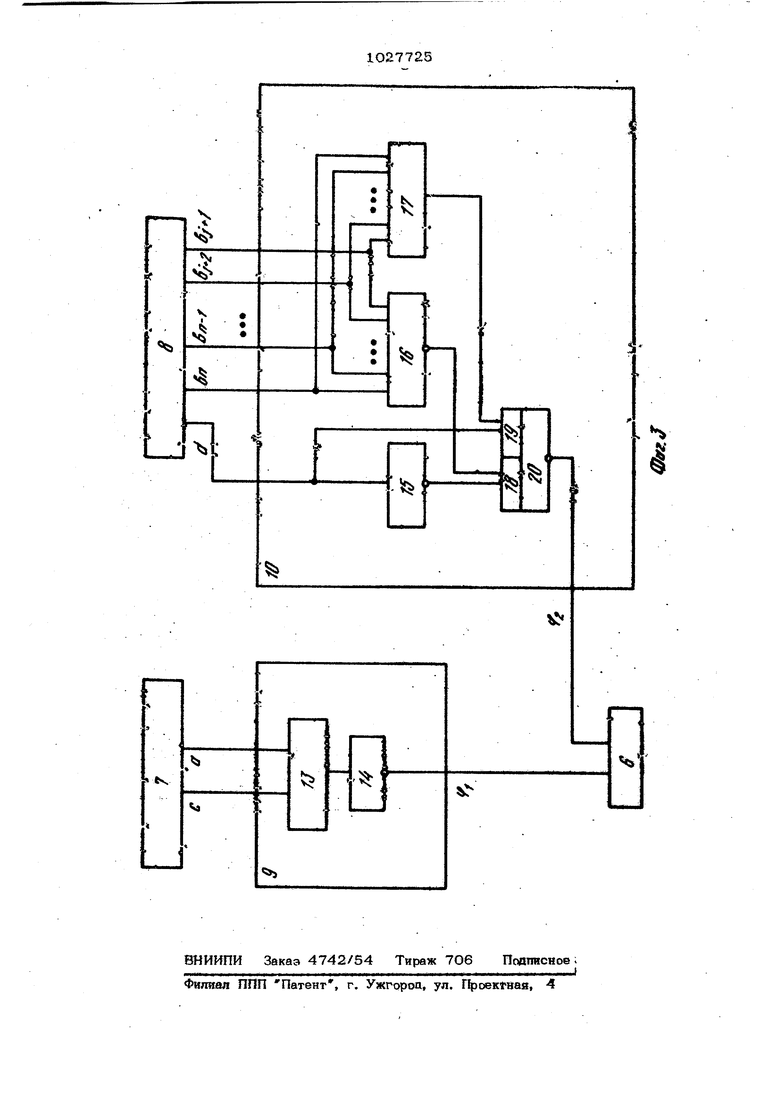

На фиг. 1 представлена блок-схема цифрового интегратора; на фиг. 2 - схемы ограничителей сдвига при кодировании подынтегральной функции в масштабного коэффициента прямым кодом; на фиг. 3 - схемы ограничителей сдвига при кодировании подынтегральной функции и масштабного коэффициента обратным кодом.

Цифровой интегратор содержит регистр 1 немасштабированного интеграла, регистр 2масштабированного интеграла, элемент НЕ 3, сумматоры 4 и 5, элемент И б, регистр 7 подынтегральной функции V. регистр 8 масштабного коэф цнента К, ограничитель 9 сдвига подынтегральной функции, ограничитель 10 сдвнга маоштабного коэффициента. Цепи, обеспечивающие заполнение регистров 7 и 8, на

фкг. 1 не отражены. ОгранИчигель 9 () содержит, элемент НЕ 11. Огр ничитепь 10. (фиг.2) содйржиг эпемевт ИЛИ 3.2. Ограничитель 9 (фиг. 3) сюдержкт сутчШатор 13 по модулю два и элемент НЕ 14. Ограничитель 10 (фиг.З содержит элемент НЕ 15, элемент ИЛИНЕ 16, элементы И 17 - 19 и элемевт 20.

Регистр 1 j сумматор 4 и регистр 7 образуют собственноннтегратор, вычиопяювд1й значение интеграла iStiX . ре-

j :

гистр 2, сумматор 5 и регистр 8 обра.зуюг 1.4ас)штабиый интегратор, реализующей умножеике интеграПа на масJ I

коэффициент К. Информационные

входы сумматоров 4 и 5 подключены соогветсгвенно к выходам регистров 1,72,8. Выходы сумматоров 4 и 5 подключеьтьт соогБетственно к входам регистров 1 и 2, Управпяюхцие входы сумматоров. 4 .и 5 подключены соответственно к выходу формирователя приращений дХ независимой . переменной X и к разряду перепопнекия регистра 1. Управляющие входы р8гисгров7 и 8 подключены к выходу эпемента И 6, один вход которого подключен к выходу генератора синхроимпульсов /СИ/, другой вход через элемент НЕ 3 соединен с выходом формирователя приращений & X, третий и четвертый входы соедиш1Ш1 с выходами ограничитепой 9 и 10. Входы ограничителей 9 и 10 соединены с выходами регистров 7 и 8.

Интегратор работает следующим об разом.

Вег01чина модуля масштабного коаффициента К рассчитывается при условии макс{-1мального значения модуля подынтегральной функции 1/ , ограниченного емкостью регистра 7. В процессе функционирования интегратора значение модуття подынтегральной функции может изменять ся от нуля до максимального, .равного емкости регистра 7. Если текущее значение модуля подь1нтегральной фуикнии меньше максимального, то при отсутствии импульса приращения независимой переменной Х по синхроимпульсам СИ. выпол й1ется сдвиг на одинаковое число разрядов в регистрах 7 и 8. При этом коды в регистрах 7 и 8 сдвигаются на один разряд по каждому синхроимпульсу соответственно в сторону старших и

мпадщих разрядов до тех пор, пока не будет выполнено неравенство

2В UUd(1)

И71И неравенство

А 1УК2Х (2)

где jKf и fv/ - модули масштабного

коэффициента К и подынтегральной функции

У;

В - вес единицы j -го раэ ряда регистра 8 ();

номер старшего и младшего разрядов регистра 8;

А - вес единицы старшего

разряда регистра 7. В случае выполнения неравенства (1) или (2) на выходе ограничителя 10 или 9 формируется сигнал, закрывающий элвг мент И б и блокирующий соответственно .вырабйтку импульсов сдвига в регистрах 7 и 8. Булевы функции и 2 , реа.лизуемые ограничителями 9 и 10, определяются выражениями (1) и (2) и способом кодирования подынтегральной функции у и масштабного коэффициента К,В случае представления подынтегральной фзгнкции у и масштабного коэффициента К в прямом коде (фиг. 2)

v 01;

I где а - единичное состояние старшего разряда регистра 7; Ъ - нулевое состояние i -го ( i

j + li n) разряда регистра 8; Г) и 1 - номер старшего в младшего разрядов регистра 8.

В случае представления подынтегральной функции У и масштабного коэффициента К в инверсном (обратном или допот нительном) коде фиг. 3 . V с5

.-Ьи)(Ч-.-Ъ,,)

где 5 - нулевое состояние старшего

разряда регистра 7; ОМС - единичное и нулевое состояния знакового разряда регистра 7; о1 и «5 - единичное и нулевое состояния .

знакового разряда регистра 8; Ь- - единичное состояние ) -уо разряда регистра 8 (4 + 1,0). Импульсы переполнения из разряда переполнения регистра 1, т.е. приращения

интеграла 2 хЛх, , где ,ип - число раз

рядов на которое выполнен сдвиг подынтегральной фушшив У в регистре 7 в сторону старших разрядов поступают на управляющий вход сумматора 5. На выходе разряда перепопнення регистра 2 формируется приращение HHrefpana

i

:sKl2™ 3,

поскопысу в регистре 8 также выпопнен сдвиг масштабного коэффипиейта К на tttt разрядов в сторону мтшдших разрядов. Из (3) следует, что сдвиг в регистрах 7

н 8 не изменяет значение HHTerpiana, так как

Kr2 v6lx KUcl-x..

: Л

гт JJ JJ

От использования изобретения повышается точность представления интеграпа при маттых скоростях изменения по-; спеднего, т.е. при малых значениях модуля подынтегральной функции. При этом .погрешность представления интеграла в 2 раз меныие, чем в известных ycTpofr ствах, где tn изменяется в зависимости .от модуля подынтегрально функпни в пределах: О и п - 1.

Й5СГ./

N

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шепейко А | |||

| В | |||

| Цифровые модели | |||

| М., Энергия, 1964, с | |||

| ЗО, рис | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Майоров Ф | |||

| В | |||

| Эпектронные цифровые интегрирующие МИШИНЫ | |||

| М., Маш1962, с | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

| шэ, | |||

Авторы

Даты

1983-07-07—Публикация

1982-02-24—Подача