Изобретение относится к вычислительной технике и предназначено для использования в интегрирующих вычислительных структурах (иве).

Целью изобретения является повышение быстродействия за счет сокращения времени обмена информацией,

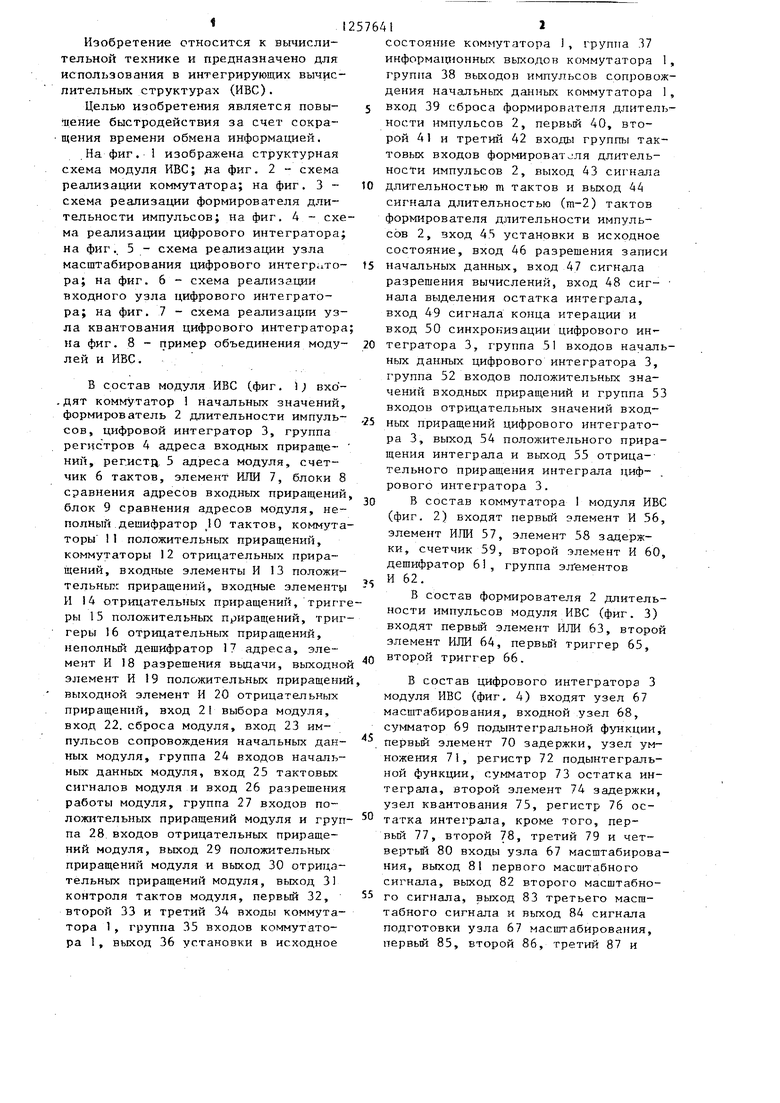

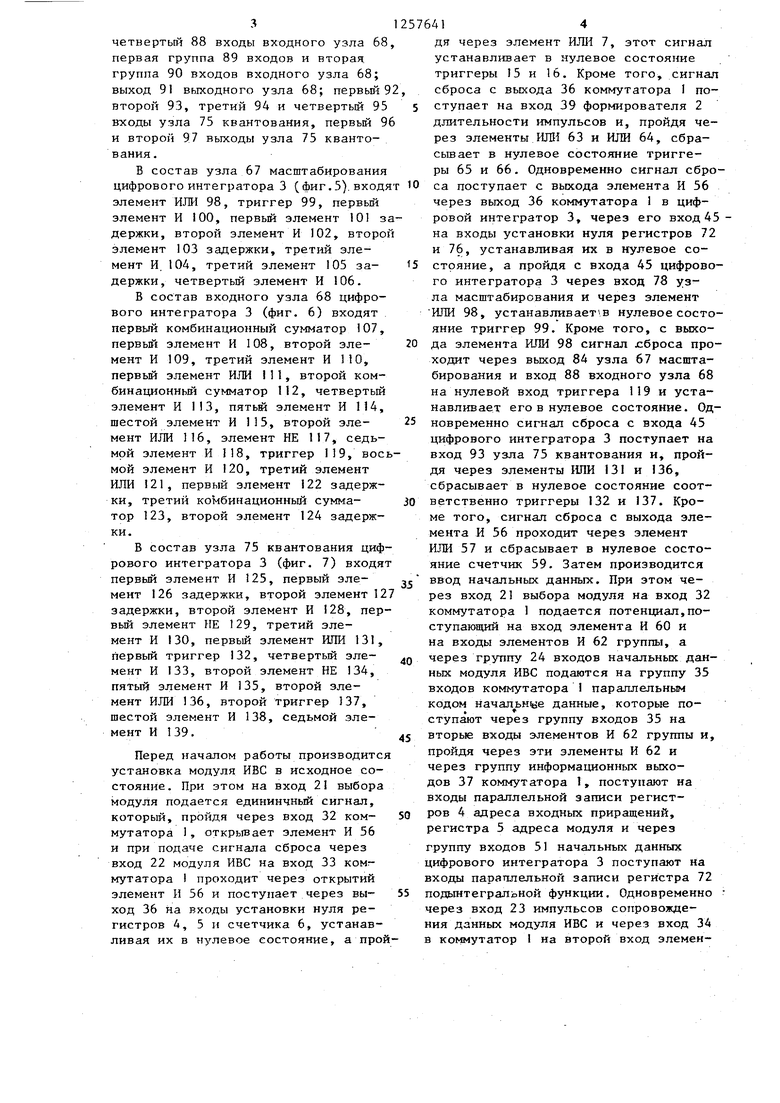

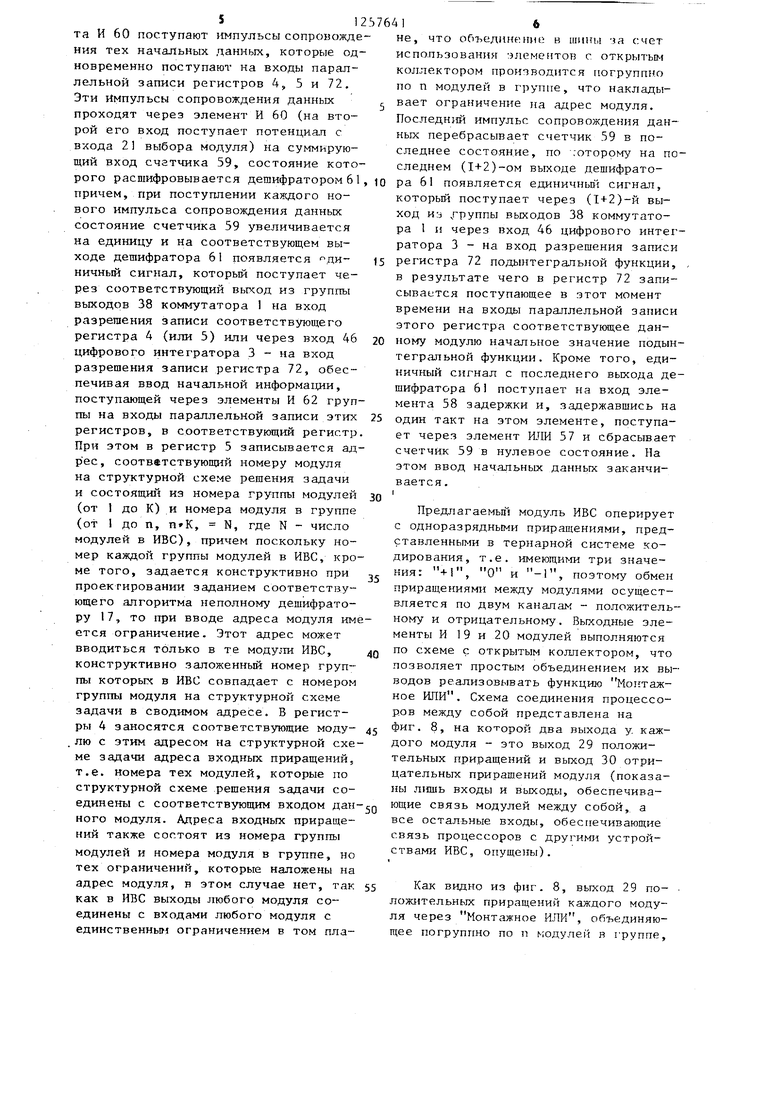

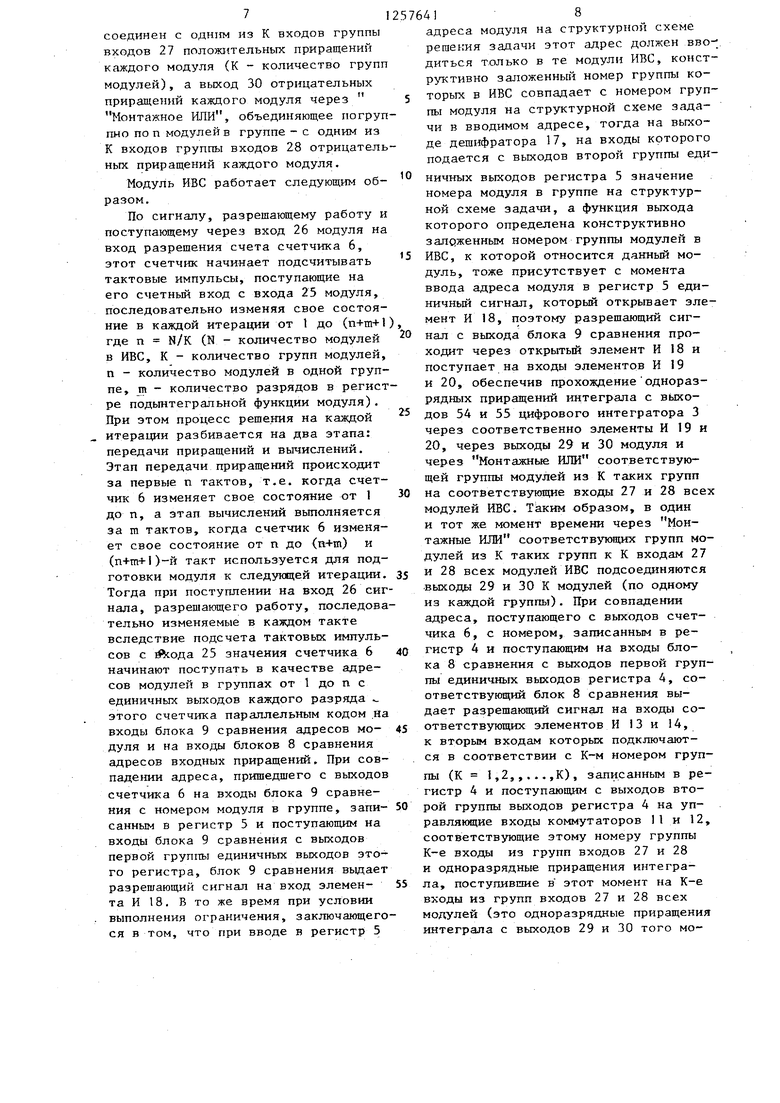

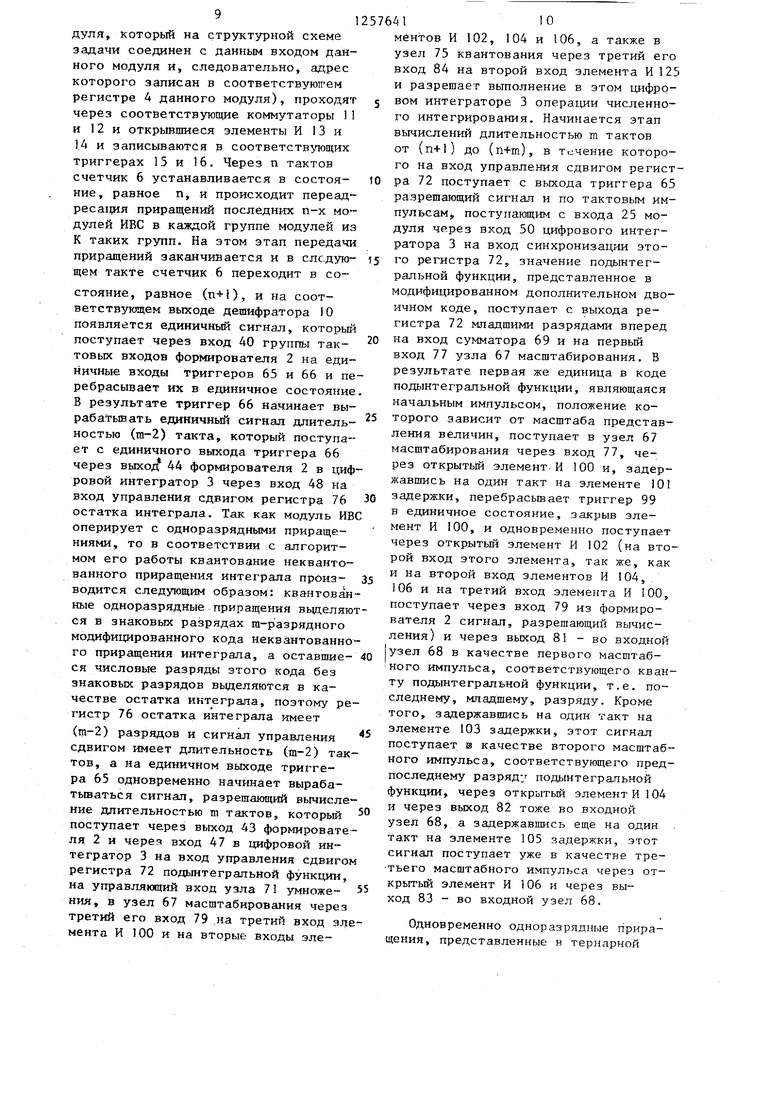

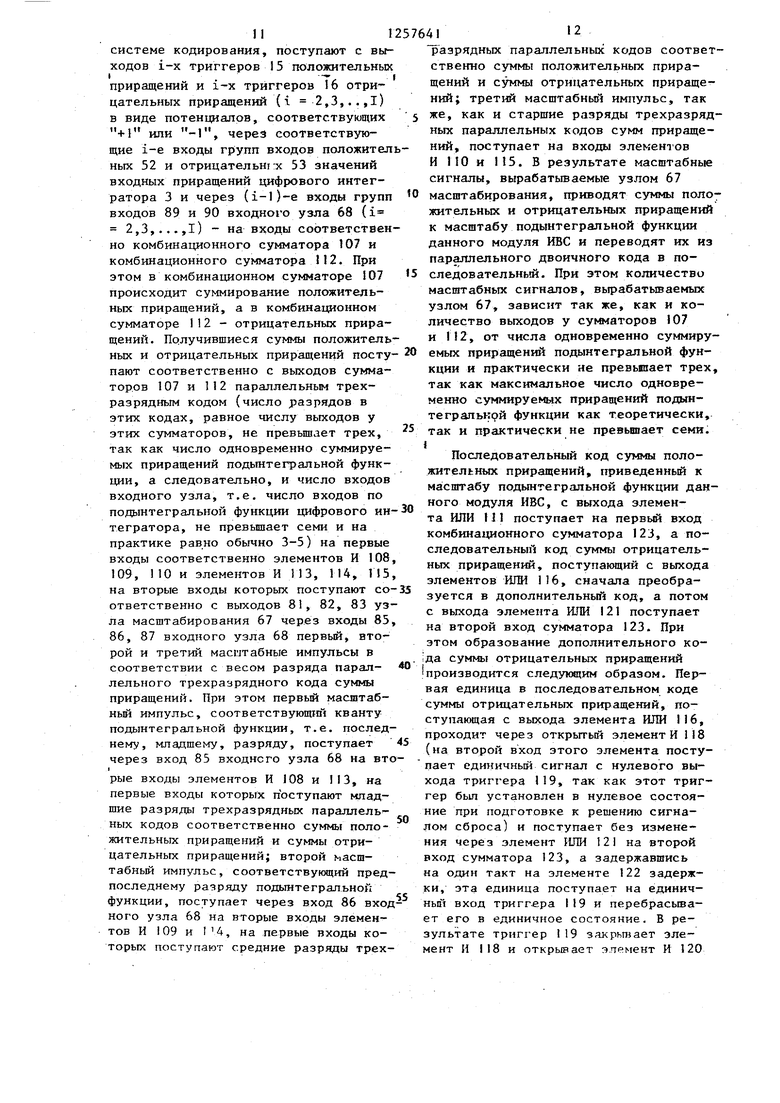

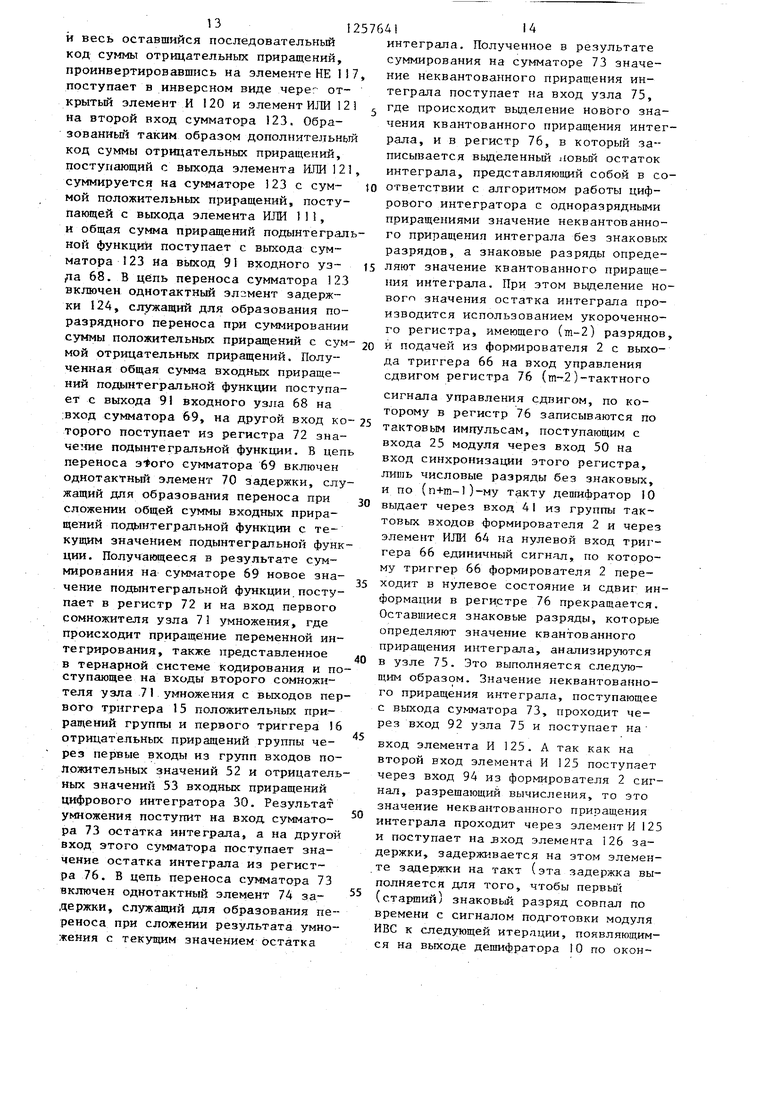

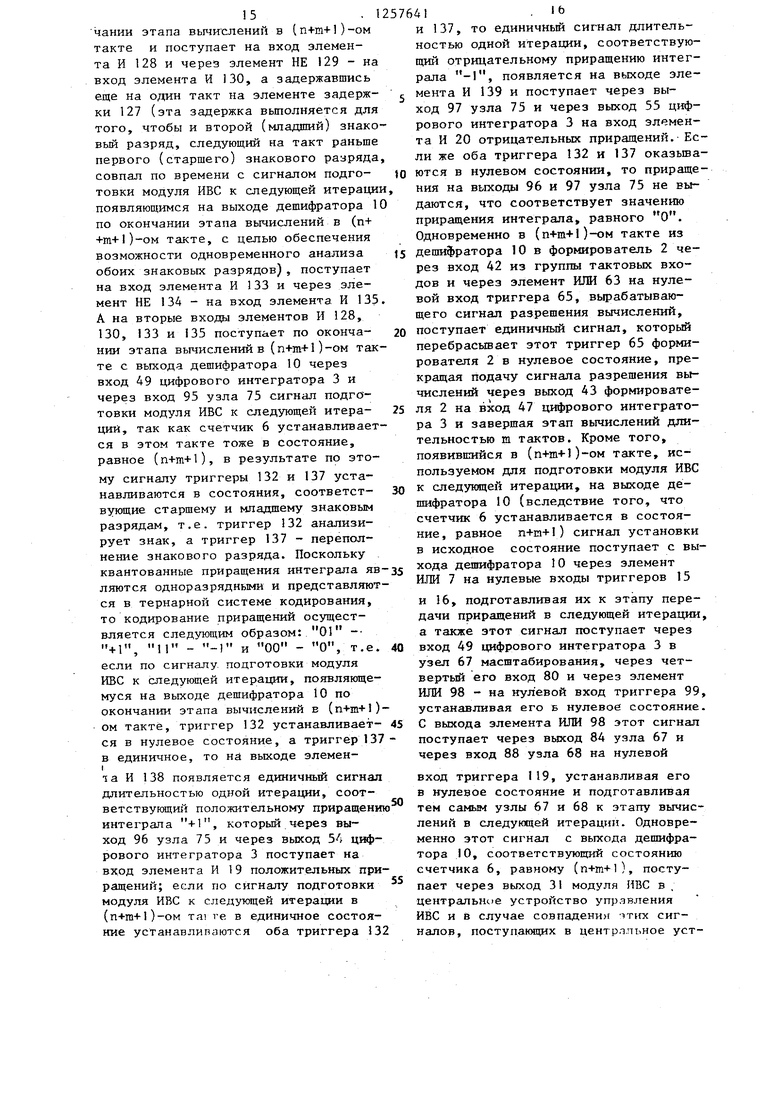

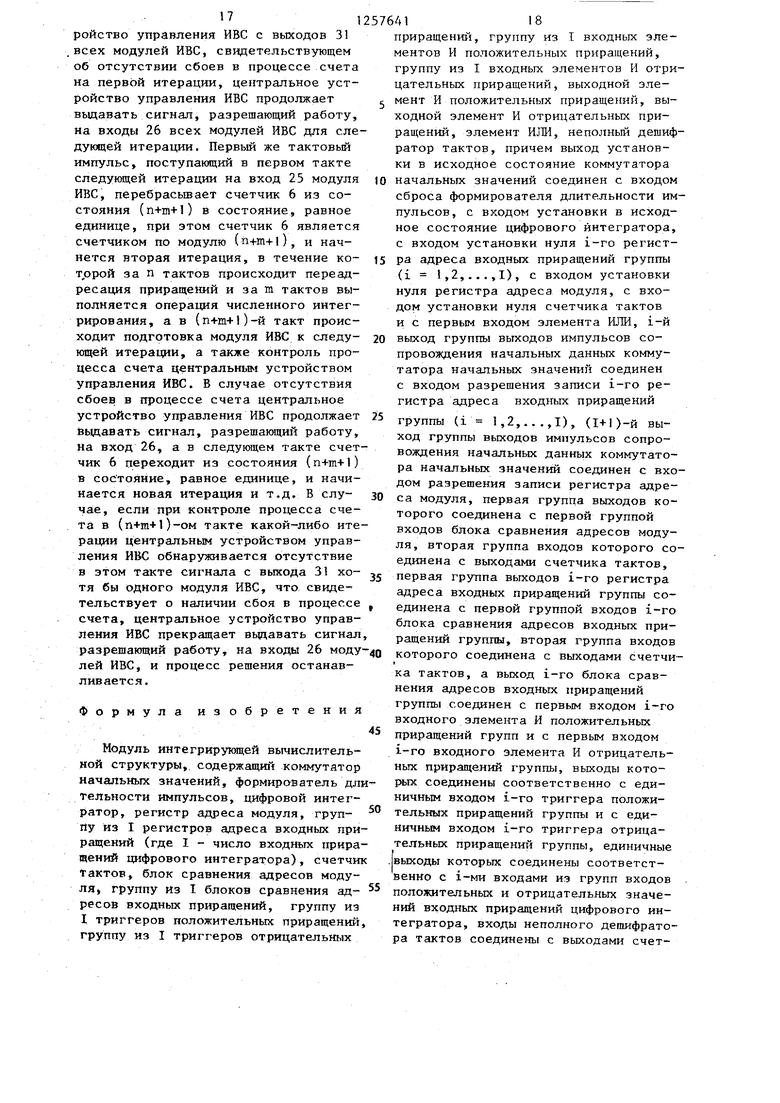

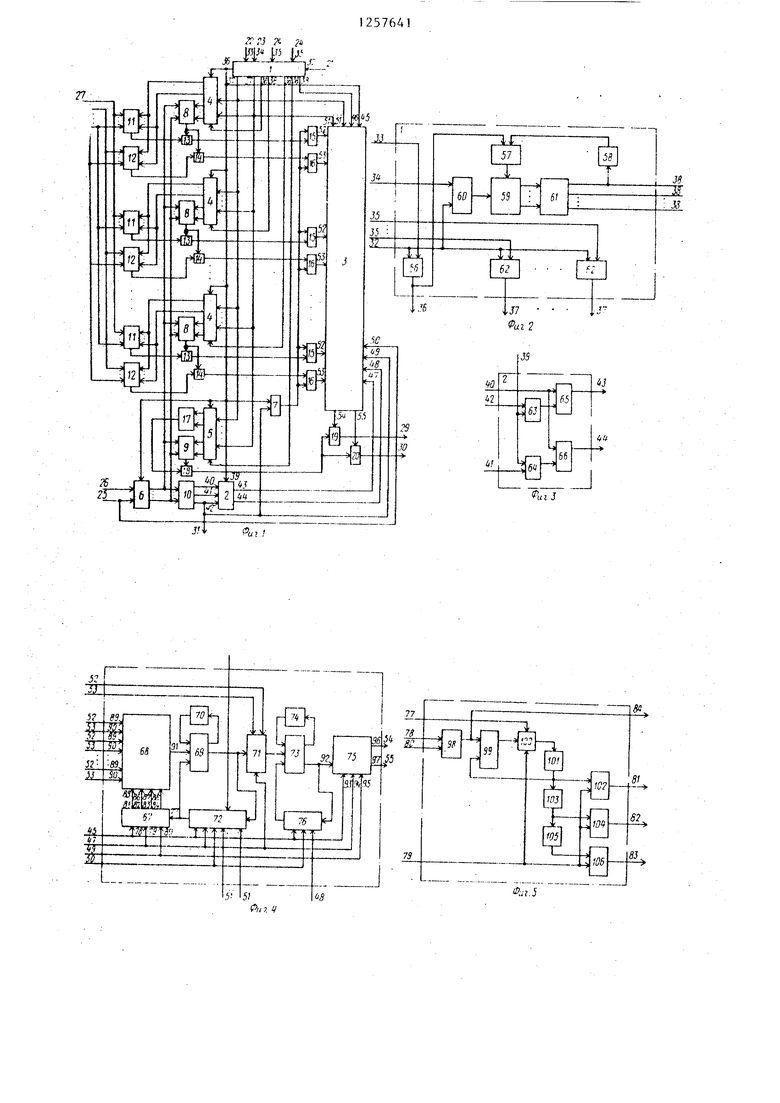

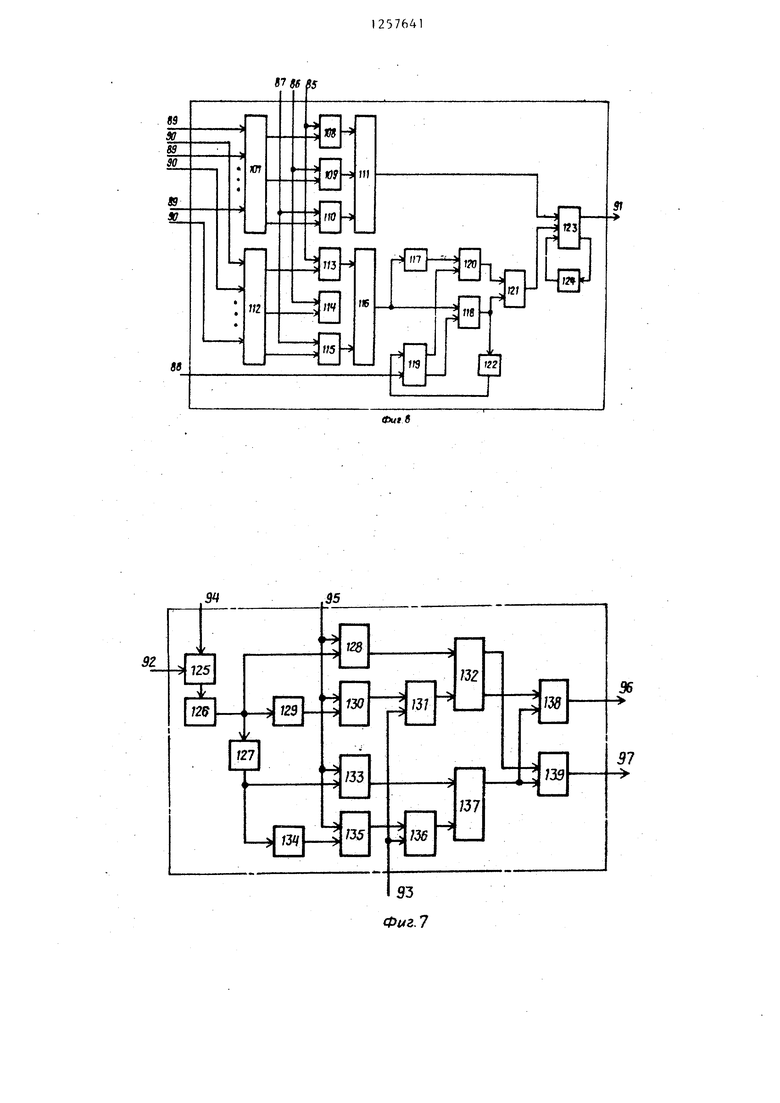

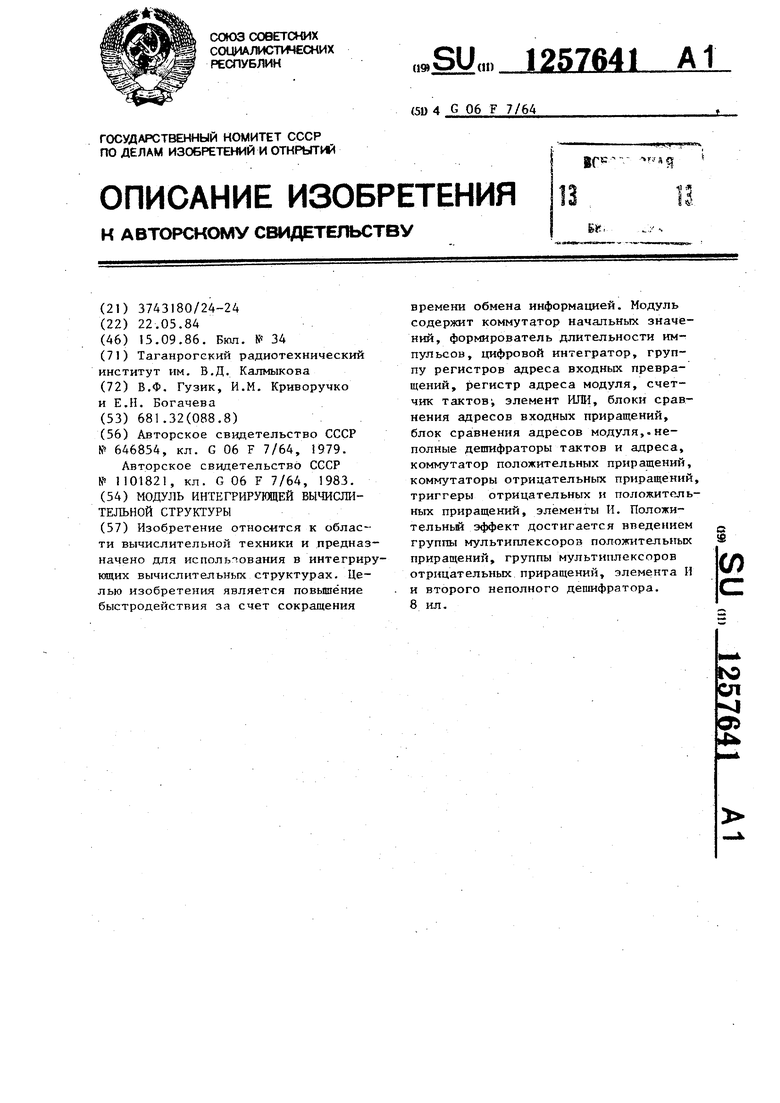

.На фиг. 1 изображена структурная схема модуля ИВС; да фиг. 2 -- схема реализации коммутатора; на фиг, 3 - схема реализации формирователя длительности импульсов; на фиг, А - схема реализации цифрового интегратора; на фиг,. 5 - схема реализации узла масштабирования цифрового интегратора; на фиг, 6 - схема реализации входного узла цифрового интегратора; на фиг, 7 - схема реализации узла квантования цифрового интегратора на фиг. 8 - пример объединения модулей и ИВС,

в состав модуля ИВС (фиг, ) вхо - дят коммутатор 1 начальных значений, формирователь 2 длительности импульсов, цифровой интегратор 3, группа регистров 4 адреса входных прираще- НИИ, регистр, 5 адреса модуля, счетчик 6 тактов, элемент ИЛИ 7, блоки 8 сравнения адресов входных приращений, блок 9 сравнения адресов модуля, неполный дешифратор 10 тактов, коммутаторы II положительных приращений, коммутаторы 12 отрицательных приращений, входные элементы И 13 положи- тельньпг приращений, входные элементу И 14 отрицательных приращений, триггеры 15 положительных приращений, триг- геры 16 отрицательных приращений, неполный дешифратор 17 адреса, эле5

25

30

35

мент И 18 разрешения выдачи, выходной элемент И 19 положительных приращений, выходной элемент И 20 отрицательных приращений, вход 21 выбора модуля, вход 22. сброса модуля, вход 23 импульсов сопровождения начальных данных модуля, группа 24 входов начальных данных модуля, вход 25 тактовых сигналов модуля и вход 26 разрешения работы модуля, группа 27 входов положительных приращений модуля и группа 28 входов отрицательных приращений модуля, выход 29 положительных приращений модуля и выход 30 отрицательных приращений модуля, выход 31 контроля тактов модуля, первьй 32, второй 33 и третий 34 входы коммутатора 1, группа 35 входов коммутатора 1, выход 36 установки в исходное

50

55

10

ts

576412

состояние коммутатора i, группа 37 информационных выходов коммутатора 1, группа 38 выходов импульсов сопровождения начальньЕХ данньк коммутатора 1 , 5 вход 39 сброса формирователя длительности импульсов 2, первьй 40, второй 41 и третий 42 входы группы тактовых входов формироваТч ля длительности импульсов 2, выход 43 сигнала длительностью m тактов и выход 44 сигнала длительностью (т-2) тактов формирователя длительности импульсов 2, вход 45 установки в исходное состояние, вход 46 разрешения записи начальных данных, вход 47 сигнала разрешения вычислений, вход 48 сиг- нала выделения остатка интеграла, вход 49 сигнала конца итерации и вход 50 синхронизации цифрового интегратора 3, г руппа 51 входов начальных данных цифрового интегратора 3, группа 52 входов положительных значений входных приращений и группа 53 входов отрицательных значений входных приращений цифрового интегратора 3, выход 54 положительного приращения интеграла и выход 55 отрица-- тельного приращения интеграла цифрового интегратора 3,

В состав коммутатора I модуля ИВС (фиг. 2) входят первый элемент И 56, элемент ИЛИ 57, элемент 58 задержки, счетчик 59, второй элемент И 60, дешифратор 61 , группа эл ементов И 62,

В состав формирователя 2 длительности импульсов модуля ИВС (фиг, 3) входят первый элемент ИЛИ 63, второй элемент ИЛИ 64, первый триггер 65,

20

25

30

35

, второй триггер 66.

В состав цифрового интегратора 3 модуля ИВС (фиг, 4) входят узел 67 масштабирования, входной .узел 68, сумматор 69 подынтегральной функции, первьй элемент 70 задержки, узел умножения 71, регистр 72 подынтегральной функции, сумматор 73 остатка интеграла, второй элемент 74 задержки, узел квантования 75, регистр 76 остатка интеграла, кроме того, первьй 77, второй 78, третий 79 и чет- вертьй 80 входы узла 67 масштабирования, выход 81 первого масштабного сигнала, выход 82 второго масштабного сигнала, выход 83 третьего масштабного сигнала и выход 84 сигнала подготовки узла 67 масштабирования, первьй 85, второй 86, третий 87 и

50

55

четвертый 88 входы входного узла 68, первая группа 89 входов и вторая группа 90 входов входного узла 68; выход 91 выходного узла 68; nepBbDi9 второй 93, третий 94 и четвертый 95 входы узла 75 квантования, первый 96 и второй 97 выходы узла 75 квантования.

В состав узла 67 масштабирования цифрового интегратора 3 (фиг,5). входя элемент ИЛИ 98, триггер 99, первый элемент И 100, первый элемент 101 задержки, второй элемент И 102, второй элемент 103 задержки, третий элемент И 104, третий элемент 105 за- держки, четвертый элемент И 106.

В состав входного узла 68 цифрового интегратора 3 (фиг. 6) входят первый комбинационный сумматор 107, первьй элемент И 108, второй эле- мент И 109, третий элемент И ПО, первьй элемент ИЛИ 111, второй ком- бинационньш сумматор 112, четвертый элемент И 113, пятьй элемент И 114, шестой элемент И 115, второй эле- мент ИЛИ 116, элемент НЕ П7, седьмой элемент И 118, триггер 119, восьмой элемент И 120, третий элемент ИЛИ 121, первый элемент 122 задержки, третий комбинационньш сумма- тор 123, второй элемент 124 задержки.

В состав узла 75 квантования цифрового интегратора 3 (фиг. 7) входят первый элемент И 125, первый элемент 126 задержки, второй элемент 127 задержки, второй элемент И 128, первый элемент НЕ 129, третий элемент И 130, первый элемент ИЛИ 131, первый триггер 132, четвертый элемент И 133, второй элемент НЕ 134, пятый элемент И 135, второй элемент ИЛИ 136, второй триггер 137, шестой элемент И 138, седьмой элемент И 1 39,

Перед началом работы производится установка модуля ИВС в исходное состояние. При этом на вход 21 выбора модуля подается едининчный сигнал, который, пройдя через вход 32 ком- мутатора 1, открывает элемент И 56 и при подаче сигнала сброса через вход 22 модуля ИВС на вход 33 коммутатора 1 проходит через открытий элемент И 56 и поступает через вы- ход 36 на входы установки нуля регистров 4, 5 и счетчика 6, устанавливая их в нулевое состояние, а прой

5

Ю 5

20 25 О

0

5

0

5

дя через элемент ИЛIi 7, этот сигнал устанавливает в нулевое состояние триггеры 15 и 16. Кроме того, сигнал сброса с выхода 36 коммутатора I поступает на вход 39 формирователя 2 длительности импульсов и, пройдя через элементы ШП1 63 и ИЛИ 64, сбра- сьшает в нулевое состояние триггеры 65 и 66. Одновременно сигнал сброса поступает с выхода элемента И 56 через выход 36 коммутатора 1 в цифровой интегратор 3, через его вход 45 - на входы установки нуля регистров 72 и 76, устанавливая их в нулевое состояние, а пройдя с входа 45 цифрового интегратора 3 через вход 78 узла масштабирования и через элемент ИЛИ 98, устанавливает в нулевое состояние триггер 99. Кроме того, с выхода элемента ИЛИ 98 сигнал х:броса проходит через выход 84 узла 67 масштабирования и вход 88 входного узла 68 на нулевой вход триггера 119 и устанавливает его в нулевое состояние. Одновременно сигнал сброса с входа 45 цифрового интегратора 3 поступает на вход 93 узла 75 квантования и, пройдя через элементы ИЛИ 131 и 36, сбрасывает в нулевое состояние соответственно триггеры 132 и 137. Кроме того, сигнал сброса с выхода элемента И 56 проходит через элемент ИЛИ 57 и сбрасывает в нулевое состояние счетчик 59. Затем производится ввод начальных данных. При этом через вход 21 выбора модуля на вход 32 коммутатора 1 подается потенциал,поступающий на вход элемента И 60 и на входы элементов И 62 группы, а через группу 24 входов начальных данных модуля ИВС подаются на группу 35 входов коммутатора I параллельным кодом начал ьнве данные, которые поступают через группу входов 35 на вторые входы элементов И 62 группы и, пройдя через эти элементы И 62 и через группу информационных выходов 37 коммутатора 1, поступают на входы параллельной записи регистров 4 адреса входных приращений, регистра 5 адреса модуля и через

группу входов 51 начальных данных цифрового интегратора 3 поступают на входы параплельной записи регистра 72 подЕлнтегральной функции. Одновременно через вход 23 импульсов сопровождения данных модуля ИВС и через вход 34 в коммутатор I на второй вход элемента И 60 поступают 1шпульсы сопровождения тех начальных данных, которые одновременно поступают на входы параллельной записи регистров 4, 5 и 72. Эти Импульсы сопровождения данных проходят через элемент И 60 (на второй его вход поступает потенциап с входа 21 выбора модуля) на суммирующий вход счгтчика 59, состояние которого расшифровывается дешифратором 6 1 причем, при поступлении каждого нового импульса сопровождения данньк состояние счетчика 59 увеличивается на единицу и на соответствующем выходе дешифратора 61 появляется ничный сигнал, который поступает через соответствующий выход из группы выходов 38 коммутатора I на вход разрешения записи соответствующего регистра 4 (или 5) или через вход 46 цифрового интегратора 3 - на вход разрешения записи регистра 72, обеспечивая ввод начальной информахдаи, поступающей через элементы И 62 группы на входы параллельной записи этих регистров, в соответствующий регистр При этом в регистр 5 записывается ад р ес, соответствующий номеру модуля на структурной схеме рещения задачи и состоящий из номера группы модулей (от 1 до К) и номера модуля в группе (от 1 до п, , N, где N - число модулей в иве), причем поскольку номер каждой группы модулей в ИВС, кроме того, задается конструктивно при проектировании заданием соответствующего алгоритма неполному дешифратору 17, то при вводе адреса модуля имется ограничение. Этот адрес может вводиться только в те моду;ш ИВС, конструктивно заложенньй номер группы которых в ИВС совпадает с номером группы модуля на структурной схеме задачи в сводимом адресе. В регистры 4 заносятся соответствующие моду- . лю с этим адресом на структурной схеме задачи адреса входных приращений, т.е. номера тех модулей, которые по структурной схеме решения задачи соединены с соответствующим входом дан ного модуля. Адреса входных приращений также состоят из номера группы

модулей и номера модуля в группе, но тех ограничений, которые наложены на адрес модуля, в этом случае нет, так как в ИВС выходы любого модуля соединены с входами любого модуля с единственным ограничением в том плане, что объединение в шины за счет использования элементов с открыть коллектором прои зводится гюгруппн.о по п модулей в группе, что накладывает ограничение па адрес модуля. Последний импульс сопровождения данных перебрасывает счетчик 59 в последнее состояние, по готорому на последнем (1+2)-ом выходе дешифратора 61 появляется единичный сигнал, который поступает через (Т+2)-й выход из группы выходов 38 коммутатора 1 и через вход 46 цифрового интегратора 3 - на вход разрешения записи регистра 72 подынтегральной функции, в результате чего в регистр 72 записывается поступающее в этот момент времени на входы параллельной записи этого регистра соответствующее данному модулю начальное значение подынтегральной функции. Кроме того, единичный сигнал с последнего выхода дешифратора 61 поступает на вход элемента 58 задержки и, задержавшись на один такт на этом элементе, поступает через элемент ИЛИ 57 и сбрасывает счетчик 59 в нулевое состояние. На этом ввод начальных данньгх заканчивается.

г

Предлагаемьш модуль ИВС оперирует с одноразрядными приращениями, представленными в тернарной системе кодирования, т.е. имеющими три значения: +, О и -, поэтому обмен приращениями между модулями осуществляется по двум каналам - положительному и отрицательному. Выходные элементы И 19 и 20 модулей выполняются по схеме с открытым коллектором, что позволяет простым объединением их выводов реализовывать функцию Монтажное ИЛИ. Схема соединения процессоров между собой представлена на фиг. 8, на которой два выхода у, каждого модуля - это выход 29 положительных приращений и выход 30 отрицательных приращений модуля (показаны лишь входы и выходы, обеспечивающие связь модулей между собой,, а все остальные входы, обеспечивающие связь процессоров с другими устройствами ИВС, опущены).

Как видно из фиг. 8, выход 29 положительных приращений каждого модуля через Монтажное ИЛИ, объединяющее погруппно по п модулей в группе.

соединен с одним из К входов группы входов 27 положительных приращении каждого модуля (К - количество групп модулей), а выход 30 отрицательных приращений каждого модуля через Монтажное ИЛИ, объединяющее погруп пно по п модулей в группе - с одним из К входов группы входов 28 отрицательных приращений каждого модуля.

Модуль иве работает следующим образом.

По сигналу, разрешающему работу и поступакядему через вход 26 модуля на вход разрешения счета счетчика 6, этот счетчик начинает подсчитывать тактовые импульсы, поступающие на его счетньй вход с входа 25 модуля, последовательно изменяя свое состояние в каждой итерации от 1 до (n+m+1 где п N/K (N - количество модулей в иве, К - количество групп модулей, п - количество модулей в одной группе, m - количество разрядов в регистре подынтегральной функции модуля). При этом процесс решения на каждой итерации разбивается на два этапа: передачи приращений и вычислений. Этап передачи приращений происходит за первые п тактов, т.е. когда счетчик 6 изменяет свое состояние от 1 до п, а этап вычислений вьтолняется за m тактов, когда счетчик 6 изменяет свое состояние от п до {n+m) и ()-й такт используется для подготовки модуля к следующей итерации. Тогда при поступлении на вход 26 сигнала, разрешающего работу, последовательно изменяемые в каждом такте вследствие подсчета тактовых импульсов с 25 значения счетчика 6 начинают поступать в качестве адресов модулей в группах от 1 до п с единичных выходов каждого разряда этого счетчика параллельным кодом .На входы блока 9 сравнения адресов модуля и на входы блоков 8 сравнения адресов входных приращений. При совпадении адреса, пришедшего с выходов счетчика 6 на входы блока 9 сравнения с номером модуля в группе, записанным в регистр 5 и поступающим на входы блока 9 сравнения с выходов первой группы единичных выходов этого регистра, блок 9 сравнения выдает разрешающий сигнал на вход элемента И 18. В то же время при условии выполнения ограничения, заключающегося в том, что при вводе в регистр 5

418

адреса модуля на структурной схеме регаекия задачи этот адрес должен вво-; диться только в те модули ИВС, конструктивно заложенный номер группы ко- торых в ИВС совпадает с номером группы модуля на структурной схеме задачи в вводимом адресе, тогда на выходе дешифратора 17, на входы которого подается с вьгходов второй группы единичных вьгходов регистра 5 значение номера модуля в группе на структурной схеме задачи, а функция выхода которого определена конструктивно заложенным номером группы модулей в

ИВС, к которой относится данный мо20

25

, 3530

40

5

0

5

дуль, тоже присутствует с момента ввода адреса модуля в регистр 5 единичный сигнал, который открывает элемент И 18, поэтому разрешающий сигнал с выхода блока 9 сравнения проходит через открытьй элемент И 18 и поступает на входы элементов И 19 и 20, обеспечив прохождение одноразрядных приращений интеграла с вько- дов 54 и 55 цифрового интегратора 3 через соответственно элементы И 19 и 20, через выходы 29 и 30 модуля и через Монтажные ИЛИ соответствующей группы модулей из К таких групп на соответствующие входы 27 и 28 всех модулей ИВС. Таким образом, в один и тот же кюмент времени через Монтажные или соответствующих групп модулей из К таких групп к К входам 27 и 28 всех модулей ИВС подсоединяются выходы 29 и 30 К модулей (по одному из каждой группы). При совпадении адреса, поступающего с выходов счетчика 6, с номером, записанным в регистр 4 и поступающим на входы блока 8 сравнения с выходов первой группы единичных выходов регистра 4, соответствующий блок 8 сравнения выдает разрешающий сигнал на входы соответствующих элементов И 13 и 14, к вторьм входам которых подключаются в соответствии с К-м номером группы (К 1,2,,...,К), записанным в регистр 4 и поступающим с выходов второй группы выходов регистра 4 на управляющие входы коммутаторов 11 и 12, соответствующие этому номеру группы К-е входы из групп входов 27 и 28 и одноразрядные приращения интеграла, поступивиие в этот момент на К-е входы из групп входов 27 и 28 всех модулей (это одноразрядные приращения интеграла с выходов 29 и 30 того модуля, который на структурной схеме задачи соединен с данным входом данного модуля и, следовательно, адрес которого записан в соответствую1гем регистре А данного модуля), проходят через соответствующие коммутаторы 1 и 12 и открывшиеся элементы И I3 и 14 и записываются в соответствующих триггерах 15 и 16. Через п тактов счетчик 6 устанавливается в состояние, равное п, и происходит переад- реса1щя приращений последних п-х модулей иве в каждой группе модулей из К таких групп. На этом этап передачи приращений заканчивается и в следующем такте счетчик 6 переходит в состояние, равное (, и на соответствующем выходе дешифратора О появляется единичный сигнал, который поступает через вход 40 группы тактовых входов формирователя 2 на единичные входы триггеров 65 и 66 и перебрасывает их в единичное состояние. В результате триггер 66 начинает вы15 го регистра 72, значение подынтегральной функции, представленное в модифицированном дополнительном двоичном коде, поступает с выхода регистра 72 младшими разрядами вперед

20 на вход сумматора 69 и на первый вход 77 узла 67 масштабирования. В результате первая же единица в коде подьштегральной функции, являющаяся начальным импульсом, положение корабатьшать единичный сигнал длитель- торого зависит от масштаба представления величин, поступает в узел 67 масштабирования через вход 77, через открытый элемент И 100 и, задержавшись на один такт на элементе 101 задержки, перебрасьшает триггер 99 в единичное состояние, закрыв элемент И 100, и одновременно поступает через открытый элемент И 102 (на второй вход этого элемента, так же, как и на второй вход элементов И 104, 106 и на третий вход элемента И 100, поступает через вход 79 из формирователя 2 сигнал, разрешающий вычисления) и через выход 81 - во входной |узел 68 в качестве первого масштаб- ного импульса, соответствующего кванту подынтегральной функции, т.е. последнему, младшему, разряду. Кроме того, задержавшись на один такт на элементе 103 задержки, этот сигнал поступает s качестве второго масштабного импульса, соответствующего предпоследнему разряду подынтегральной функции, через открытый элемент И 104 и через выход 82 тоже во входной узел 68, а задержавшись еще на один такт на элементе 105 задержки, этот сигнал поступает уже в качестве третьего масштабного импульса через открытый элемент И 106 и через выход 83 - во входной узел 68.

ностью (т-2) такта, который поступает с единичного выхода триггера 66 через выход 44 формирователя 2 в цифровой интегратор 3 через вход 48 на вход управления сдвигом регистра 76 0 остатка интеграла. Так как модуль ИВС оперирует с одноразрядными приращениями, то в соответствии с алгоритмом его работы квантование неквантованного приращения интеграла произ- 35 водится следующим образом: квантованные одноразрядные приращения вьщеляют- ся в знаковых разрядах т-разрядного модифицированного кода неквантованного приращения интеграла, а оставшие- 40 ся числовые разряды этого кода без знаковых разрядов выделяются в качестве остатка интеграла, поэтому регистр 76 остатка интеграла имеет

(та-2) разрядов и сигнал управления сдвигом имеет длительность (т-2) тактов, а на единичном выходе триггера 65 одновременно начинает выраба- тьгоаться сигнал, разрешающий вычисление длительностью m тактов, который поступает через выход 43 формирователя 2 и через вход 47 в цифровой интегратор 3 на вход управления сдвигом регистра 72 подынтегральной функции, на управляющий вход узла 71 умноже- 55 ния, в узел 67 масштабирования через третий его вход 79,на третий вход элемента И 100 и на вторые входы эле. 57641 О

ментов И 102, 104 и 106, а также в узел 75 квантования через третий его вход 84 на второй вход элемента И 125 и разрешает выполнение в этом цифро5 вом интеграторе 3 операции численного интегрирования. Начинается этап вычислений длительностью m тактов от (п+1) до (п+т), в Течение которого на вход управления сдвигом регист10 ра 72 поступает с вькода триггера 65 разрешающий сигнал и по тактовьгм им- пульсам поступающим с входа 25 модуля через вход 50 цифрового интегратора 3 на вход синхронизации это15 го регистра 72, значение подынтегральной функции, представленное в модифицированном дополнительном двоичном коде, поступает с выхода регистра 72 младшими разрядами вперед

20 на вход сумматора 69 и на первый вход 77 узла 67 масштабирования. В результате первая же единица в коде подьштегральной функции, являющаяся начальным импульсом, положение которого зависит от масштаба представления величин, поступает в узел 67 масштабирования через вход 77, через открытый элемент И 100 и, задержавшись на один такт на элементе 101 задержки, перебрасьшает триггер 99 в единичное состояние, закрыв элемент И 100, и одновременно поступает через открытый элемент И 102 (на второй вход этого элемента, так же, как и на второй вход элементов И 104, 106 и на третий вход элемента И 100, поступает через вход 79 из формирователя 2 сигнал, разрешающий вычисления) и через выход 81 - во входной |узел 68 в качестве первого масштаб- ного импульса, соответствующего кванту подынтегральной функции, т.е. последнему, младшему, разряду. Кроме того, задержавшись на один такт на элементе 103 задержки, этот сигнал поступает s качестве второго масштабного импульса, соответствующего предпоследнему разряду подынтегральной функции, через открытый элемент И 104 и через выход 82 тоже во входной узел 68, а задержавшись еще на один такт на элементе 105 задержки, этот сигнал поступает уже в качестве третьего масштабного импульса через открытый элемент И 106 и через выход 83 - во входной узел 68.

Одновременно одноразрядные приращения, представленные в тернарной

системе кодирования, поступают с выходов i-x триггеров 15 положительных

„ .Т.:

приращении и I X триггеров 1о отрицательных приращений (г 2,3,..,) в виде потенциалов, соответствующих +1 или -1, через соответствующие i-e входы групп входов положительных 52 и отрицательнггх 53 значений входных приращений цифрового интегратора 3 и через (i-l)-e входы групп входов 89 и 90 входного узла 68 (i 2,3,...,l) - на входы соответственно комбинационного сумматора 107 и комбинационного сумматора М2. При этом в комбинационном сумматоре 107 происходит суммирование положительных приращений, а в комбинационном сумматоре 112 - отрицательных приращений. Получившиеся суммы положительразрядных параллельньк кодов соответ ственно суммы положительных приращений и суммы отрицательных приращений; третий масщтабньп импульс, так же, как и старщие разряды трехразрядных параллельных кодов сумм приращений, поступает на входы элементов И ПО и П5. В результате масштабные сигналы, вырабатьшаемые узлом 67

О масштабирования, приводят суммы положительных и отрицательных приращений к масштабу подынтегральной функции данного модуля ИВС и переводят их из параллельного двоичного кода в по15 следовательный. При этом количество масштабных сигналов, вырабатьшаемых узлом 67, зависит так же, как и количество выходов у cy Iaтopoв 107 и 112, от числа одновременно суммируных и отрицательных приращений посту- 20 емых приращений подынтегральной фун25

пают соответственно с выходов сумматоров 107 и 112 параллельным трехразрядным кодом (число разрядов в этих кодах, равное числу выходов у этих сумматоров, не превышает трех, так как число одновременно суммируемых приращений подынтегральной функции, а следовательно, и число входов входного узла, т.е. число входов по подынтегральной функции цифрового ин-30 тегратора, не превышает семи и на практике равно обычно 3-5) на первые входы соответственно элементов И 108, 109, ПО и элементов И 113, 114, 115, на вторые входы которых поступают со-33 ответственно с выходов 81, 82, 83 узла масштабирования 67 через входы 85, 86, 87 входного узла 68 первый, второй и третий масштабные импульсы в соответствии с весом разряда парал- J лельного трехразрядного кода суммы приращений. При этом первьй масштаб- ньй импульс, соответствующгш кванту подынтегральной функции, т.е. последнему, младшему, разряду, поступает 45 через вход 85 входного узла 68 на втоI

рые входы элементов И 108 и 113, на первые входы которых поступают мпад- шие разряды трехразрядных параллельных кодов соответственно суммы положительных приращений и суммы отрицательных приращений; второй масштабный импульс, соответствующий предпоследнему разряду подынтегральной

50

кции и практически не превьшает тре так как максимальное число одновременно суммируемых приращений подын- тегралькрй функции как теоретически так и практически не превьипает семи I

Последовательный код суммы положительных приращений, приведенньй к масщтабу подынтегральной функции дан ного модуля ИВС, с выхода элемента ИЛИ I11 поступает на первый вход комбинационного сумматора 123, а последовательный код суммы отрицательных приращений, поступающий с выхода элементов ИШ 116, сначала преобразуется в дополнительньй код, а потом с выхода элемента ИЛИ I21 поступает на второй вход сумматора 123. При этом образование дополнительного ко- ;да суммы отрицательных приращений производится следующим образом. Первая единица в последовательном коде суммы отрицательных приращений, поступающая с выхода элемента ИЛИ 116, проходит через открытьй элемент И 118 (на второй вход этого элемента посту пает едш{ичньгй сигнал с нулевого выхода триггера 119, так как этот три:- гер был установлен в нулевое состояние при подготовке к решению сигналом сброса) и поступает без изменения через элемент ИЛИ 121 на второй вход сумматора 123, а задержавшись на один такт на элементе 122 задержки, эта единица поступает на единич-

функции, поступает через вход 86 вход- ньй вход триггера 119 и перебрасьтаного узла 68 на вторые входы элементов И 109 и Р4, на первые входы которых поступают средние разряды трехет его в единичное состояние. В результате триггер I 19 закрьтает элемент И 118 и открывает элемент И 120

разрядных параллельньк кодов соответственно суммы положительных приращений и суммы отрицательных приращений; третий масщтабньп импульс, так же, как и старщие разряды трехразрядных параллельных кодов сумм приращений, поступает на входы элементов И ПО и П5. В результате масштабные сигналы, вырабатьшаемые узлом 67

масштабирования, приводят суммы положительных и отрицательных приращений к масштабу подынтегральной функции данного модуля ИВС и переводят их из параллельного двоичного кода в последовательный. При этом количество масштабных сигналов, вырабатьшаемых узлом 67, зависит так же, как и количество выходов у cy Iaтopoв 107 и 112, от числа одновременно суммиру25

30 33 J 5 0

кции и практически не превьшает трех, так как максимальное число одновременно суммируемых приращений подын- тегралькрй функции как теоретически, так и практически не превьипает семи. I

Последовательный код суммы положительных приращений, приведенньй к масщтабу подынтегральной функции данного модуля ИВС, с выхода элемента ИЛИ I11 поступает на первый вход комбинационного сумматора 123, а последовательный код суммы отрицательных приращений, поступающий с выхода элементов ИШ 116, сначала преобразуется в дополнительньй код, а потом с выхода элемента ИЛИ I21 поступает на второй вход сумматора 123. При этом образование дополнительного ко- ;да суммы отрицательных приращений производится следующим образом. Первая единица в последовательном коде суммы отрицательных приращений, поступающая с выхода элемента ИЛИ 116, проходит через открытьй элемент И 118 (на второй вход этого элемента поступает едш{ичньгй сигнал с нулевого выхода триггера 119, так как этот три:- гер был установлен в нулевое состояние при подготовке к решению сигналом сброса) и поступает без изменения через элемент ИЛИ 121 на второй вход сумматора 123, а задержавшись на один такт на элементе 122 задержки, эта единица поступает на единич-

ньй вход триггера 119 и перебрасьтает его в единичное состояние. В результате триггер I 19 закрьтает элемент И 118 и открывает элемент И 120

13

интеграла. Полученное в результате суммирования на сумматоре 73 значение неквантованного приращения интеграла поступает на вход узла 75, где происходит вьщеление нового значения квантованного приращения интеграла, и в регистр 76, в который записывается вьщеленный иовый остаток интеграла, представляющий собой в соответствии с алгоритмом работы цифрового интегратора с одноразрядными приращениями значение неквантованного приращения интеграла без знаковых

Ш

и весь оставшийся последовательный код суммы отрицательных приращений, проинвертировавшись на элементе НЕ П7, поступает в инверсном виде чаре: от- крытьй элемент И 120 и элемент ИЛИ 12J на второй вход сумматора 123, Обра- зованиьй таким образом дополнительньтй код суммы отрицательных приращений, поступающий с выхода элемента ИЛИ 121, суммируется на сумматоре 123 с суммой положительных приращений, поступающей с выхода элемента ШШ 111, и общая сумма приращений подынтегр,зль- ной функции поступает с выхода сумматора 123 йа выход 91 входного уз- is fta 68. В цепь переноса сумматора 123 включен однотактный элемент задержки 2А, служащий для образования поразрядного переноса при суммировании суммы положительных приращений с сум- 2о и подачей из формирователя 2 с выхоразрядов, а знаковые разряды определяют значение квантованного приращения интеграла. При этом вьделение нового значения остатка интеграла производится использованием укороченного регистра, имеющего (т-2) разрядов.

мой отрицательных приращений. Полученная общая сумма входньпс приращений подынтегральной функции поступает с выхода 9 входного узла 68 на :вход сумматора 69, на другой вход ко- торого поступает из регистра 72 зна- подынтегральной функции. В цепь переноса сумматора 69 включен однотактный элемент 70 задержки, служащий для образования переноса при сложении общей суммы входньгх приращений подынтегральной функции с текущим значением подынтегральной функции. Получающееся в результате суммирования на сумматоре 69 новое значение подынтегральной функции,поступает в регистр 72 и на вход первого сомножителя узла 71 умножения, где происходит приращение переменной интегрирования, также представленное

в тернарной системе кодирования и поступающее на входы второго сомножителя узла 71 умножения с выходов первого триггера 15 положительных приращений группы и первого триггера 6 отрицательных приращений группы через первые входы из групп входов положительных значений 52 и отрицательных значений 53 входных приращений цифрового интегратора 30. Результат умножения поступит на вход сумматора 73 остатка интеграла, а на другой вход этого сумматора поступает значение остатка интеграла из регистра 76. В цепь переноса сумматора 73 включен однотактный элемент 74 задержки, служащий для образования переноса при сложении результата умножения с текущим значением остатка

11-4

интеграла. Полученное в результате суммирования на сумматоре 73 значение неквантованного приращения интеграла поступает на вход узла 75, где происходит вьщеление нового значения квантованного приращения интеграла, и в регистр 76, в который записывается вьщеленный иовый остаток интеграла, представляющий собой в соответствии с алгоритмом работы цифрового интегратора с одноразрядными приращениями значение неквантованного приращения интеграла без знаковых

и подачей из формирователя 2 с выхои подачей из формирователя 2 с выхоразрядов, а знаковые разряды определяют значение квантованного приращения интеграла. При этом вьделение нового значения остатка интеграла производится использованием укороченного регистра, имеющего (т-2) разрядов.

да триггера 66 на вход управления сдвигом регистра 76 ( )-тактного

5

5 о

0

сигнала управления сдвигом, по которому в регистр 76 записываются по тактовым импульсам, поступающим с входа 25 модуля через вход 50 на вход синхронизации этого регистра, лишь числовые разряды без знаковых, и по (п+1п-1)-му такту дешифратор 10 выдает через вход 41 из группы тактовых входов формирователя 2 и через элемент ИЛИ 64 на нулевой вход трих- гера 66 единичный сигнал, по которому триггер 66 формирователя 2 переходит в нулевое состояние и сдвиг информации в регистре 76 прекращается. Оставшиеся знаковые разряды, которые определяют значение квантованного приращения интеграла, анализируются в узле 75. Это выполняется следующим образом. Значение неквантованного приращения интеграпа, поступающее с выхода сумматора 73, проходит через вход 92 узла 75 и поступает на

вход элемента И 125, А так как на второй вход элемента И 125 поступает через вход 94 из формирователя 2 сигнал, разрешающий вычисления, то это значение неквантованного приращения интеграла проходит через элемент И 125 и поступает на лход элемента 126 задержки, задерживается на этом элементе задержки на такт (эта задержка выполняется для того, чтобы первьп (старший; знаковьй разряд совпал по времени с сигналом подготовки модуля иве к следующей итерации, появляющимся на выходе дешифратора 10 по окон5

0

15

чании этапа вычислений в (п+ш+О-ом такте и поступает на вход элемента И 128 и череэ элемент НЕ 129 - на вход элемента И 130, а задержавшись еще на один такт на элементе задержки 127 (эта задержка вьтолняется для того, чтобы и второй (младший) знаковый разряд, следующий на такт раньще первого (старшего) знакового разряда совпал по времени с сигналом подготовки модуля иве к следующей итерации появляющимся на выходе дешифратора 1 по окончании этапа вычислений в (п+ +т+1)-ом такте, с целью обеспечения возможности одновременного анализа обоих знаковых разрядов), поступает на вход элемента И 133 и через элемент НЕ 134 - на вход элемента И 135 А на вторые входы элементов И 128, 130, 133 и 135 поступает по окончании этапа вычислений в (п+т+1)-ом такте с выхода дешифратора 10 через вход 49 цифрового интегратора 3 и через вход 95 узла 75 сигнал подготовки модуля иве к следующей итераций, так как счетчик 6 устанавливается в этом такте тоже в состояние, равное (n+m+l), в результате по этому сигналу триггеры 132 и 137 устанавливаются в состояния, соответствующие старшему и младшему знаковым разрядам, т.е. триггер 132 анализирует знак, а триггер 137 - переполнение знакового разряда. Поскольку квантованные приращения интеграла являются одноразрядными и представляются в тернарной системе кодирования, то кодирование приращений осуществляется следующим образом: 01 - 41, П - -1 и 00 - О, т.е. если по сигналу подготовки модуля иве к следующей итерации, появляющемуся на выходе дешифратора 10 по окончании этапа вычислений в (п-«-зп+1)- ом такте, триггер 132 устанавливает- ся в нулевое состояние, а триггер 137в единичное, то ни выходе элемен- 1

та И 138 появляется единичный сигнал длительностью одной итерации, соответствующий положительному приращению интеграла +1, который через выход 96 узла 75 и через выход 54 цифрового интегратора 3 поступает на вход элемента И 19 положительных приращений; если по сигналу подготовки модуля иве к следующей итерации в (п+т+О-ом тат re в единичное состояние устанавливаются оба триггера 532

5 0 5 5764 и

16

137, то единичньй сигнал длительностью одной итерации, соответствующий отрицательному приращению интеграла -1, появляется на выходе эле- с мента И 139 и поступает через выход 97 узла 75 и через выход 55 цифрового интегратора 3 на вход элемента И 20 отрицательных приращений. Если же оба триггера 132 и 137 оказьша}0 ются в нулевом состоянии, то приращения на выходы 96 и 97 узла 75 не выдаются, что соответствует значению приращения интеграла равного О. Одновременно в (n+m+1)-ом такте из

15 дешифратора 10 в формирователь 2 через вход 42 из группы тактовых входов и через элемент ИЛИ 63 на нулевой вход триггера 65, вьфабатываю- щего сигнал разрешения вычислений,

20 поступает единичный сигнал, который перебрасывает этот триггер 65 формирователя 2 в нулевое состояние, прекращая подачу сигнала разрешения вычислений через выход 43 формировате25 ля 2 на вход 47 цифрового интегратора 3 и завершая этап вычислений длительностью m тактов. Кроме того, появившийся в (п+1п+1)-ом такте, используемом для подготовки модуля иве к следзгкяцей итерации, на выходе дешифратора 10 (вследствие того, что счетчик 6 устанавливается в состояние, равное п+п+1) сигнал установки в исходное состояние поступает с выхода дешифратора 10 через элемент ИЛИ 7 на нулевые входы триггеров 15

и 16, подготавливая их к этапу передачи приращений в следующей итерации, а также этот сигнал поступает через вход 49 цифрового интегратора 3 в узел 67 масштабирования, через четвертый его вход 80 и через элемент ИЛИ 98 - на нулевой вход триггера 99, устанавливая его Б нулевое состояние, е выхода элемента ИЛИ 98 этот сигнал поступает через выход 84 узла 67 и через вход 88 узла 68 на нулевой

0

вход триггера И9, устанавливая его в кулевое состояние и подготавливая тем самьм узлы 67 и 68 к этапу вычислений в следующей итерации. Одновременно этот сигнал с выхода дешифратора 10, соответствующий состоянию счетчика 6, равному (n+m+l), поступает через выход 31 модуля ИВе в центральное устройство упрявления иве и в случае совпадени) -irirx сигналов, поступакнцих в центрлльное устto

20

25

ойство управления ИВС с выходов 31 всех модулей ИВС, свидетельствующем об отсутствии сбоев в процессе счета на первой итерации, центральное устройство управления ИВС продолжает выдавать сигнал, разрешающий работу, на входы 26 всех модулей ИВС для следующей итерации. Первый же тактовый импульс, поступающий в первом такте следующей итерации на вход 25 модуля ИВС, перебрасывает счетчик 6 из состояния (n+m+O в состояние, равное единице, при этом счетчик 6 является счетчиком по модулю (n+m+l), и начнется вторая итерация, в течение ко- тррой за п тактов происходит переадресация приращений и за m тактов выполняется операция численного интегрирования, а в (п+т+1)-й такт происходит подготовка модуля ИВС к следующей итерации, а также контроль процесса счета центральньв- устройством управления ИВС. В случае отсутствия сбоев в процессе счета центральное устройство управления ИВС продолжает выдавать сигнал, разрешающий работу, на вход 26, а в следующем такте счетчик 6 переходит из состояния (n+m+l) в состояние, равное единице, и начинается новая итерация и т.д. В случае, если при контроле процесса счета в (n+m+l)-OM такте какой-либо итерации центральным устройством управления ИВС обнаруживается отсутствие в этом такте сигнала с выкоДа 31 хотя бы одного модуля ИВС, что свидетельствует о наличии сбоя в процессе , счета, центральное устройство управления ИВС прекращает вьщавать сигнал, разрещающий работу, на входы 26 моду-4о лей ИВС, и процесс решения останавливается.

Формула изобретения , .

Модуль интегрирующей вычислительной структуры, содержащий коммутатор начальных значений, формирователь длительности импульсов, цифровой интегратор, регистр адреса модуля, группу из I регистров адреса входных приращений (где I - число входных приращений цифрового интегратора), счетчик тактов , блок сравнения адресов модуля, группу из I блоков сравнения ад- ресов входных приращений, группу из I триггеров положительных приращений, группу из I триггеров отрицательных

15

30

35

50

o

0

5

о

приращений, группу из I входных элементов И положительных приращений, группу из I входных элементов И отрицательных приращений, выходной элемент И положительных приращений, выходной элемент И отрицательных приращений, элемент ИЛИ, неполный дешифратор тактов, причем выход установки в исходное состояние коммутатора начальньгх значений соединен с входом сброса формирователя длительности импульсов, с входом установки в исходное состояние цифрового интегратора, с входом установки нуля i-ro регист- 5 ра адреса входных приращений группы

(i 1,2,,1), с входом установки

нуля регистра адреса модуля, с входом установки нуля счетчика тактов и с первым входом элемента ИЛИ, i-й выход группы выходов импульсов сопровождения начальных данных коммутатора начальных значений соединен с входом разрешения записи i-ro регистра адреса входных приращений

группы (i 1,2,...,), (1+1)-й выход группы выходов импульсов сопровождения начальных данных коммутатора начальных значений соединен с входом разрешения записи регистра адреса модуля, первая группа выходов которого соединена с первой группой входов блока сравнения адресов модуля, вторая группа входов которого соединена с выходами счетчика тактов, первая группа выходов i-ro регистра адреса входных приращений группы соединена с первой группой входов i-ro блока сравнения адресов входных приращений групгш, вторая группа входов которого соединена с выходами счетчика тактов, а выход i-ro блока сравнения адресов входных приращений группы соеда1нен с первьм входом i-ro входного элемента И положительных приращений групп и с первым входом 1-го входного элемента И отрицательных приращений группы, выходы которых соединены соответственно с единичным входом i-ro триггера положительных приращений группы и с единичным входом i-ro триггера отрицательных приращений группы, единичные вькодь которых соединены соответственно с i-ми входами из групп входов положительных и отрицательных значений входных приращений цифрового интегратора, входы неполного дешифратора тактов соединены с выходами счет0

5

0

чнка TaKTOFi, выходы состояния (п +1) где п N/K, N - количество модулей в интегрирующей вычислительной структуре; К - количество групп модулей; п - количество модулей в одной группе, состояния (п+га-1) и состояния (n+m+1) неполного дешифратора тактов где m - количество разрядов в регистре подынтегральной функции цифрового интегратора, соединены соответственн с первым, вторым и третьим входами формирователя длительности импульсов, нулевой вход каждого триггера положительных приращений группы и каждого триггера отрицательных прира щений группы соединены с выходом элемента ИЛИ, второй вход которого соединен с выходом состояния (n+m+I) неполного дешифратора тактов, выходы сигнала длительностью m тактов и сиг нала длительностью (in-2) тактов формирователя длительности импульсов и выход состояния (n+m+1) неполного дешифратора тактов соединены соответственно с входом разрешения вычислений с входом вьщеления остатка интеграла и с входом конца итерации цифрового интегратора, выходы положительного и отрицательного приращений интеграла которого соединены соответственно с первым входом выходного элемента И положительных приращений и с первым входом выходного элемента И отрицательных приращений, выходы которых соединены с выходами положительных и отрицательных приращений, модуля соответственно, первьй, второй и третий входы коммутатора начальных значений соединены с входом выбора модуля, с входом сброса модуля и входом импульсов сопровождения данных модуля соответственно, а группа входов коммутатора начальных значений соединена с группой входов начальных данных модуля, вход синхронизации цифрового- интегратора и счетный вход, счетчика тактов соединены с входом тактовых сигналов модуля, вход разрешения ра- ооты модуля соединен с входом разрешения счета счетчика тактов, выход состояния (n+m-t-1) неполного дешифратора тактов соединен с выходом контроля тактов модуля, информационные

to

J5 2025д s

30

35

0

выходы коммутатора начапьных значений соединены с входами начальных данных цифрового интегратора, с информационными входами регистра адреса модуля и с информационными входами каждого регистра адреса входных приращени, выход (1+2)-го импульса из группы выходов импульсов сопровождения начальных данных коммутатора начальных значений соединен с входом разрешения записи начапьных данных цифрового интегратора, о т - личающийся тем, что, с целью повышения быстродействия за счет сокращения времени обмена информацией, в него дополнительно введены группа из I коммутаторов положительных приращений, группа из I коммутаторов отрицательных приращений, элемент И разрешения вьщачи и неполный дешифратор адреса, причем вторая группа выходов регистра адреса модуля соединена с входами неполного дешифратора адреса, выход которого соединен с первым входом элемента И разрешения вьщачи, второй вход которого соединен с В1з1ходом блока сравнения адресов модуля, а выход соединен с вторым входом выходного элемента И положительных приращений и с вторым входом выходного элемента И отрицательных приращений, вторая группа выходов i-ro регистра адреса входных приращений группы соединена с группой управляющих входов i-ro коммутатора положительных приращений группы и с группой управляющих входов i-ro коммутатора отрицательных приращен1ш группы, выходы которых соединены с вторым входом i-ro входного элемента И положительных приращений группы и с вторым входом i-ro входного элемента И отрицательных приращений группы соответственно, К-ый вход из группы информационных входов каждого коммутатора положительньгх приращений группы и вход из группы информационных входов каждого коммутатора отрицательных приращений группы (К 1,2,...,К) соединены соответственно с К-ми входами из групп входов положительных и отрицательных приращений модуля.

r;j л 2 W j. u

,r ;..

r

(uz2

ад

4J

U- f L1j

«IzJ

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| НЕПРЕРЫВНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1969 |

|

SU241121A1 |

| Устройство для диагностики неисправностей цифровых интеграторов | 1979 |

|

SU877551A1 |

| Устройство цифрового интегрирования | 1988 |

|

SU1532922A1 |

Изобретение относ«тся к области вычислительной техники и предназначено для использования в интегрирующих вычислительных структурах. Целью изобретения является повышение быстродействия за счет сокращения времени обмена информацией. Модуль содержит коммутатор начальных значений, формирователь длительности импульсов, цифровой интегратор, группу регистров адреса входных превращений, регистр адреса модуля, счетчик тактов , элемент ИЛИ, блоки сравнения адресов входных приращений, блок сравнения адресов модуля,.неполные дешифраторы тактов и адреса, коммутатор положительных приращений, ком таторы отрицательных приращений, триггеры отрицательных и положительных приращений, элементы И, Положи- тельньй эффект достигается введением группы мультиплексоров положительных приращений, группы мультиплексоров отрицательных приращений, элемента И и второго неполного дешифратора. 8 ил. (О

j:

21

6Л

ira

a

7

-H 7J

5,

JL-l

л::

5

ад

77

7#

i

s

fO

т

Ss

wj

lOt

w

7J

.5

Ж

т

«

e

fW

-i

4

2

Ь0

5T

r in

i

ТЯ)

c;

Составитель Г. Пономарева Редактор . Швьщкая Техред И.Попович PP I I L :-- - - -ЗакаГ4957/ 7 Тираж 67 . Подписное ВНИИПИ Государственного комитета GCCP

по делам изобретений и открытий 113035, Москва, Ж-35, Раугаская наб., д. /5

Проиаводственно-поляг

-рафическое предприятие, г. Ужгород, ул. Проектная,4

| Авторское свидетельство СССР № 646854, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-15—Публикация

1984-05-22—Подача