1

.гИзобретение относится к цифровой вычислительной технике и может быть использовано в. вычислительных системах, работающих в избыточной системе счисления.

Известно устройство, содержащее сумматор-, регистр, элемент ИЛИ и блок анализа разрядов, которое производит сложение чисел в избыточной системе счисления последовательно старшими разрядами вперед Cl.

Недостатками устройства является низкое быстродействие и сложение чисел только в двоичной системе счисления .

Известно устройство, содержащее два двухразрядных сумматора, три элемента задержки и блок формирования результата; которое производит сложение чисел последовательно старшими . разрядами вперед с высоким быстродействием 2.,

однако устройство имеет возможность сложения только в двоичной .избыточной системе счисления с цифрами 1,0 и 1.

Наиболее близким к предлагаемому является устройство, содержащее два комбинационных сумматора, две логические схемы выработки положительного и отрицательного переноса, группу элементов ИЛИ и реверсивный счетчик, которое производит сложение чисел в избыточной системе счисления с про11звольным основанием Р и цифрами р-1, ..., Т,О, 1, ... р-1. з1.

Недостатком устройства является большое количество оборудования, так как оно работает только в параллель0ном режиме.

Цель изобретения - сокращение количества оборудования, которое достигается за счет возможности последовательного сложения чисел в избыточ5ной системе счисления с произвольным основанием Р.

Поставленная цель достигается тем, что в устройство для сложения в избыточной системе счисления, содержащее первый комбинационный сумматор, входы которого соединены с шинами входных аргументов, блоки выработки положительного и отрицательного переносов, входы которых соединены с выходом первого сумматора, шифратор, входы которого соединены с выходами блоков выработки положительного и отрицательного переносов, второй сумматор, первый вход которого соединен

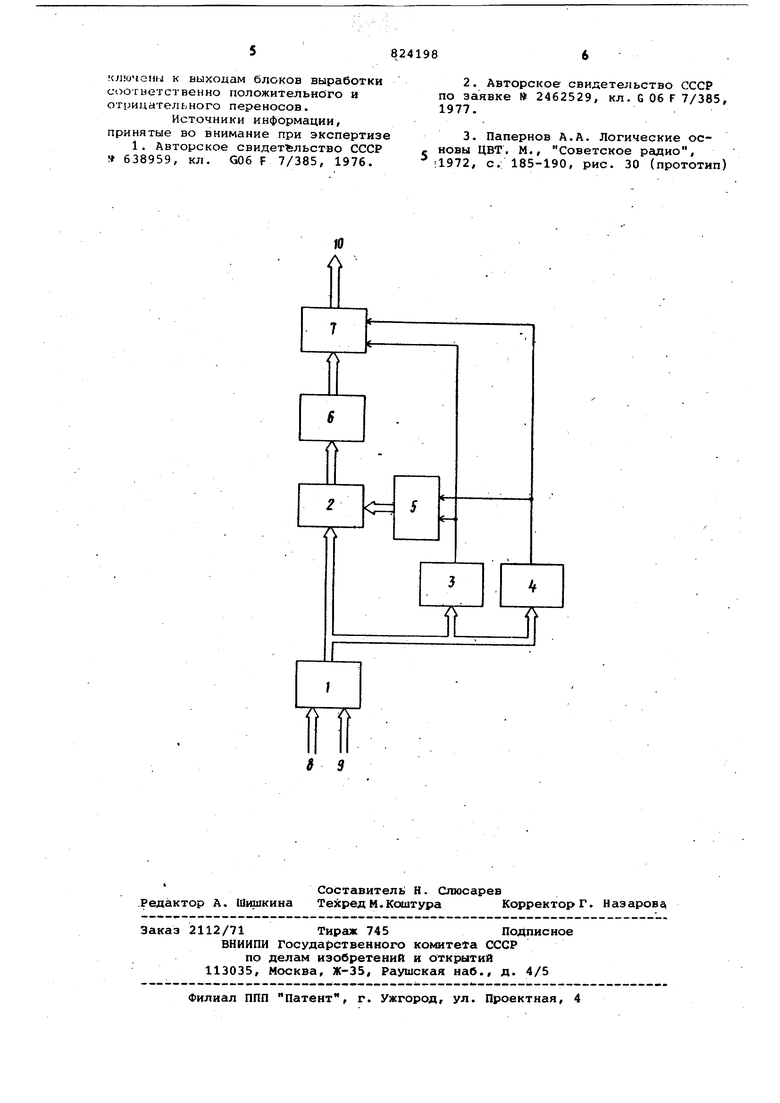

0 с выходом первого сумматора, а второй вход подключен к выходу шифратор реверсивный счетчик, выход-которого соединен с выходной ценной устройства введен регистр, вход которого подклю чен к выходу второго сумматора, а выход соединен со входом реверсивного счетчика, суммирующий я вычитаю,щий входы которого подключены к выходам блоков выработки соответственно, положительного и отрицательного переносов. На чертеже приведена структурная схема устройства для сложения чисел в избыточной системе счисления. Устройство содержит первый и второй комбинационные сумматоры 1 и 2, Олоки 3 и 4 выработки положительного и отрицательного переносов, шифратор 5, регистр 6 и реверсивный сч чик 7. Входы первого сумматора 1 подклю чены к шине 8 первого входного аргумента и шине 9 второго входного аргумента, а выходы первого суммато ра 1 соединены с первыми входами второго сумматора 2 и с входами бло ков 3 и 4 выработки переносов. Втор вход второго сумматора 2 подключен выходу шифратора 5, входы которого соединены с выходами блоков 3 и 4 в работки положительного и отрицатель ного переносов и с суммирующим и вычитающим-входами реверсивного сче чика 7. Выход второго сумматора 2 соединен с входом регистра 6, вход которого подключен ко входу реверси ного счетчика 7, соединенного по вы -ходу с выходной шиной 10 устройства Устройство работает следующим об разом. На входы первого комбинационного устройства по шинам 8 и 9 последова тельно разряд за разрядом, начиная со старшего, поступают суммируем1 1е аргументы, выра хенные в избыточной системе счисления с осно ванием Р и системой цифр р-1, ..., 1, О, 1, .. р-1. Каждый i-П разряд входных аргументов поступает в устройство в виде (k+l)-ro разрядного двоичного кода 1 ) старший разряд-которого является знаковым. При этом положительные значения вход ных аргументов подаются в прямом ко де, а отрицательные - в дополнительном. На выходе, первого сумматора 1 образуется сумма 3 i-тых разрядов входных аргументов а-и Полученнс1я сумма S,- поступает на входы второго комбинационного сумматора 2 и блоков 3 и 4 выработки поло жительного и отрицательного переносов. В зависимости от величины полученной суммы блоки 3 и 4 Бырабаты;гаюг си1-налы i.epeaoc алгоритму Г1 при S,- р-( П . -I Т при SjJ f-j о iфИpи S pьлоки 3 и 4 выработки переносов представляют собой логические блоки, входными сигн алами которых являются значения разрядов суммы S-, структура определяется значением основания системы Р. Шифратор 5 выдает на второй вход второго сумматора 2 число Р (если ) или минус Р (если П-1). Таким образом, на выходах второго сумматора 2 получают следующие значения суммы S/ ( S -р при Ш Т S-- при П-1 1 ( при Полученная сумма S с выхода второго сумматрра-2 заносится в регистр б. В следующем ( i -t-1) -м также работы устройства сумма с выхода регистра 6 заносится в реверсивный счетчик 7, где и к ней добавляется Т или 1 при наличии отрицательного или положительного переносов на выходах блоков 3 и 4. С выхода реверсивного счетчика 7 по выходной шине 10 устройства снимаются разряд за разрядом, начиная со старшегй разряда, результаты суммирования аргументов а и Ь. Таким образом, введение регистра позволило производить последовательное суммирование чисел в избыточной системе счисления с произвольным основанием Р и системой цифр р-1, ..., 1, О, 1, ..., р-1, что дает выигрыш- в оборудовании, примерно в П раз (где п - число разрядов суммируемых аргументов). Формула изобретения Устройство для сложения в избыточгной системе счисления, содержащее первый сумматор, входы которого подключены к шинам входных аргументов, блоки выработки положительного и отрицательного переносов, входы которых соединены с выходом первого сумматора, шифратор, входы которого подключены к выходам блоков выработки положительного и отрицательного переносов, второй сумматор, первый вход которого подключен к выходу первого сумматора, а второй вход соединен с выходом шифратора, реверсивный счетчик, выход которого подключен к ВЫХОДНОЙ шине устройства, отличающееся тем, что, с целью сокращения количества оборудования, оно содержит регистр, вход которого подключен к выходу второго сумматора, а выход соединен со входом реверсивйого счетчика, суммирующий н вычитающий входы которого подключаны к выходам блоков выработки соответственно положительного и отрицательного переносов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР f 638959, кл. G06 F 7/385, 1976.

2.Авторское свидетельство СССР по заявке 2462529, кл. G 06 F 7/385, 1977.

3.Папернов А.А. Логические ос-новы ЦВТ. М., Советское радио,

11972, с. 185-190, рис. 30 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения чисел в из-быТОчНОй СиСТЕМЕ СчиСлЕНия | 1979 |

|

SU824199A1 |

| Устройство для сложения в избыточной системе счисления | 1980 |

|

SU924698A1 |

| Устройство для сложения чисел в избыточной системе счисления | 1978 |

|

SU763896A1 |

| Устройство для вычисления квадратного корня | 1985 |

|

SU1254477A1 |

| Устройство для вычисления логарифма | 1984 |

|

SU1262489A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для сложения в избыточной двоичной системе счисления | 1977 |

|

SU696450A1 |

| Устройство для сложения в избыточной двоичной системе | 1977 |

|

SU717763A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

Авторы

Даты

1981-04-23—Публикация

1979-06-27—Подача