N9

О N9

41

00 СО

Изобретение относится к вычислительной технике, в частности к устройствам для выполнения математических операций, и может быть использовано в быстродействующих ЦВМ, а также при построении специализированных процессов вычислительных систем высокой производительности.

Цель изобретения - повышение быстродействия устройства путем сокращения времени выполнения каждой итерации.

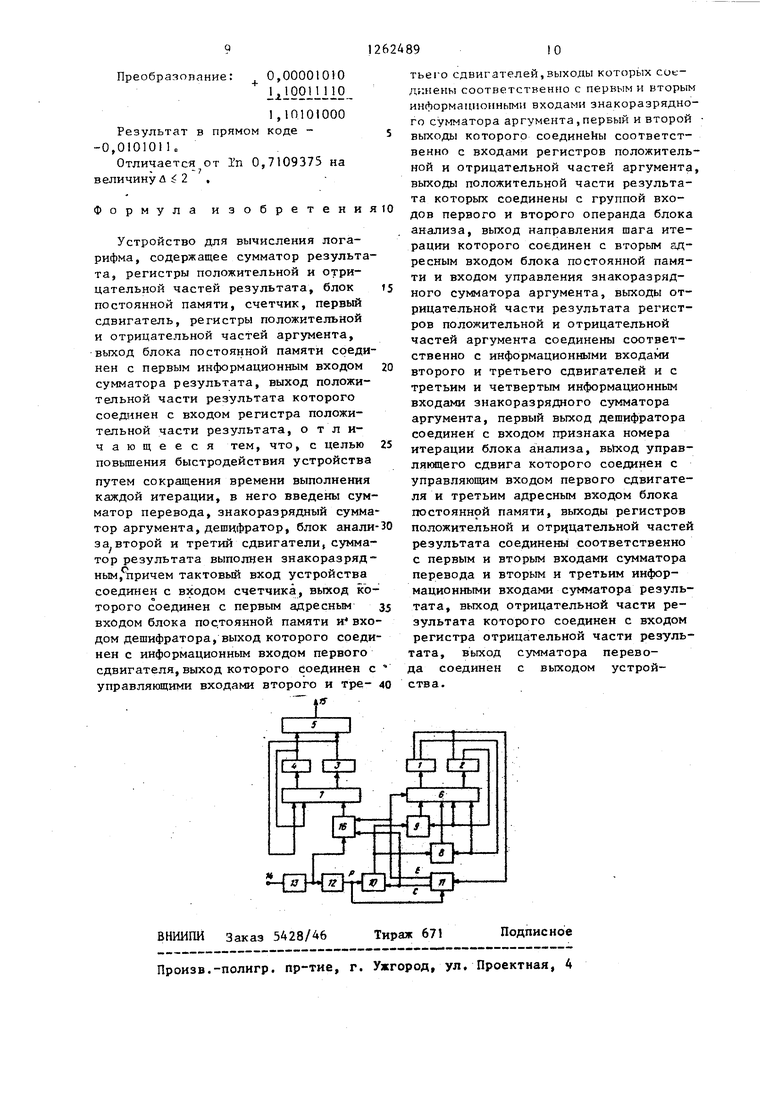

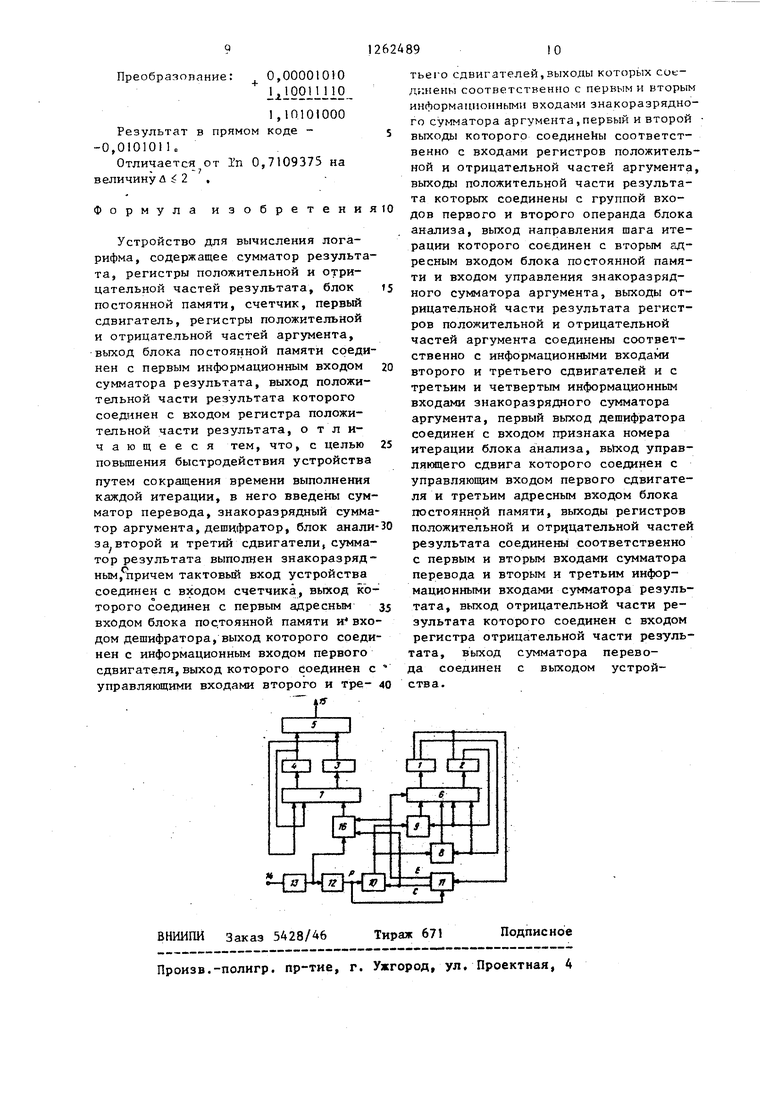

На чертеже изображена структурная схема устройства для вычисления логарифма.

Устройство содержит регистры положительной 1 и отрицательной 2 частей аргумента, положительной 3 и отрицательной 4 частей результата, сумматор 5 перевода, знакоразрядные сумматоры аргумента 6 и результата 7, второй 8, третий 9 и первый 10 сдвигатели, блок 11 анализа, дешифратор 12,счетчик 13, тактовый вход 14 устройства, выход 15 устройства, бтюк 16 постоянной памяти.

В предлагаемом устройстве процесс вычисления логарифма основывается на следующих равенствах. Аргумент ,5; 1 представляется в виде

(1)

где ,1|; Epf:{-l, О, 1) номер итерации; К - разрядность аргумента.

Тогда значение результата представится в виде

- (Р-с)

X -irinLKEp21 .(2)

На основании (1) и (2) процесс вычисления логарифма представится следующими рекуррентными выражениям Хр., 2(Хр+Ер Хр); (3) y.,5f,-ln(UR/2- - ), (40

fwi. ,К; Ept{-l, О, т}; С€(0, .

где Р

Начальное условие: .

Результат: У 1пХ; . .

Переменные Е и С на каждой р-й итерации определяются по значениям старших разрядов Хр таким образом, чтобы первый после запятой разряд Хр в результате выполнения (З) принимал нулевое значение. При этом при заданных начальных условиях переменная X будет стремиться к значению единица с точностью до К-й двоичной цифры, а переменная Хр - к значению In X.

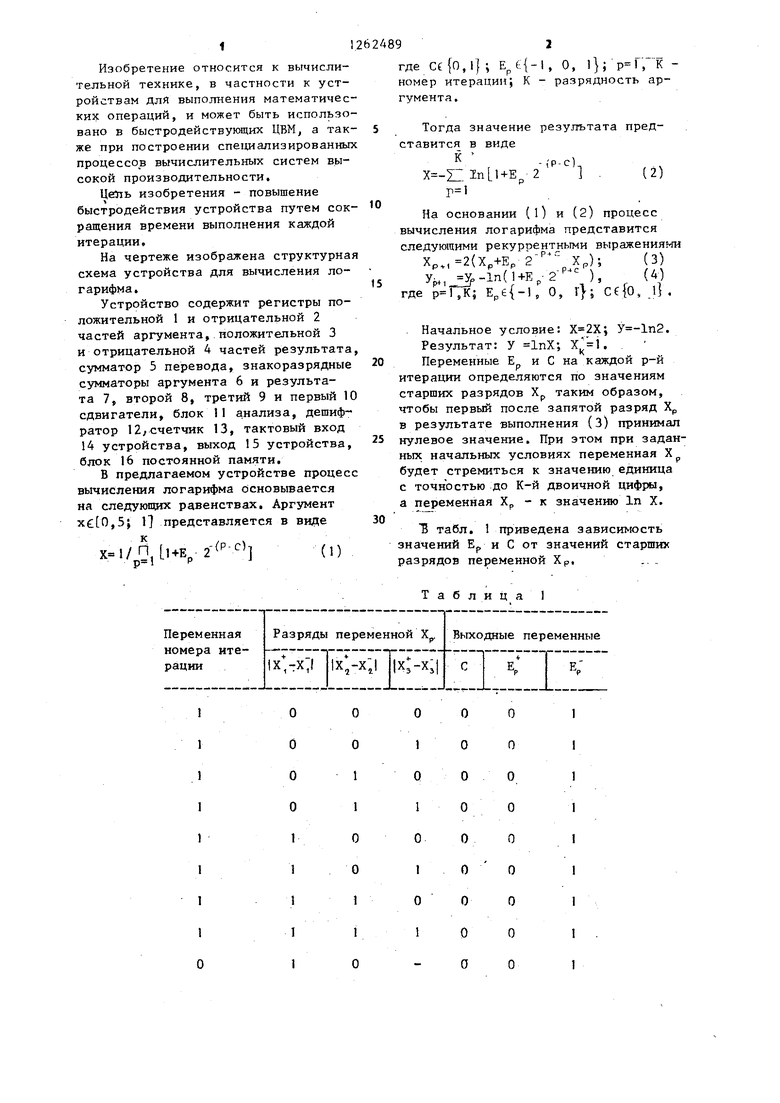

В табл. 1 приведена зависимость значений Ер и С от значений старших разрядов переменной Хр,

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1985 |

|

SU1254477A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1084785A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1103225A1 |

| Специализированный процессор для вычисления элементарных функций | 1984 |

|

SU1265764A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Специализированный процессор | 1977 |

|

SU734705A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам для выполнения математических операций в ЦВМ. Цель изобретения - повьшение.быстродействия устройства за счет сокращения времени выполнения каждой итерации. В состав устройства входят регистры положительной и отрицательной частей аргумента, регистры положительной и отрицательной частей результата, сумматор перевода, сумматор ре,зультата, знакоразрядный сумматор аргумента, три сдвигателя, блок анализа, дешифратор, счетчик и блок постоянной памяти. Введение сумматора перевода, знакоразрядного сумматора аргумента, дешифратора, блока анализа, двух сдвигателей и- новых с S связей позволяет повысить быстродействие устройства за счет сокраще(Л ния времени выполнения каждой итерации в 1,5 раза. I ил.

1 1 1 1 1 1 1 1 О

О О

о о 1 1 } I 1

о о 1 1

о о 1 1 о Обозначения, принятые в табл. 1: Ер, Ер - двоичные переменные для управления направлением шага; -Е;-Е;; Е;, Ер€{0, 1};Че{0. 1} переменная номера итерации при P-l.M-O, при Р-ЗТТС. Прочерками в табл. 1 обозначены случаи, когда значение переменной не влияет на выходные сигналы.

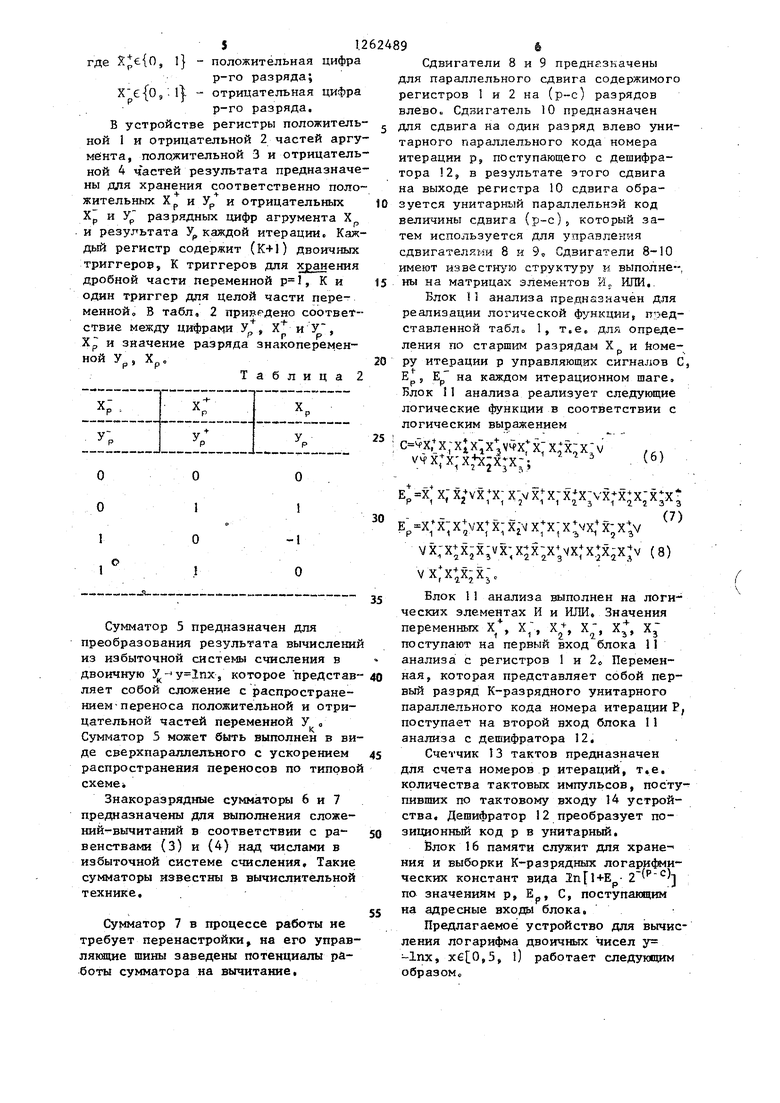

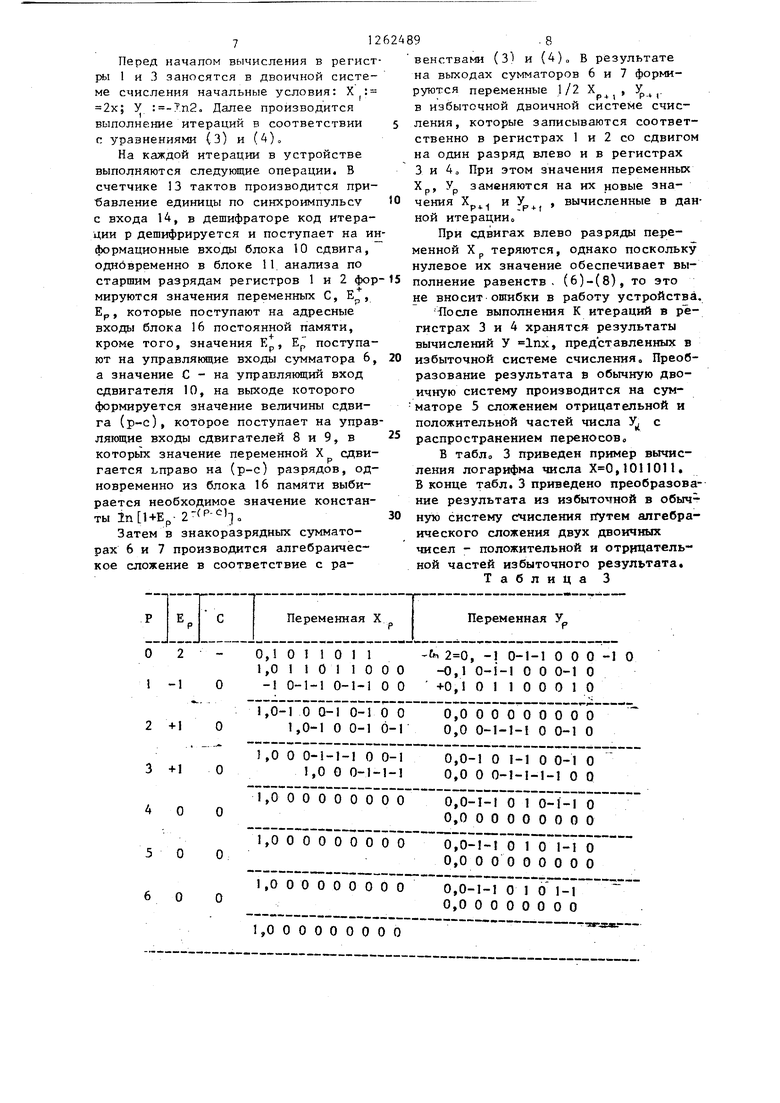

Продолжение табл.1 В предлагаемом устройстве на каждом шаге итераций переменных и Ур хранятся в избыточной двоичной системе счисления с основанием 2 и циф рами -1,0, 1; любое К-разрядаое . число в этой системе счисления представляется в ви,де К (Х;-Х-) 2- (5) 51.2 где Хре{П, 1} - положительная цифра р-го разряда; Xelo/.l. - отрицательная цифра р-го разряда. В устройстве регистры положительной 1 и отрицательной 2 частей аргумбнта, положительной 3 и отрицательной 4 частей результата предназначены для хранения соответственно положительных Хр и Ур и отрицательных Хр и Ур разрядных цифр агрумента Х и результата У каждой итерации. Каждый регистр содержит (К-И) двоичных триггеров К триггеров для хранения дробной части переменной , К и один триггер для целой части переменной,, В табл, 2 приведено соответствие между цифрами У, Х и У, Хр и значение разряда знакопеременСумматор 5 предназначен для преобразования результата вычислен из избыточной системы счисления в двоичную 3Jj., которое представ ляет собой сложение с распространением -переноса положительной и отрицательной частей переменной У о Сумматор 5 может быть выполнен в ви де сверхпараллельного с ускорением распространения переносов по типово схеме Знакоразрядные сумматоры 6 и 7 предназначены для выполнения сложений-вычитаний в соответствии с равенствами (З) и (4) над числами в избыточной системе счисления. Такие сумматоры известны в вычислительной технике, . Сумматор 7 в процессе работы не требует перенастройки, на его управ лянвдие шины заведены потенциалы работы сумматора на вычитание. 9§ Сдвигатели 8 и 9 преднгзкачены для параллельного сдвига содержимого регистров 1 и 2 на (р-с) разрядов влевОо Сдзигатель 10 предназначен ддя сдвига на один разряд влево унитарного параллельного кода номера итерации р, поступающего с дешифратора 2, в результате этого сдвига на выходе регистра 10 сдвига образуется унитарный параллельнэй код величины сдвига (р-с), который затем используется для управления сдвигателями 8 и 9, Сдвигатели 8-10 имеют известщю структуру и выполне-, ны на матрицах элементов й, ИЛИ,. Блок 1 анализа предназначен для реализации логической функции, представленной табЛо 1, т,е. для определения по старшим разрядам Хр и йомеру итерации р управляющих сигналов С, Ер, Ер на каждом итерационном шаге. Блок 11 анализа реализует следующие логические функции в соответствии с логическим выражением (;х;х:х;хХЯ;х;х-х;у . V4x;x;x,-x;x-; , x;x;vx;x; х х;х;х хлх;х;х;х;Хз Ep x;x;x;vx;x;x,vx;x;xXx-x;v vx;x;x-x;vx;x x;x;vx;x.;x2x;v (в) vx:x;x-x, Блок 11 анализа выполнен на логических элементах И и ИЛИ, Значения переменных хД х;, , Х, х; поступают на первый вход блока 11 анализа с регистров 1 и 2с, Переменная, которая представляет собой первый разряд К-разрядного унитарного параллельного кода номера итерации Р, поступает на второй вход блока I1 анализа с дешифратора 12, . Счетчик 13 тактов предназначен для счета номеров р итераций, , количества тактовых импульсов, поступивших по тактовому входу 14 устройства. Дешифратор 12 преобразует позиционный код р в унитарный, 1Влок 16 памяти служит для хранения и выборки К-разрядных логарифмических констант вида Infl+Ep- 2 по значениям р, Е, С, поступающим на адресные входы блока. Предлагаемое устройство для вычисления логарифма двоичных чисел у -1пх, ,5, }) работает следующим образом. 71 Перед началом вычисления в регист ры 1 и 3 заносятся в двоичной системе счисления начальные условия: X : 2х; У . Далее производится вылолнение итераций в соответствии с уравнениями (З) и (4) На каждой итерации в устройстве выполняются следующие операции. В счетчике 13 тактов производится прибавление единицы по синхроимпульсу с входа 14, в дешифраторе код итерации р дешифрируется и поступает на ин формационные входы блока 10 сдвига, однбвременно в блоке 11 анализа по старшим разрядам регистров 1 и 2 фор мируются значения переменных С, Е, Ер, которые поступают на адресные входы блока 16 постоянной памяти, кроме того, значения Ер, Ер поступают на управляющие входы сумматора 6, а значение С - на управляющий вход сдвигателя 10, на выхода которого формируется значение величины сдвига (р-с), которое поступает на управ ляющие входы сдвигателей 8 и 9, в которых значение переменной X сдвигается ъправо на (р-с) разрядов, одновременно из блока 16 памяти выбирается необходимое значение константы in H-Ep-2-fP- o Затем в знакоразрядных сумматорах 6 и 7 производится алгебраическое сложение в соответствие с ра1,0-1 О 0-1 0-1 О О 1,0-1 О 0-1 6-1

1,0 О 0-1-1-1 О 0-1 1,0 о 0-1-1-1

1,0 00000000

1,0 00000000

1,000000000

1,0 00000000

О,О 00000000 0,0 0-1-1-1 О 0-1 О

0,0-1 о 1-1 о 0-1 о 0,0 о 0-1-1-1-1 о о

0,0-1-1 о 1 0-1-1 о 0,0 о о о о о о о о

0, о 1 о 0,0 о 00 00000

0,0-1-1 о 1 о 1-1 0,0 0000000 9.8 венствами (З и (4) о В результате на выходах сумматоров 6 и 7 формируются переменные 1/2 X , . в избыточной двоичной системе счисления, которые записываются соответственно в регистрах 1 и 2 со сдвигом на один разряд влево и в регистрах 3 и 4о При этом значения переменных Хр, Ур заменяются на их новые эначения X р+ вычисленные в данной итерации При сдвигах влево разряды переменной Хр теряются, однако поскольку нулевое их значение обеспечивает выполнение равенств. (6)-(8), то это не вносит оптбки в работу устройства. ilocne выполнения К итераций в рЪгистрах 3 и 4 хранятся результаты вычислений У 1пх, представленных в избыточной системе счисления Преобразование результата в обычную двоичную систему производится на сумматоре 5 сложением отрицательной и положительной частей числа У с распространением переносов, В табла 3 приведен пример вычисления логарифма числа ,. В конце табл. 3 приведено преобразование результата из избыточной в обычную систему счисления йутем алгебраического сложения двух двоичных чисел - положительной и отрицательной частей избыточного результата. Таблица 3

| Байков В, Д | |||

| Смолов В | |||

| Б | |||

| Аппаратная реализация элементарных функций в ЦВМ | |||

| Л., ЛГУ, 1975, с | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1986-10-07—Публикация

1984-10-29—Подача