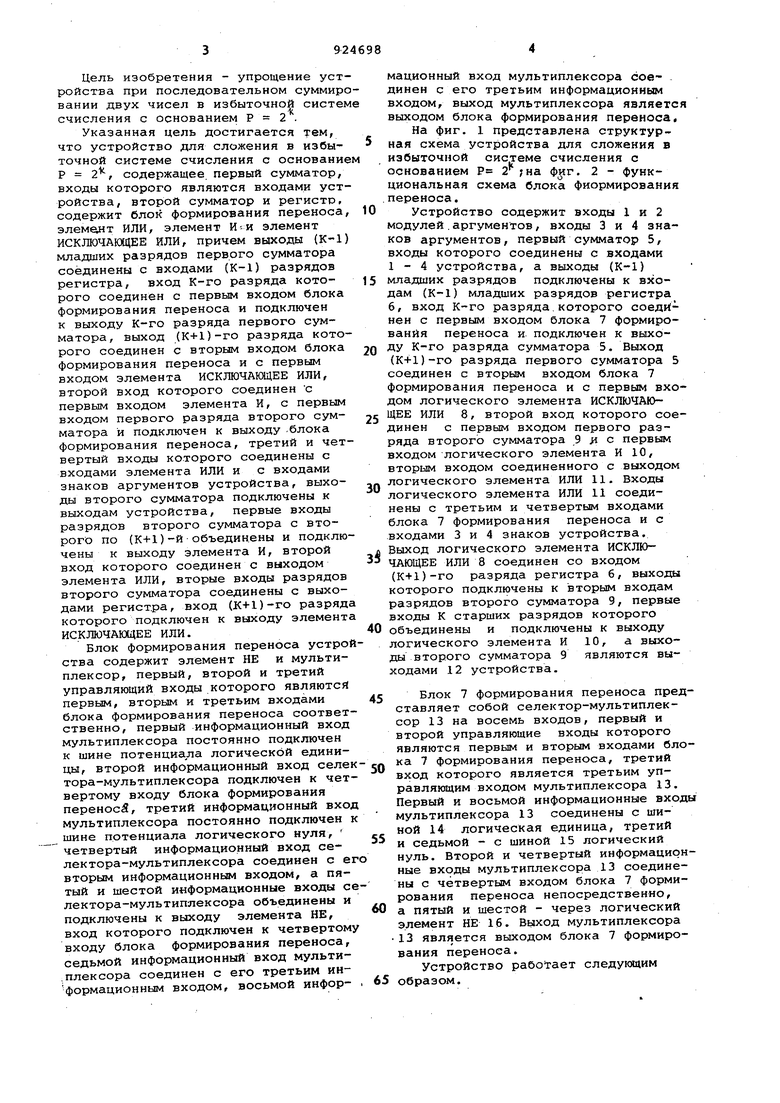

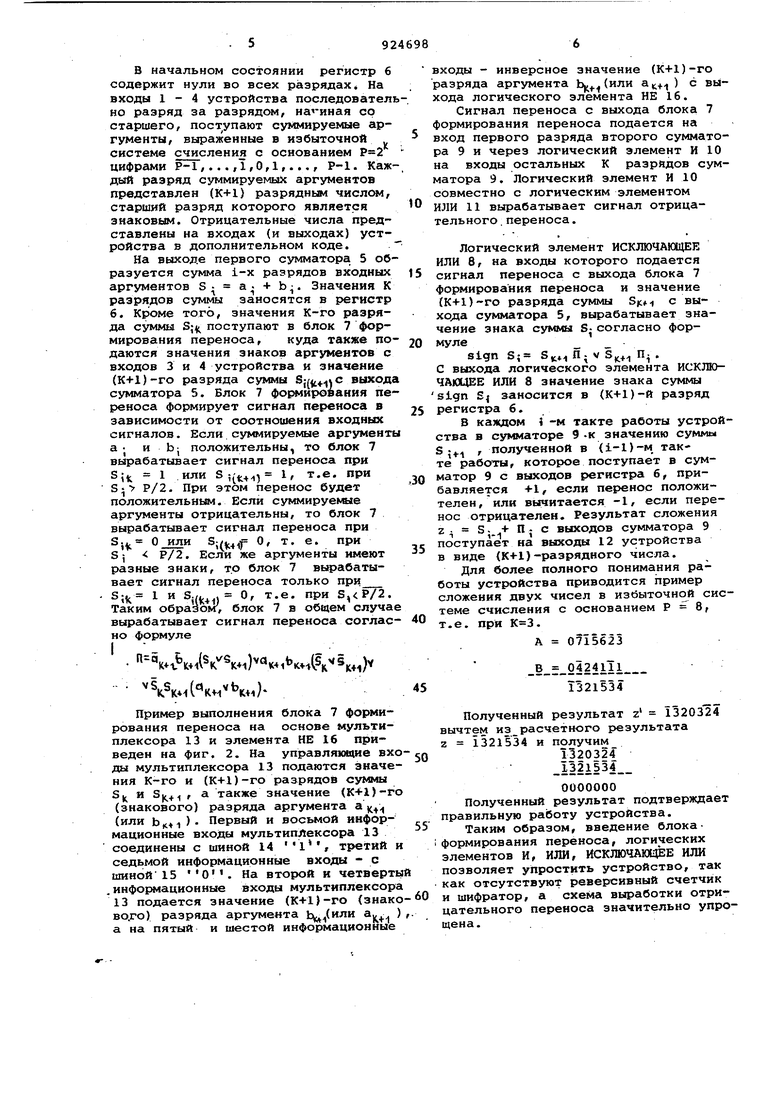

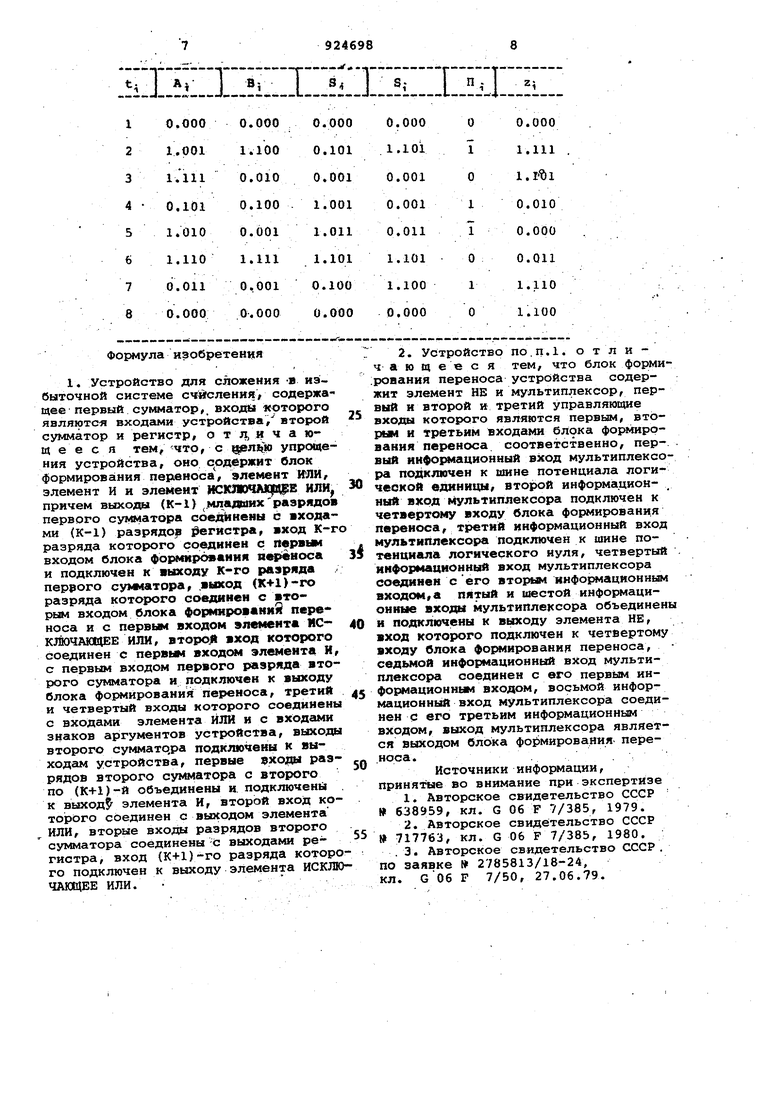

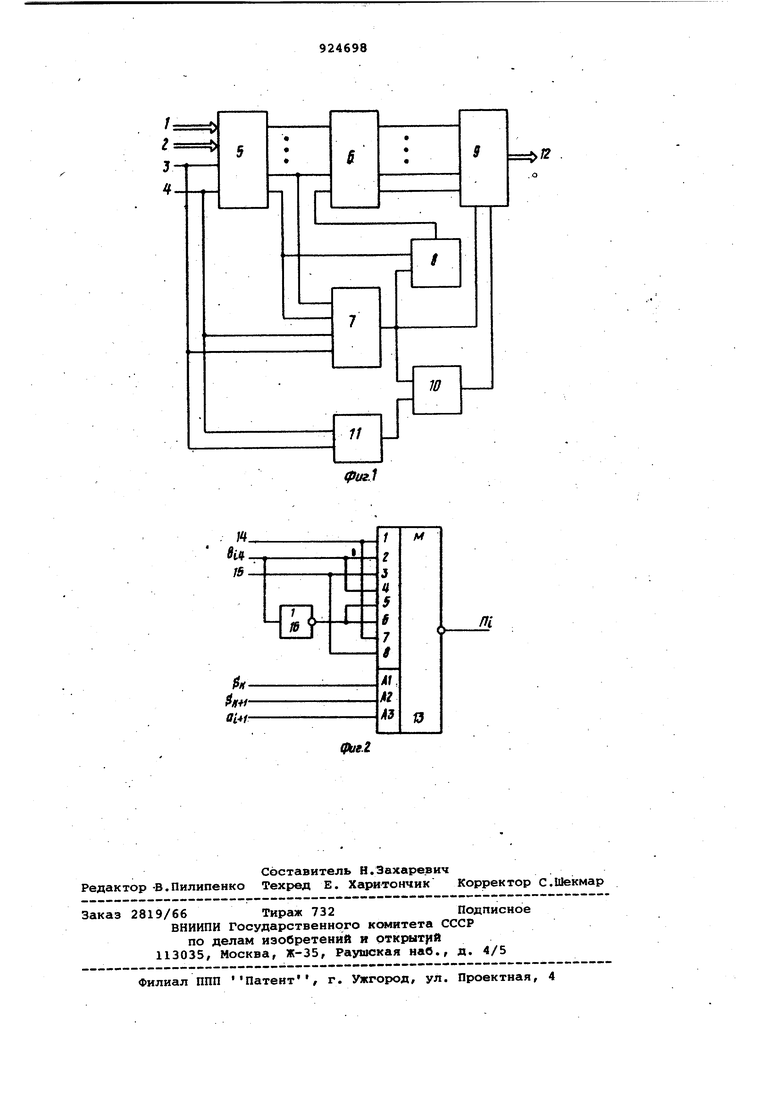

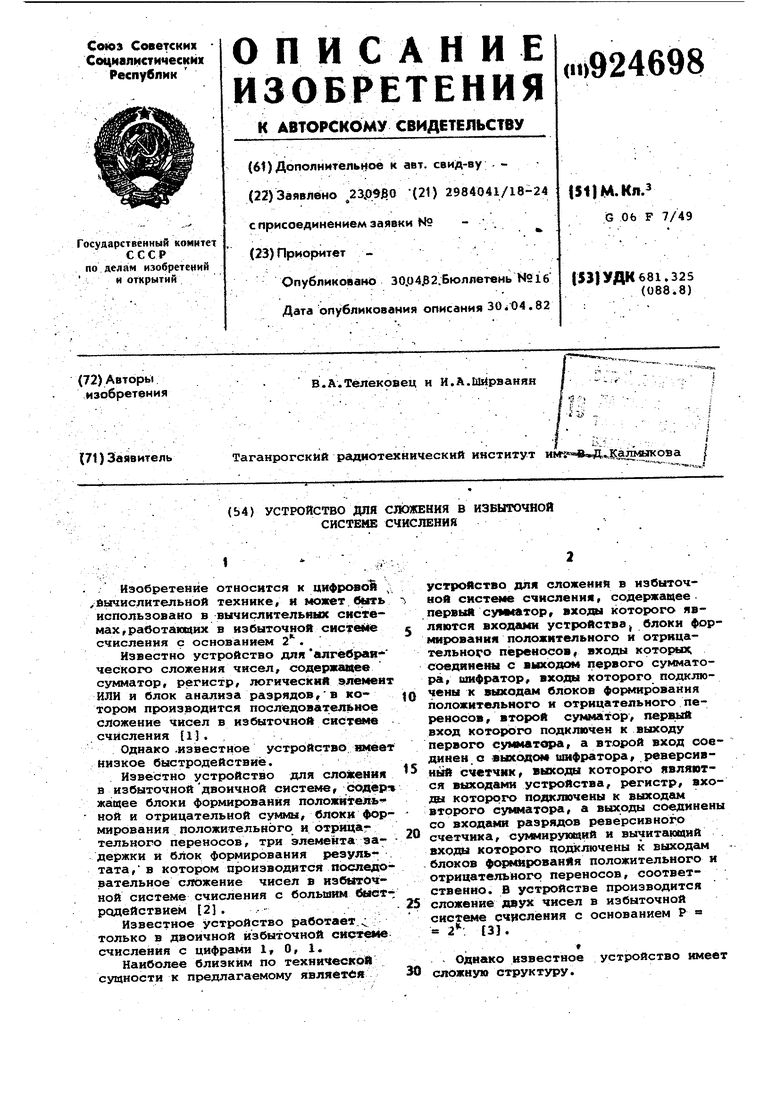

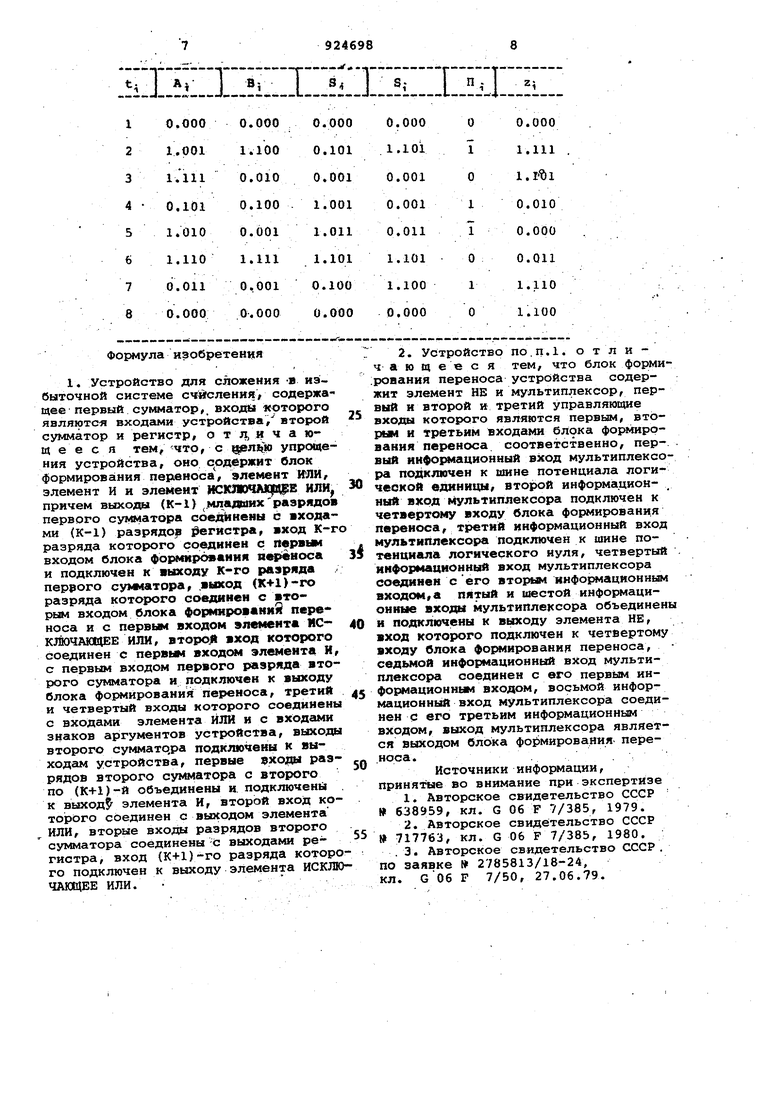

Цель изобретения - упрощение уст ройства при последовательном суммир вании двух чисел в избыточной систе счисления с основанием Р 2 . Указанная цель достигается тем, что устройство для сложения в извыточной системе счисления с основани Р 2, содержащее первый сумматор, входы которого являются входами уст ройства, второй сумматор и регистр, содержит блок формирования переноса элем€ нт ИЛИ, элемент элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем ВЫХОДЫ (K-l младших разрядов первого сумматора соединены с входами (К-1) разрядов регистра, вход К-го разряда которого соединен с первым входом блока формирования переноса и подключен к выходу К-го разряда первого сумматора, выход {К+1)-го разряда которого соединен с вторым входом блока формирования переноса и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с первым входом элемента И, с первым входом первого разряда второго сумматора и подключен к выходу .блока формирования переноса, третий и чет вертый входы которого соединены с входами элемента ИЛИ и с входами знаков аргументов устройства, выходы второго сумматора подключены к выходам устройства, первые входы разрядов второго сумматора с второго по (К+1)-и объединены и подключены к выходу элемента И, второй вход которого соединен с выходом элемента ИЛИ, вторые входы разрядов второго сумматора соединены с выходами регистра, вход (К+1)-го разряда которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Блок формирования переноса устрой ства содержит элемент НЕ и мультиплексор, первый, второй и третий управляющий входы которого являются первым, вторым и третьим входами блока формирования переноса соответственно, первый информационный вход мультиплексора постоянно подключен к шине потенциала логической единицы, второй информационный вход селек тора-мультиплексора подключен к четвертому входу блока формирования переноси, третий информационный вход мультиплексора постоянно подключен к шине потенциала логического нуля, четвертый информационный вход селектора-мультиплексора соединен с ег вторым информационным входом, а пятый и шестой информационные входы се лектора-мультиплексора объединены и подключены к выходу элемента НЕ, вход которого подключен к четвертому входу блока формирования переноса, седьмой информационный вход мультиплексора соединен с его третьим информационным входом, восьмой информационный вход мультиплексора соединен с его третьим информационным входом, выход мультиплексора является выходом блока формирования переноса. На фиг. 1 представлена структурная схема устройства для сложения в избыточной системе счисления с основанием Р ;на ф,г. 2 - функциональная схема блока фиормирования переноса. Устройство содержит входы 1 и 2 модулей.аргументов, входы 3 и 4 знаков аргументов, первый сумматор 5, входы которого соединены с входами 1-4 устройства, а выходы (К-1) младших разрядов подключены к входам (К-1) младших разрядов регистра 6, вход К-го разряда,которого соединен с первым входом блока 7 формирования переноса и подключен к выходу К-го разряда сумматора 5. Выход (К+1)-го разряда первого сумматора 5 соединен с вторым входог блока 7 формирования переноса и с первым входом логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, второй вход которого соединен с первым входом первого разряда второго сумматора 9 i с первым входом логического элемента И 10, вторым входом соединенного с выходом логического элемента ИЛИ 11. Входы логического элемента ИЛИ 11 соединены с третьим и четвертым входами блока 7 формирования переноса и с входами 3 и 4 знаков устройства. Выход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 соединен со входом (К+1)-го разряда регистра б, выходы которого подключены к вторым входам разрядов второго сумматора 9, первые входы К старших разрядов которого объединены и подключены к выходу логического элемента И 10, а выхоы второго сумматора 9 являются выодами 12 устройства. Блок 7 формирования переноса представляет собой селектор-мультиплексор 13 на восемь входов, первый и второй управляющие входы которого являются первым и вторым входами блока 7 формирования переноса, третий вход которого является третьим управляющим входом мультиплексора 13. Первый и восьмой информационные входы мультиплексора 13 соединены с шиной 14 логическая единица, третий и седьмой - с шиной 15 логический нуль. Второй и четвертый информационные входы мультиплексора 13 соединены с четвертым входом блока 7 формирования переноса непосредственно, а пятый и шестой - через логический элемент НЕ 16. Выход мультиплексора 13 является выходом блока 7 формирования переноса. Устройство работает следующим образом. В начальном состоянии регистр 6 содержит нули во всех разрядах« На входы 1-4 устройства последовател но разряд за разрядом, на иная со старшего, пост упают суммируемые аргументы, выраженные в избыточной системе счисления с основанием цифрг1ми Р-1,... ,1 0,1,..., Р-1. Каж дый разряд суммируемых аргументов представлен (К+1) разрядным , старший разряд которого является знаковым. Отрицательные числа представлены на входах (и выходах) устройства в дополнительном коде. На выходе первого сумматора 5 об разуется сумма i-x разрядов входных аргументов S- а + Ь. Значения К разрядов суммы заносятся в регистр 6. Кроме того, значения К-го разряда суммы S;4i поступают в блок 7 формирования переноса, куда также по даются значения знаков аргументов с входов 3 и 4 устройства и значение (К+1)-го разряда суммы выхода сумматора 5. Блок 7 формирования переноса формирует сигнал переноса в зависимости от соотношения входных сигналов. Если суммируемые аргументы а; и Ь; положительны, то блок 7 вырабатывает сигнал переноса при S 1 или S ) т.е. при S- Р/2. При этом перенос будет положительным. Если суммируеквде аргументы отрица тельны, то блок 7 вырабатывает сигнал переноса при Sj О или Sj/Vi+iT Р Sj Р/2. Если же аргументы имеют разные знаки, то блок 7 вырабатывает сигнал переноса только при S; 1 и 8ц|,, О, т.е. при S,P/2. Таким обрайом, блок 7 в общем случа вырабатывает сигнал переноса соглас но формуле () K4ibK4VS|C4lh () Пример выполнения блока 7 формирования переноса на основе мультиплексора 13 и элемента НЕ 16 приведен на фиг. 2. На управляющие вхо ды мультиплексора 13 подаются значе ния К-го и (К+1)-го разрядов суммы Зц и SY , а также значение (К+1)-г (знакового) разряда аргумента а );, (или ). Первый и ВОСЬМОЙ информационные входы мультиплексора 13 соединены с шиной 14 , третий седьмой информационные входы - с шиной15 О. На второй и четверты .информационные входы мультиплексор 13 подается значение (К+1)-го (знак B0.ro) разряда аргумента ь(или а| а на пятый и шестой информационные входы - инверсное значение (К+1)-го разряда аргумента ty (или а ) с выхода логического злемента НЕ 16. Сигнал переноса с выхода блока 7 формирования переноса подается на вход первого разряда второго сумматора 9 и через логический элемент И 10 на входы остальных К разрядов сумматора 9. Логический элемент И 10 совместно с логическим элементом ИЛИ 11 вырабатывает сигнал отрицательного ,переноса. Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, на входы которого подается сигнал переноса с выхода блока 7 формирования переноса и значение (К+1)-го разряда суммы Sjcf с выхода сумматора 5, вырабатывает значение знака суммы S- согласно формуле . sign S; Й-V П . С выхода логического элемента ИСКЛЮЧАКХДВЕ ИЛИ 8 значение знака суммы sign S| заносится в (К+1)-и разряд регистра 6. В каждом I -м такте работы устройства в сумматоре 9 -к значению суммы , полученной в {1-1)-м такте работы, которое поступает в сумматор 9 с выходов регистра б, прибавляется +1, если перенос положителен, или вычитается -1, если перенос отрицателен. Результат сложения Z . S.. + П ; с выходов сумматора 9 поступает на выходы 12 устройства в виде К+1)-разрядного числа. Для более полного понимания работы устройства приводится пример сложения двух чисел в избыточной системе счисления с основанием Р 8, т.е. при . А 0715623 В 0424111, 1321534 Полученный результат z 1320324 вычтем из расчетного результата z 1321534 и получим 1320324 1321534 0000000 Полученный результат подтверждает правильную работу устройства. Таким образом, введение блокаформирования переноса, логических элементов И, ИЛИ, ИСКЛЮЧАЮЦЕЕ ИЛИ позволяет упростить устройство, так как отсутствуют реверсивный счетчик и шифратор, а схема выработки отрицательного переноса значительно упрощена. .

:i.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

| Многовходовой знакоразрядный сумматор | 1982 |

|

SU1027716A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Устройство для извлечения квадратного корня | 1986 |

|

SU1381497A1 |

| Устройство для вычисления ядер Винера нелинейных объектов | 1984 |

|

SU1196896A1 |

| Цифровой фильтр | 1987 |

|

SU1418756A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| @ -Ичный сумматор | 1984 |

|

SU1273925A1 |

| Устройство для извлечения квадратного корня | 1988 |

|

SU1575177A1 |

Формула изобретения 1. Устройство для сложения -я нэбыточной системе счисления/ содержащее первый сумматор,, входы которого являются входами устройства, второй сумматор и регистр, о т л, и ч а ющ ее с я тем, что, с упрощения устройства, оно содержит блок формирования переноса, элемент ИЛИ, элемент И и элемент ИСКЛЮЧА ЦЦРВ ИЛИ, причем выходы (К-1 .младшихразрядов первого сум 4атора сое {йнены с аходами (К-1) разрядов регясгрл, вход К-г разряда которого соединен с первый входом блока фосмирования жфеноса и подключен к выходу К-го разряда первого сумматора, яыход (K-t-l)-ro разряда которого соединен с вторым входом блока формиромниЯ переноса и с первым входом элемента ИСКШЧАЮЦЕЕ или, BTOpOjtt ВХОД КОТОРОГО соединен с первьм входсж элемента И, с первым входом первого разряда второго сукматора и подключен к выходу блока формирования переноса, третий и четвертый входы которого соединены с входами элемента ИЛИ и с входгши знаков аргументов устройства, выходы второго суммато.ра подключены к выходам устройства, первые входа разрядов второго сумматора с второго по (К+1)-й объединены и подключены к выход элемента И, второй вход которого соединен с выходом элемента ИЛИ, вторые входы разрядов второго сумматора соединены -С выходами регистра, вход (К+1)-го разряда которо го подключен к выходу элемента ИСКЛЮ ЧАЮЩЕЕ ИЛИ. 2. Устройство по.п.1. отличающееся тем, что блок форми:рования переноса устройства содержит элемент НЕ и мультиплексор, первый и второй и третий управляющие входы которого являются первым, вто1ЯМ н Третьим входами блока фо(тррвання переноса соответственно, первый инфосялацнонный вход мультиплексора подключен к шине потенциала логической единицы, второй информационный вход мультиплексора подключен к четвертому входу блока формирования переноса, третий информационный вход мультиплексора подключен к шине потенциала логического нуля, четвертый . информационный вход мультиплексора соединен сего BTOF« t информационным входом,а пятый и шестой информационные входы мультиплексора объединены и подключены к вьосоду элемента НЕ, вход которого подключен к четвертому входу блока фО1М4Ирования переноса, седьмой информацнонный вход мультиплексора соединен с его первьм информационньм входом, восьмой информационный вход мультиплексора соединен С его третьим информационным входом, выход мультиплексора является выходом блОка фО)мирования пере.носа.. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 638959, кл. G 06 Р 7/385, 1979. 2.Авторское свидетельство СССР 717763, кл. G 06 Р 7/385, 1980. . 3. Авторское свидетельство СССР . по заявке 2785813/18-24, кл. сОб F 7/50, 27.06.79.

12

Авторы

Даты

1982-04-30—Публикация

1980-09-23—Подача