Изобретение относится к вычислительной технике и может быть использовано при построении устройств па- нараллельного суммирования чисел, представленных в избыточных системах счисления.

Цель изобретения - повышение быстродействия .

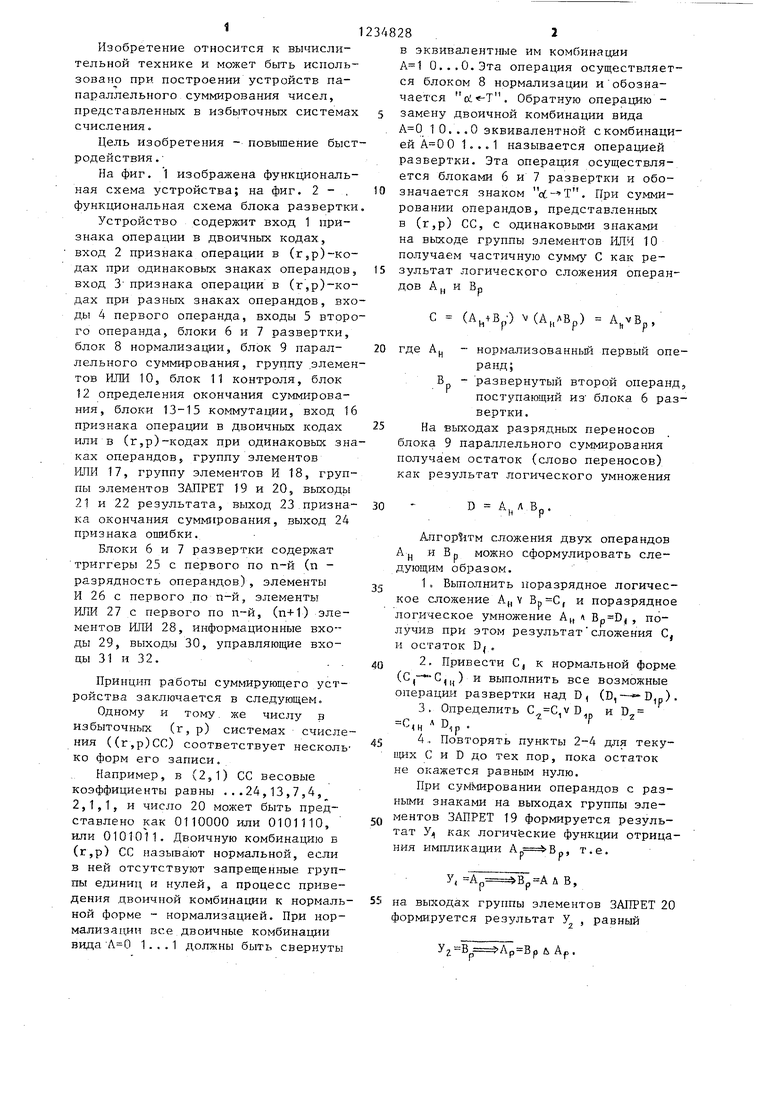

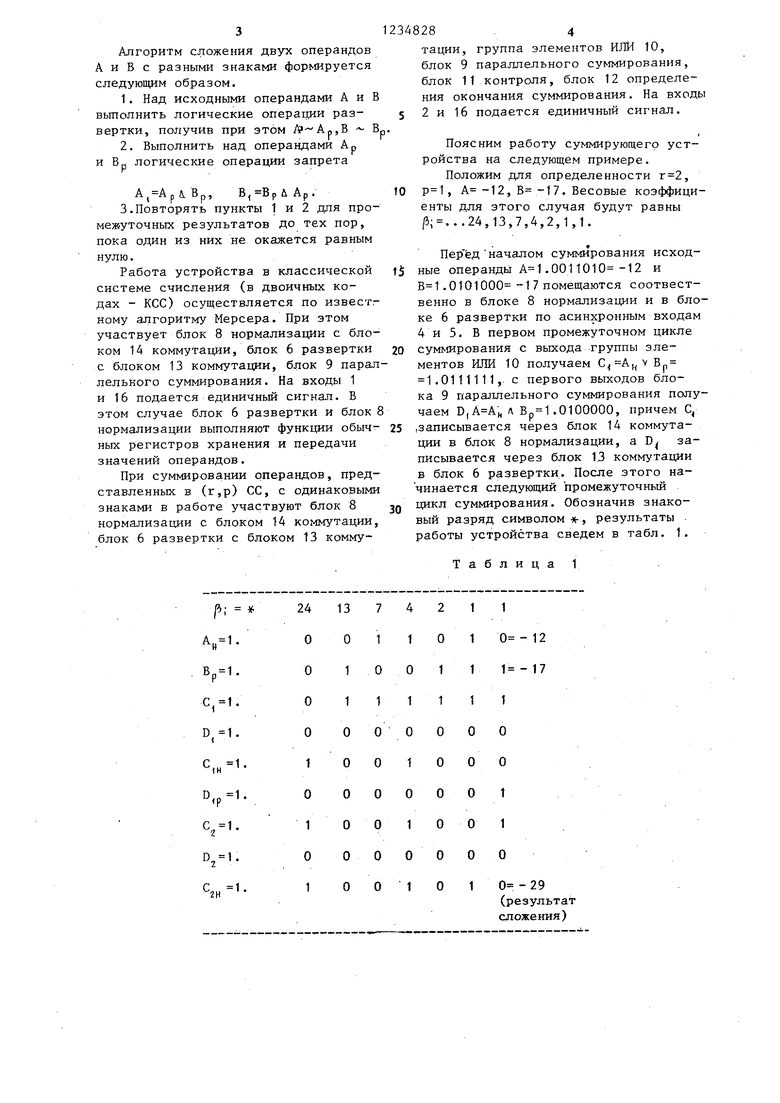

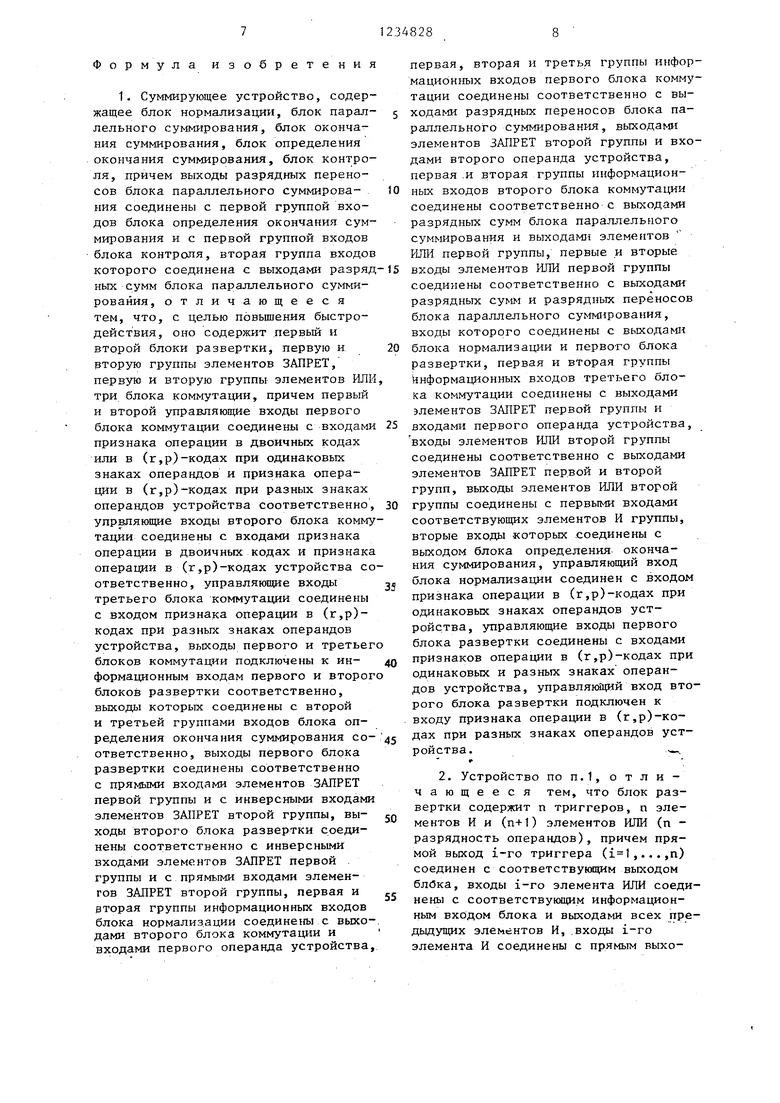

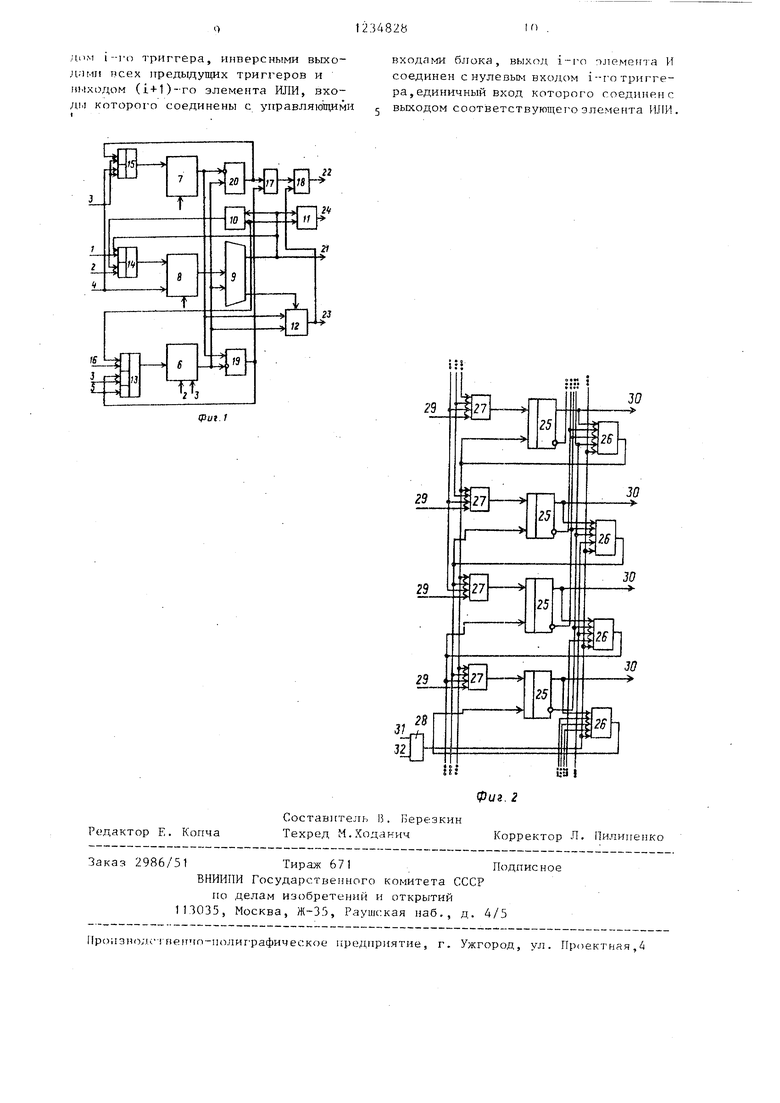

Иа фиг. 1 изображена функциональная схема устройства; на фиг. 2 - , функциональная схема блока развертки

Устройство содержит вход 1 признака операции в двоичных кодах, вход 2 признака операции в (гjp)-кодах при одинаковых знаках операндов, вход 3 признака оператдии в (г,р)-ко- дах при разных знаках операндов, входы 4 первого операнда, входы 5 второго операнда, блоки 6 и 7 развертки, блок 8 нормализации, блок 9 параллельного суммирования, группу элементов ИЛИ 10, блок 11 контроля, блок 12 определения окончания суммирования, блоки 13-15 коммутации, вход 16 признака операции в двоичньпс кодах или в (г,р)-кодах цри одинаковых знаках операндов, группу элементов ИЛИ 17, группу элементов И 18, группы элементов ЗАПРЕТ 19 и 20, выходы 21 и 22 результата, выход 23,признака окончания суммирования, выход 24 признака ошибки.

Блоки 6 и 7 развертки содержат триггеры 25 с первого по п-й (п - разрядность операндов), элементы И 26 с первого по п-й, элементы ИЛИ 27 с первого по п-й, (п+1) элементов ИЛИ 28, информационные входы 29, выходы 30, управляющие вхо- цы 31 и 32.

Принцип работы суммирующего устройства заключается в следующем.

Одному и тому. же числу в избыточных (г, р) системах счисления ((г,р)СС) соответствует несколько форм его записи.

Например, в (2,1) СС весовые коэффициенты равны ...24,13,7,4, 2,1,1, и число 20 может быть представлено как 0110000 или 0101110, или 0101011. Двоичную комбинацию в (г,р) СС называют нормальной, если 3 ней отсутствуют запрещенные группы единиц и нулей, а процесс приведения двоичной комбинации к нормальной форме - нормализацией. При нормализации все двоичные комбинации видаЛ 0 1... 1 должны быть свернуты

348282

в эквивалентные им комбинации О...О.Эта операция осуществляется блоком 8 нормализации и обозначается о.-Т. Обратную операцию 5 замену двоичной комбинации вида , 10...О эквивалентной с комбинацией О 1...1 называется операцией развертки. Эта операция осуществляется блоками 6 и 7 развертки и обо10 значается знаком . При суммировании операндов, представленных в (г,р) СС, с одинаковыми знаками на выходе группы элементов 11ПИ 10 получаем частичную сумму С как ре15 зультат логического сложения операндов А, и Вр

С (А,+ ) ЧА.лВр) ,

20 где А - нормализованньй первый операнд;

В - развернутый второй операнд, поступающий из блока 6 развертки.

25 На выходах разрядш тх переносов блока 9 параллельного суммирования получаем остаток (слово переносов) как результат логического умножения

30

D .

AnropliTM сложения двух операндов А j и Вр можно сформулировать следующим образом.

1 , Выполнить Поразрядное логическое сложение А„V , и поразрядное логическое умножение А А Ър- О , получив при этом результат сложения С, и остаток D.

2. Привести С, к нормальной форме (С,,|) и выполнить все возможные операции развертки над D, (D, ,p).

3. Определить ,v D и 0 С,н D,,p .

4., Повторять пункты 2-4 для текущих С и D до тех пор, пока остаток не окажется равным нулю.

При сумйировании операндов с разными знаками на выходах группы элементов ЗАПРЕТ 19 формируется результат УН как логические функции отрицания импликации А.

Вр, т.е.

у л

J( я.

. В,

на выходах группы элементов ЗАПРЕТ 20 формн:руется результат У , равный

& Ар,

Алгоритм сложения двух операндов А и В с разными знаками формируется следующим образом.

1.Над исходными операндами А и В вьтолнить логические операдаи развертки, получив при этом ,В В

2.Выполнить над операндами Ар и Вр логические операции запрета

А,, В,Вр&Ар.

3.Повторять пункты 1 и 2 для промежуточных результатов до тех пор, пока один из них не окажется равным нулю.

Работа устройства в классической системе счисления (в двоичных кодах - КСС) осуществляется по известг- ному алгоритму Мерсера. При этом участвует блок 8 нормализации с блоком 14 коммутации, блок 6 развертки с блоком 13 коммутации, блок 9 параллельного суммирования. На входы 1 и 16 подается единичньй сигнал. В

.0101000 -1 7 помещаются соотвест- венно в блоке 8 нормализации и в бло ке 6 развертки по асинхронным входам 4 и 5. В первом промежуточном цикле 20 суммирования с выхода группы элементов ИЛИ 10 получаем Вр 1.0111111, с первого выходов блока 9 параллельного суммирования полу чаем D, л .0100000, причем С,

этом случае блок 6 развертки и блок 8

нормализации выполняют функции обыч- 25.записывается через блок 14 коммутаньгх регистров хранения и передачиции в блок 8 нормализации, а D зазначений операндов.писывается через блок 1.3 коммутации

При суммировании операндов, представленных в (г,р) СС, с одинаковыми знаками в работе участвуют блок 8 нормализации с блоком 14 коммутации, блок 6 развертки с блоком 13 комму12348284

тации, группа элементов ИЛИ 10, блок 9 параллельного суммирования, блок 11 контроля, блок 12 определения окончания суммирования. На входы 5 2 и 16 подается единичный сигнал.

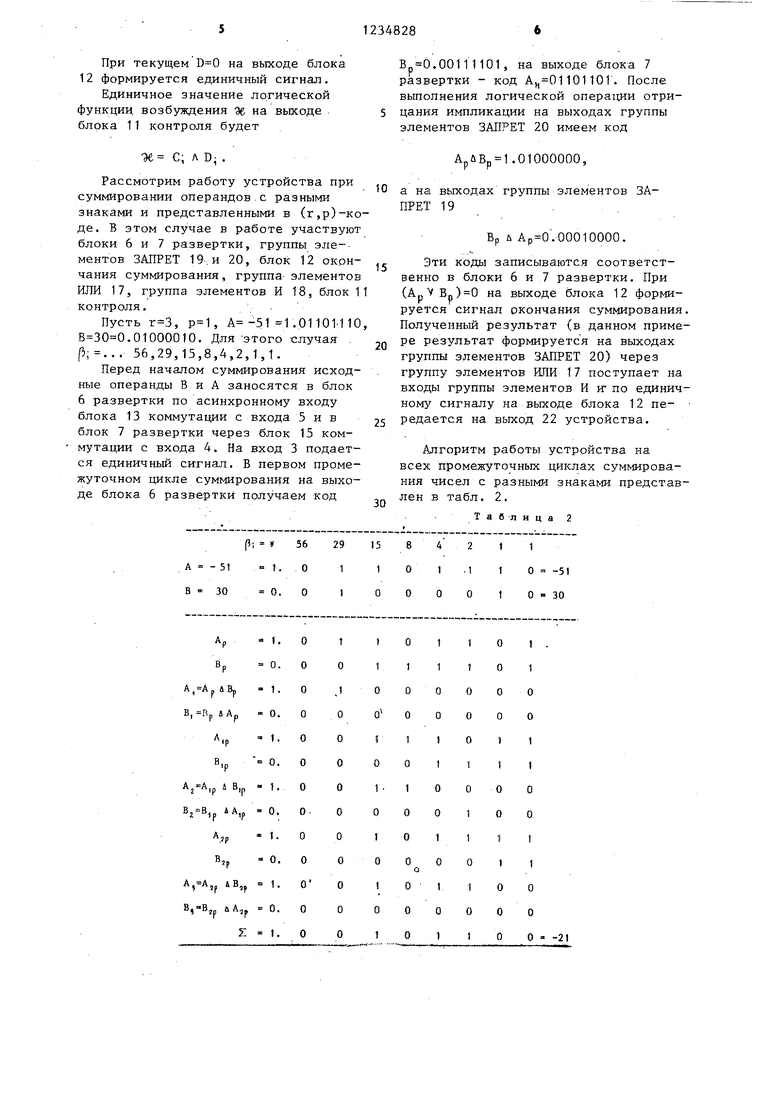

Поясним работу суммирующего устройства на следующем примере.

Положим для определенности , , , 7, Весовые коэффициенты для этого случая будут равны ;...24,13,7,4,2,1,1.

Пер ёд началом суммирования исход- ные операнды .0011010 -12 и

.0101000 -1 7 помещаются соотвест- венно в блоке 8 нормализации и в блоке 6 развертки по асинхронным входам 4 и 5. В первом промежуточном цикле суммирования с выхода группы элементов ИЛИ 10 получаем Вр 1.0111111, с первого выходов блока 9 параллельного суммирования получаем D, л .0100000, причем С,

.записывается через блок 14 коммутав блок 6 развертки. После этого начинается следующий промежуточный цикл суммирования. Обозначив знаковый разряд символом, результаты работы устройства сведем в табл. 1.

Таблица 1

(результат сложения)

5 12348286

При текущем на выходе блокаВр 0.00111101, на выходе блока 7

12 формируется единичный сигнал.развертки - код A 01101101. После

Единичное значение логическойвыполнения логической операхщи отрифункциц возбуждения Эб на выходеs цания импликации на выходах группы

блока 11 контроля будет .элементов ЗАЛРЕТ 20 имеем код

9е С;лВ-.АрйВр 1.01000000,

Рассмотрим работу устройства при,л „.

О а на выходах группы элементов ЗАсуммировании операндов.с разнымит ю

знаками и представленными в {г,р)-ко- .

де. В этом случае в работе участвуют. л -п nnninnnn

, -, Вр U Ап-и. UUU1 ииии.

блоки о и 7 развертки, группы зле--р н

ментов ЗАПРЕТ 19.и 20, блок 12 окон-,, Эти коды записываются соответстчания суммирования, группа- элементоввенно в блоки 6 и 7 развертки. При

ИЛИ 17, группа элементов И 18, блок 11(Ар V Вр)0 на выходе блока 12 формиконтроля. .руется сигнал окончания суммирования.

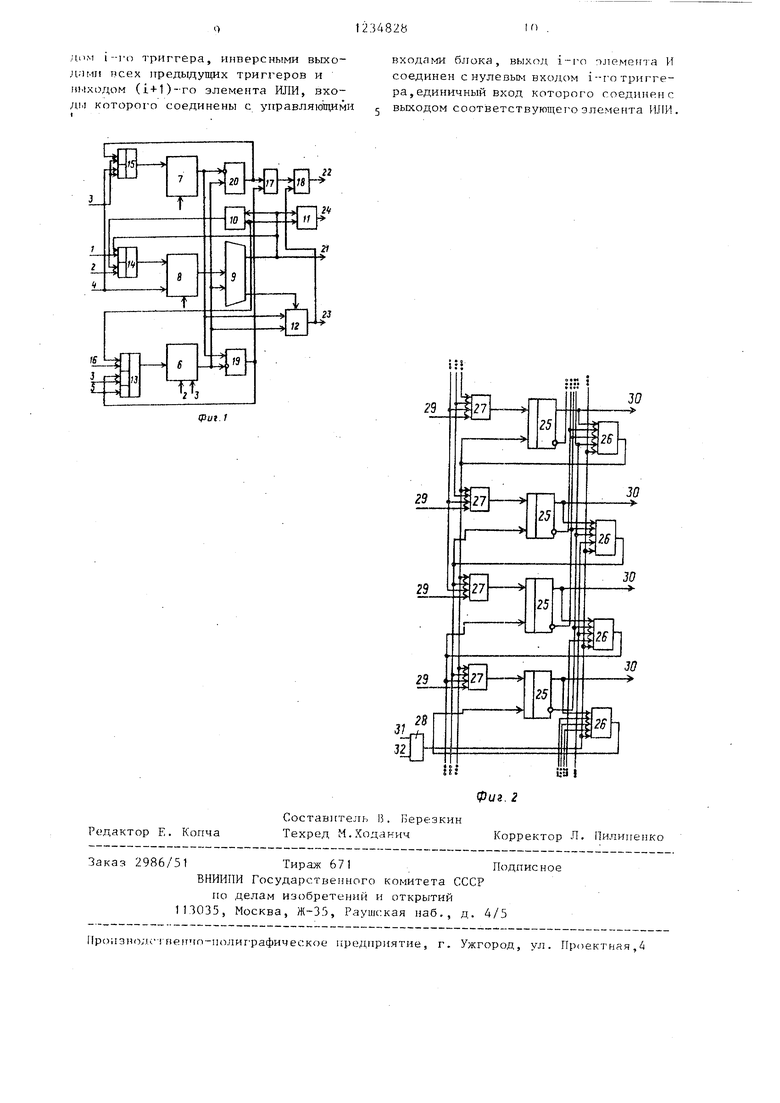

Пусть , , 1 .01101-110,Полученный результат (в данном приме5 30 0.01000010. Для этого случая ,. ре результат формируется на выходах

Р;... 56,29,15,8,4,2,1,1.группы элементов ЗАЛРЕТ 20) через

Перед началом суммирования исход-. группу элементов ИЛИ 17 поступает на

ные операнды В и А заносятся в блоквходы группы элементов И и- по единич6 развертки по асинхронному входуному сигналу на выходе блока 12 пеблока 13 коммутации с входа 5 и редается на выход 22 устройства,

блок 7 развертки через блок 15 ком-.

мутации с входа 4. На вход 3 подает-Алгоритм работы устройства на

ся единичный сигнал. Б первом проме-всех промежуточных циклах суммироважуточном суммирования на выхо-ния чисел с разными знаками представде блока 6 разве-рткй получаем кодлен в табл. 2.

Формула изобретения

1, Суммирующее устройство, содержащее блок нормализации, блок парал- лельного суммирования, блок окончания суммирования, блок определения окончания суммирования, блок контроля, причем выходы разрядных переносов блока параллельного суммирова- ния соединены с первой группой входов блока определения окончания суммирования и с первой группой входов блока контроля, вторая группа входов которого соединена с выходами разряд ных сумм блока параллельного суммирования, отличающееся тем, что, с целью повьшения быстродействия, оно содержит первый и второй блоки развертки, первую и вторую группы элементов ЗАПРЕТ, первую и вторую группы элементов ИЛИ три блока коммутации, причем первый и второй управляющие входы первого блока коммутации соединены с входами признака операции в двоичных кодах или в (г,р)-кодах при одинаковых знаках операндов и признака операции в (г,р)-кодах при разных знаках операндов устройства соответственно, упрвляющие входы второго блока коммутации соединены с входами признака операции в двоичных кодах и признака операции в (г,р)-кодах устройства соответственно, управляющие входы третьего блока коммутации соединены с входом признака операции в (г,р)- кодах при разных знаках операндов устройства, выходы первого и третьег блоков коммутации подключены к ин- формационным входам первого и второг блоков развертки соответственно, выходы которых соединены с второй и третьей группами входов блока определения окончания суммирования соответственно, выходы первого блока развертки соединены соответственно с прямыми входами элементов ЗАПРЕТ первой группы и с инверсными входами элементов ЗАПРЕТ второй группы, вы- ходы второго блока развертки соединены соответственно с инверсными входами элементов ЗАПРЕТ первой . группы и с прямыми входами элементов ЗАПРЕТ второй группы, первая и эторая группы информационных входов блока нормализации соединены с выходами второго блока коммутации и входами первого операнда устройства.

первая, вторая и третья группы информационных входов первого блока коммутации соединены соответственно с выходами разрядных переносов блока параллельного суммирования , выходами элементов ЗАПРЕТ второй группы и входами второго операнда устройства, первая .и вторая группы информационных входов второго блока коммутации соединены соответственно с выходами разрядных сумм блока параллельного суммирования и выходами элементов ИШ первой группы, первые и вторые входы элементов ИЛИ первой группы соединены соответственно с выходами разрядных сумм и разрядных переносов блока параллельного суммирования, входы которого соединены с выходами блока нормализации и первого блока развертки, первая и вторая группы Информационных входов третьего блока коммутации соединены с выходами элементов ЗАПРЕТ первой группы и входами первого операнда устройства, входы элементов ИЛИ второй группы соединены соответственно с выходами элементов ЗАПРЕТ первой и второй групп, выходы элементов ИЛИ второй группы соединены с первыми входами соответствующих элементов И группы, вторые входы которых .соединены с выкодом блока определения окончания суммирования, управляющий вход блока нормализации соединен с входом признака операции в (г,р)-кодах при одинаковых знаках операндов устройства, управляющие входы первого блока развертки соединены с входами признаков операции в (г,р)-кодах при одинаковых и разных знаках операндов устройства, управляюйщй вход второго блока развертки подключен к входу признака операции в (г,р)-кодах при разных знаках операндов устройства.

2. Устройство по п.1, о т л и - чающееся тем, что блок развертки содержит п триггеров, п элементов Ни (п+1) элементов ИЛИ (п - разрядность операндов), причем прямой вькод i-ro триггера (,...,п) соединен с соответствующим выходом блока, входы i-ro элемента ИЛИ соединены с соответствующим информационным входом блока и выходами всех предыдущих элементов И,.входы i-ro элемента И соединены с прямым выхол.11м i-iT) триггера, инверсными выхо-входами блока, выход i-rci племеита И

д;1м11 всех предыдущих триггеров исоединен с нулевым входом i--r o триггеныходом (i+1)-ro элеме {та ИЛИ, вхо-ра,единичный вход которого соединен с

ды KoTopoi o соединены с управляющими выходом соответствующего элемента ИЛИ.

Редактор Е. Копча

Пгиз

Физ.г

Составитель В. Нерезкин

Техред М.ХоданичКорректор Л, Пилипенко

Заказ 2986/51Тираж 671Лодписное

ВНИИЛИ Государственного комитета СССР

по делам изобретений и открытий 11.3035, Москва, Ж-35, Раушская наб., д. 4/5

rip(.ii3no;. пе1тчо-но.;1иг рафическое ггредприятие, г. Ужгород, ул. Проектная, 4

32

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Суммирующее устройство | 1990 |

|

SU1775722A1 |

| Вычислительное устройство | 1988 |

|

SU1517024A1 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

Изобретение относится к области цифровой вычислительной техзгаки. Целью изобретения является повьппение быстродействия. Для достижения поставленной цели в устройство введены первый и второй блоки развертки, первая и вторая группы элементов ЗАПРЕТ, блоки коммутадаи, группа элементов И, шины признака операций и соответствующие указанным блокам связи. Введение новых элементов и связей позволило реализовать один из оптимальных алгоритмов выполнения операции суммирования в избыточных г,р-кодах. 1 з.п. ф-лы, 2 ил. S

| Параллельный сумматор | 1976 |

|

SU559237A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Суммирующее устройство | 1979 |

|

SU824200A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-10-09—Подача