(54) УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ОБЪЕКТОМ

ния кода времени технологической

задержки или адрес перехода, четвертая - 1 разряд - для хранения призна технологической задержки, пятая - 1 разряд - для зфанения признака условного перехода,шестая - 1 разряд - д хранения признака безусловного перехода), которые считываются последовательно, начиная с первой группы. При наливши одинаковой информации на o6on входах схемы сравне шя на ее выходе появляется разрешающий уровень, поступающий на программный блок .СоДердамое второй группы разрядов поступает на блок вентилей.Если состояние объе та совпадает с содержимым первой группы разрядов ячейки памяти и нет признаков условного или безусловного перехода, то программный блок открывает блок вентилей, и содержимое вто рой группы разрядов ячейки (код команды) проходит через блок вентилей на блок исполнительных механизмов. При наличии сигнала совпадения на выходе схемы сравнения и признака те нологической задержки информация из третьей группы -разрядов ячейки записьшается в счетчик времеьш программного блока. Выбор следующей ячейки блока памяти происходит; тольк по истечении периода времени, соответствующего информации третьей .группы разрядов ячейки. При наличии признака условного перехода, сигнала совпаде1 шя на выходе схемы сравнения и условия перехода, информация из третьей части ячейки памяти переписьшается в счетчик адреса блока памяти, а при наличиипризнака безусловного перехода и сигнала совпадения на выходе схемы сравнения аналогичное перемещение происходит без дополнительного условия. Команды условного и безусловного переходов не исключают вьщачу кода кбмакды на исполнительные механизмы Г21.

Однако данное устройство характеризуется недостаточно эффективным использованием емкости блока памяти, приводящим к увеличению емк-ости блока памяти и уменьшению функциональных возможностей устройства для программного управления объектом, так как в качестве условия перехода к обработке следующей позиции(считыванию следующей ячейки блока памяти)используются обычно сигналы от датчиков выполнения команды .или (когда это невозможно или нецелес.ообразно)достижение заданной заранее выдержки време1Ш (времени термообработки, прессования, максимальной продолжительности механообработки или сборочной операции). Тогда при максимальном числе переходов технологического процесса m и максимальном Числе используемых интервалов времени, определяющем точность отбработки временных интервалов п, число, разрядов каждой ячейки блока памяти не может быть меньше значения 1од (m+n) При использовании сигналов от датчиков вводят условия, связанные с временными интервалами, например: перейти к отработке следующей -команды сразу же после получения сигнала от датдатчика а при отсутствии последнего по сигналу схемы вьщержки времени, С учетом использования таких комбинированных условий требуемое число двоичных разрядов каждой ячейки блока памяти не может быть меньше, чем log (т+ п + 2 mn).

Цель изобретения-- упрощение и расширение функцинальных возможностей устройства.

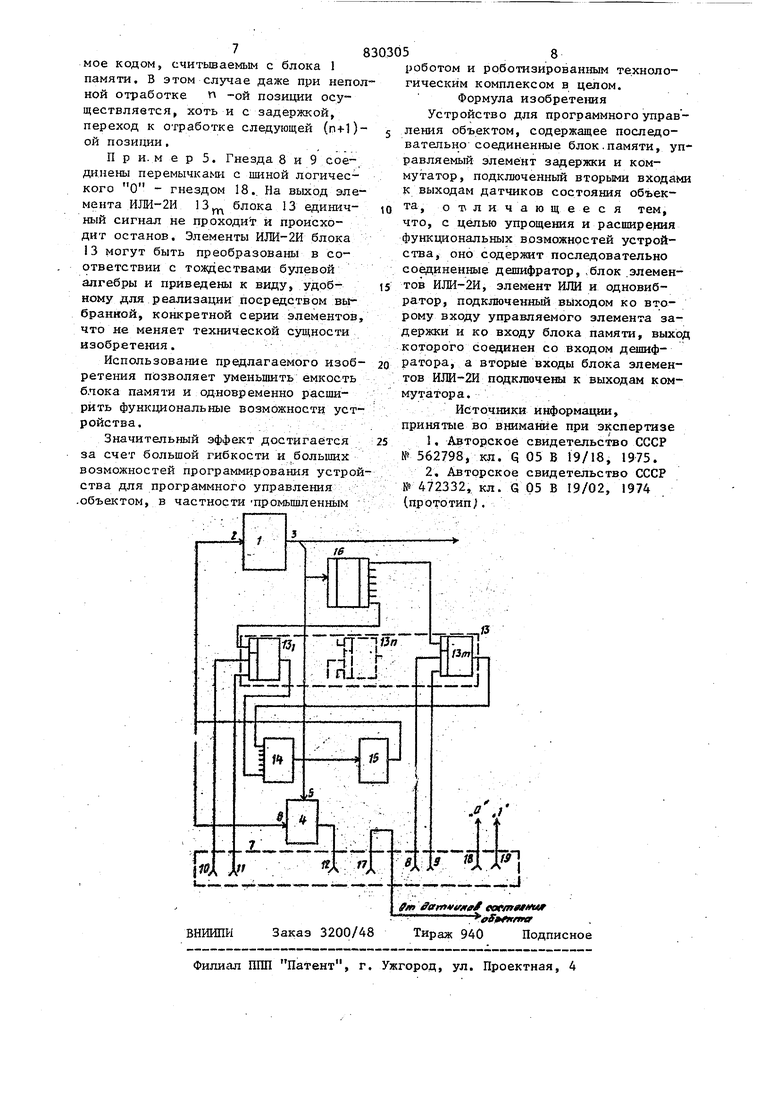

Цель достигается тем, что устройство для программного управления объектом, содержащее последовательно соединенные блок памяти, управляемый элемент задержки и коммутатор, подключенный вторыми входами к выходам датчиков состояния объекта, содерлсит последовательно соединенные дешифратор, блок элемейтов ИЛИ-2И, элемент ИЛИ и одновибратор, подключенный выходом ко второму входу управляемого элемента задержки и ко входу блока памяти, выход которого соединенгсо входом дешифратора, а вторые входы блока элементов ЙЛИ-2И под.ключены к выходам коммутатора,

Коммутация входов элементов ИЛИ2И в зависимости от конкретных требований позволяет использовать одно и то же управляющее слово, считываемое с блока памяти, для реализации различных условий перехода к отработке следующей позиции.

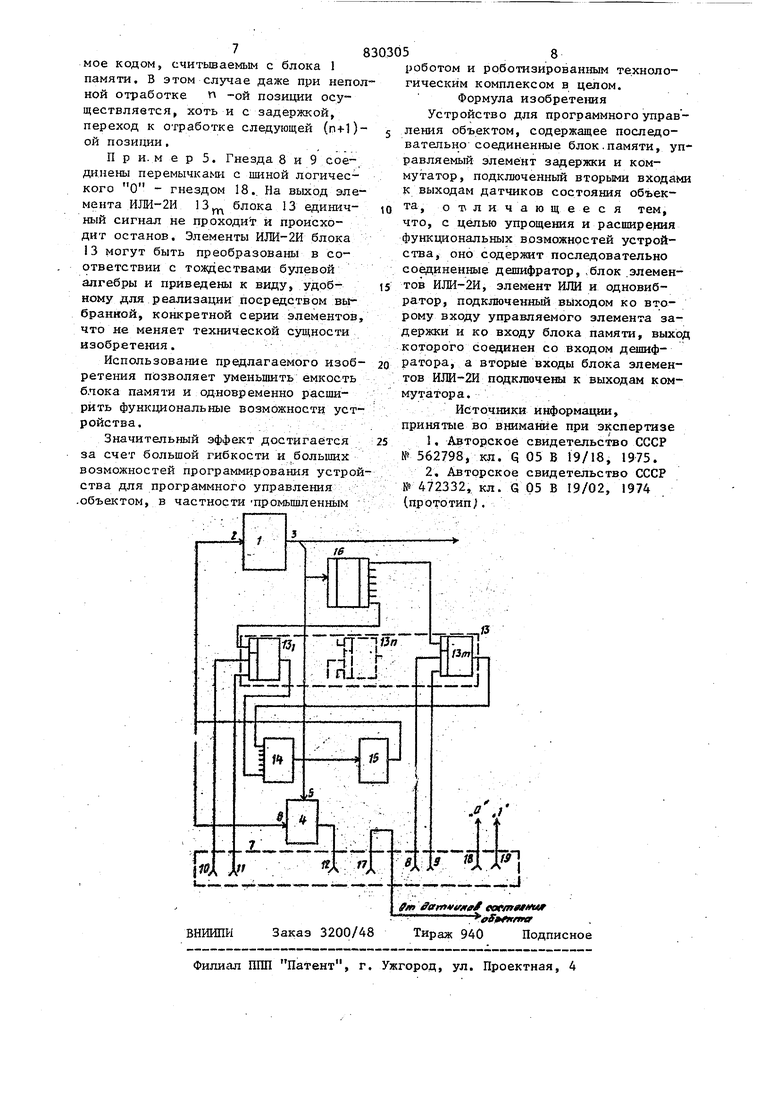

На чертеже приведена функциональная схема устройства.

Устройство содержит блок 1 памяти со входом 2 и выходом 3, управляемый эл гмент 4 задержки со входами 5 и 6. коммутатор 7 с гнездами 8-12 блок 13 элементов ИЛИ-2И, элемент ИЛИ 14, одновибратор 15 и .дешифратор 16, а коммутатор 7 имеет гнезда 17-19, датчики состояния объекта на чертеясё не показаны. Устройство работает следующим образом. При поступлении на вход 2 блока очередного импульса адрес, по которому происходит считывание в блоке увеличивается на единицу. Информационное слово, считанное по новому а,цресу, поступает на вход 3 блока 1 При этом происходит отработка позиции, заданной считанным информационным словом, а на входы.дешифратора 16 поступает в виде двоичного кода условие перехода к отработке следуюр;ей позиции. На одном из выходов дер1фратора 16 появляется единичный еигнал, который проходит через соот ретствующий элемент ИЛИ-2И блока 13 ||1ри условии поступления единичных Сигналов на другие входы этого эленента) затем через элемент 14 ИЛИ на вход одновибратора 15. На выходе одновибратора 15 вырабатывается импульс поступающий на вход 2 блока 1 и увеличивает адрес, по которому происход считывание в блоке 1 на единицу,При этом из блока 1 на вькод 3 выводится новое информационное слово и происхо дит отработка следующей позиции. Одновременно с изменением адреса в блоке 1 Импульс с выхода одновибратора 15 запускает элемент 4, на выходе которого единичный сигнал появляется через промежуток времени, определяемьй кодом, считанным с блока 1 и поступающим на вход 5 эле;мента 4. Перемычками на-, коммутационной панели могут быть установлены различные условия перехода,к отработке сле дующей позиции,причемусловия пере:хода -от отработки п -ой позиции к отработке (п-(-1)-ой позиции могут быть различными для различных п. Пример 1. Гнезда 8 и 9 соединены перемычками с шиной логическо 1 - гнездом 19. При считывании с блока I очередного управляющего блок такого, что код, поступающий на входы дешифратора 16, вызывает появление единичного сигнала на первом (верхнем на чертеже) выходе этого дешифратора, единичный сигнал поступает на первый вход элементов ИЛИ2И блока 13. На два других входа 56 этих элементов поступает сигнал логич-зской 1, поэтому сигнал, поступивший на первый вход элемента ИШ1-2И 13tn блока 13, сразу проходит на его выход, преходит через элемент ИЛИ 14 и запускает одновибратор 15. Импульс с выхода одноБибратора 15 поступает на вход 2 блока 1, увеличивает на единицу адрес блОка 1, обеспечивая переход к отработке следующей ( позиции. Таким образом, ,w -ая позиция не отрабатывается и исключается. .П р и м е р 2. Гнездо 8 соединено перемычкой с гнездом 12, а гнездо 9 с шиной логического О - гнездом 18 В этом случае при поступлении на цервый вход- элемента ИЛИ-2И 13 блока 13 единичного сигнала с выхода дешифратора 16 на выходе этого элемента единичный сигнал йоявляется через время,определяемое кодом,счи«танным с блока 1 и поступившим на входы 5 управления элемента 4,после чего осуществляется переход к отработке следующей . (п+1)-ой позиции. Таким ;образом, на отработку п -ой позиции отводится определенное время, задаваемое кодом, считьюаемым с блока 1. П р и м е р 3. Гнездо 8 соединено с шиной логического О гнездом 18, а гнездо 9 с гнездом J7. При поступлении на первый вход элемента ;ИЛИ-2И 13vn блока 13 единичного сигнала с выхода дешифратора 16 на выходе этого элемента единичный сигнал появляется лишь завершения отработки п -ой позиции, зафиксированной датчиком. В этом случае переход к отработке )-ой позиции осуществля.ется лишь при условии фактического Зсшершения отработки п -ой позиции. При невыполнении по какойлибо причине этого условия переход к отработке ()-ой позиции не происходит и отрабатывается останов. Пример 4. Установлены две. перемычки: меяду гнездом 9 и гнездом 17 и между гнездом 8 и гнездом 12. При поступлении на первый вход элемента ИЛИ.-2И ISiYi блока 13 единичного сигнала на выходе этого элеменщ единичный сигнал появляется после отработки Y -ой позиции, зафикс фсванной датчикам. В случае непоступления сигнала оТ датчика, единичнь Й сигнал на выходе элемента 13 блока 13 появляется через время, определяемое кодом, считьшаемым с блока памяти, В этом случае даже при непол ной отработке п -ей позиции осуществляется, хоть и с задержкой, переход к отработке следующей (п+1)ой позигдаи,

П р и. м е р 5. Гнезда В и 9 соединены перемычками с шиной логического О - гнездом 18., На выход элемента ИЛИ-2И 13 блока 13 единичный сигнал не проходит и происходит останов. Элементы ИЛИ-2И блока 13 могут быть преобразованы в соответствии с тождествами булевой алгебры и приведень: к виду, удобному для реализации посредством выбранной, конкретной серии элементов, что не меняет технической сущности изобретения.

Использование предлагаемого изобретения позволяет уменьшить емкость блока памяти и одновременно расширить функциональные возможности устройства.

Значительный эффект достигается за счет большой гибкости и больших возможностей программирования устройства для программного управления .объектом, в частности промьш1ленным

роботом и роботизированным технологическим комплексом в целом.

Формула изобрете1шя Устройство для программного управления объектом, содержащее последовательно соединенные блок.памяти, управляемый элемент задержки и коммутатор , подключенный вторьми входами К выходам датчиков состояния объекта.

о -влич а ющее с я тем,

что, с целью упрощения и расшире.ния функциональных возможностей устройства, оно содержит последовательно соединенные дешифратор,.блок .элементов ИЛИ-2И, элемент ИЛИ и одновибратор, подключенный выходом ко второму входу управляемого элемента задержки и ко входу блока памяти, выхо которого соединен со входом дешифратора, а вторые входы блока элементов ИЖ-2И подключены к выходам коммутатора.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР № 562798, кл, Q 05 В 19/18, 1975.

2,Авторское свидетельство СССР № 472332, кл. G 05 В 19/02, 1974 (пpoтoтип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для программного управления | 1982 |

|

SU1083159A1 |

| Устройство для имитации сбоев | 1985 |

|

SU1298925A2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для программного управления | 1990 |

|

SU1716482A1 |

| Асинхронное устройство для программного управления | 1987 |

|

SU1481712A1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU842814A1 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

Авторы

Даты

1981-05-15—Публикация

1979-08-02—Подача