.1 . ,

Изобретение относится к вычислительной технике -и может быть испольгзовано в системах, обрабатьшаюадих сообщения о большом количестве абонентов.

Известны устройства формирования гщреса, содержащие два распределите ля, элементы И, ИЛИ, генератор импульсов, -блок приема сигналов запуска и блок шифрации адреса Cll.

Однако эти устройства сложны.

Наиболее близким к предлагаемому является устройство прерывания, содержащее тактируемый счетчик адреса, управляющий -вход которого соединен с одним из информационных выходов триггера, другой информационный выхо триггера соединен с управляющим входом тактируемого сдвигового регистра выход которого соединен со входсял компаратора, другой вход компаратора соединен с информационными входами тактируемого сдвигового регистра и адаптера связи и с выходом мультиплексора входных сигналов, адресные входы которого соединены с выходами счетчика гщреса и информационными входами адаптера связи, выход кото-, рого соединен с установочным входом триггера Г21.

НедостатЬк устройства - большие аппаратурные затраты в условиях, когда сигнал запроса, от объекта выдается сигналами различной полярности. ,. . . ,;.; , . .

Цель изобретения - сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство, содержсодее коммута0тор входных сигналов, группу информационных входов которого является группой входов запросов устройства, ёадресный вход соединен с выходом счетчика адреса и информационным входом

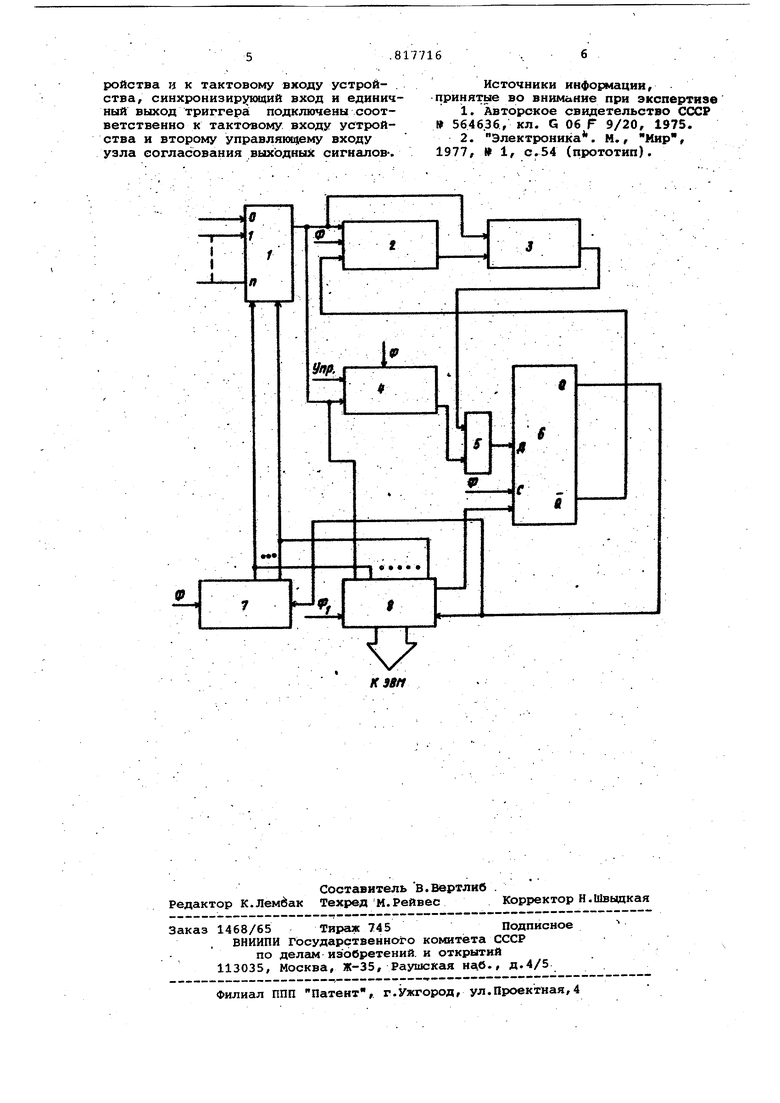

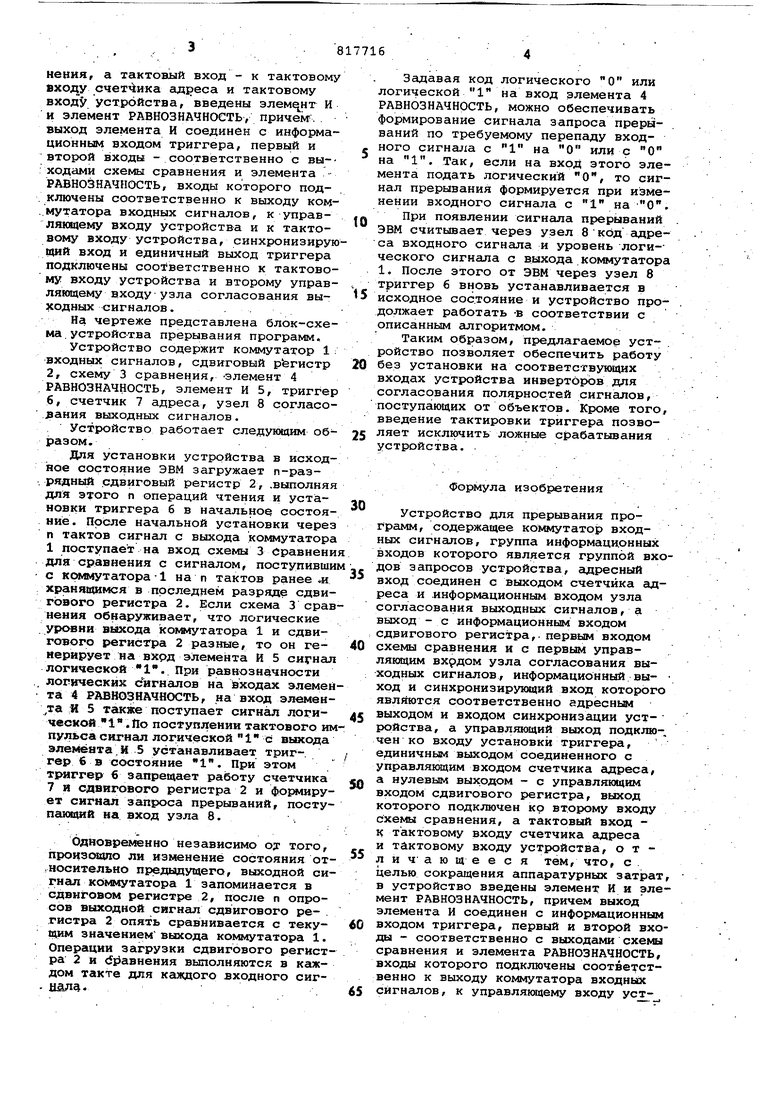

5 узла согласования выходных сигналов, а выход - с информационным входом сдвиового регистра, первым входом схемы сравнения и с первым управляющим входом узла согласования выход0ных сигналов, информационньай выход и синхронизирующий вход которого являются соответственно адресным выходом и входом синхронизации устройства, а управляющий выход подключен ко вхо5ду установки триггера, единичным выходом соединенного с управляющим входом сЧетчйка адреса, а нулевым выходом - с управляющим входом сдвигового регистра, выход которого под0ключен ко второму входу схемы сравнения, а тактовый вход - к тактовому входу адреса и тактовому входу устройства, введены элемент И и элемент РАВНОЗНАЧНОСТЬ, причем. выход элемента И соединен с информационным входом триггера, первый и второй входы - соответственно с вы-ходами схемы сравнения и элемента РАВНОЗНАЧНОСТЬ, входы которого подключены соответственно к выходу коммутатора входных сигнсШОБ, К управляющему входу устройства и к тактовому входу устройства, синхронизирую щий вход и единичный выход триггера подключены соответственно к тактовому входу устройства и второму управляющему входу узла согласования выходных сигналов. . На чертеже представлена блок-схема, устройства прерывания программ. Устройство содержит коммутатор 1 -: входнЕлх сигналов, сдвиговый регистр 2, схему 3 сравнения, Элемент 4 .РАВНОЗНАЧНОСТЬ, элемент И 5, триггер 6, счетчик 7 адреса, узел 8 согласования выходных сигналов. . Устройство работает следующим образом. Для установки устройства в исходное состояние ЭВМ загружает п-раз. рядный .сдвиговый регистр 2, .выполняя для этого п операций чтения и установки триггера б в начальное состояние. После начальной установки через п тактов сигнал с выхода коммутатора 1 поступает на вход схемы 3 Сравнени для сравнения с сигналом, поступивши с келлмутатора 1 на п тактов ранее «и храня&{имся в последнем разряде сдвигового регистра 2. Если схема 3 срав нения обнаруживает, что логические уровни вьисода колмутатора 1 и сдвигового регистра 2 разные, то он генерирует на вхрд элемента И 5 сигнал логической 1. При равнозначности логических с игналов на входах элемен та 4 РАВНОЗНАЧНОСТЬ, на ВХОД элемен та Я 5 также поступает сигнал логической 1.йо поступлении тактового им пульса сигнал логической 1 с выхода элемента,И 5 устанавливает триггер 6 в состояние 1. При этом триггер 6 запрещает работу счетчика 7 я сдвигового регистра 2 и формирует сигнал запроса прерываний, поступаю1вий на вход узла 8. Одновременно независимо од- того, произ(жшо ли изменение состояния от гНосительно предыдущего, выходной си гнал коммутатора 1 запоминается в сдвиговом регистре 2, после п опросов выходной сигнал сдвигового ре- . гистра 2 опять сравнивается с текущим значением выхода коммутатора 1. Операции загрузки сдвигового регист ра 2 и ; }авнения выполняются в каждом такте для каждого входного сиг. налаЗадавая код логического О или огической 1 на вход элемента 4 АВНОЗНАЧНОСТЬ, можно обеспечивать ормирование сигнала запроса прерыаний по требуемому перепаду входого сигнала с 1 на О или с О а 1. Так, если на вход этого элеента подать логический О, то сигал прерывания формируется при измеении входного сигнала с 1 на О. При появлении сигнала прерываний ВМ считывает через узел 8 ксзд адреса входного сигнала и уровень логи-ческого сигнала с выхода коммутатора 1. После этого от ЭВМ через узел 8 триггер 6 вновь устанавливается в исходное состояние и устройство продолжает работать -в соответствии с описанным алгоритмом. Таким образом, предлагаемое уст- . ройство позволяет обеспечить работу без установки на соответствующих входах устройства инверторов для согласования полярностей сигналов, поступающих от объектов. Кроме того, введение тактировки триггера позволяет исключить ложные срабатывания устройства. . Формула изобретения Устройство для прерывания программ, содержащее кок 1утатор входных сигналов, группа информационных входов которого является группой входов запросов устройства, адресный вход соединен с выходом счетчика адреса и информационным входом узла согласования выходных сигналов, а выход - с информационным входом сдвигового регистра, первым входом схемы сравнения и с первым управляющим ВХ9ДОМ узла согласования выходных сигналов, информационный вы- ход и синхронизирух ций вход которого явлйются соответственно адресным выходом и входом синхронизации устройства, а управляющий выход подклю-, чен ко входу установки триггера, единичным выходом соединенного с управляющим входом счетчика адреса, а нулевым выходом - с управляющим входом сдвигового регистра, выход которого подключен ко второму входу схемы сравнения, а тактовый вход К тактовому входу счетчика гщреса и тактовому входу устройства, отличающееся тем, что, с целью сокращения аппаратурных зат1рат, в устройство введены элемент И и элемент РАВНОЗНАЧНОСТЬ, причем выход элемента И соединен с информационным входом триггера, первый и второй входы - соответственно с выходами схемы сравнения и элемента РАВНОЗНАЧНОСТЬ, входы которого подключены соответственно к выходу коммутатора входных сИгнсшов, к управлякяцему входу устройства и к тактовому входу устрой- . ства, синхронизирглощий вход и единичный выход триггера: подключены соответственно к тактовому входу устройства и второму управляюилему входу узла согласования выходных сигналов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 5646.36, кл. G 06 F 9/20, 1975.

2. Электроника. М., Мир, 1977, 1, С.54 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения электроннойВычиСлиТЕльНОй МАшиНы C диСКРЕТНыМидАТчиКАМи | 1979 |

|

SU830367A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для сопряжения ЭВМ с факсимильным аппаратом | 1988 |

|

SU1524060A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Программируемый контроллер | 1989 |

|

SU1647594A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для управления обменом информации | 1981 |

|

SU1109729A1 |

Ф

9

л

Авторы

Даты

1981-03-30—Публикация

1979-04-04—Подача