Изобретение относится к автоматике и контрольно-измерительной технике и может быть использовано для получения минимизированных проверяющих тестов и тестов поиска дефекта дискретных автоматов.

Известно устройство для контроля и поиска неисправностей комбинационных схем,которое содержит источник питания, блок фиксации неисправностей коммутатор переменных логических функций, коммутатор переменных инверсных логическ.;х функций, выполненные матричными с двумя группами выходных шин. Мины одной группы яв.пяются общими для обоих коммутаторов и соединяются с соответствующими вход ными Шинами в одном из включенных положений коммутирующих элементов. Электронные ключи, управляющие входы которых через элемент ИЛИ подключены к входам шагового коммутатора и к выходным шинам другой группы данного коммутатора, соединяющиеся С входными шинами в другом включенном положении тех же коммутирующих элементов, соединены с управляющими входами диагностируемой схемы. Нагрузкой д иагностируемой схемы является блок фиксации неирправностей,

входы которого через коммутирующие элементы коммутатора конъюнкций подключены к одноименным входам шагового коммутатора, в каждом положении которого источник питания подключен одновременно к одной из входных шин одного матричного коммутатора совместно со всеми входными шинами и входами всех эле «ентов ИЛИ другого

0 коммутатора 1J.

Недостатком этого устройства является невозможность получения минимизированного теста для схем общего вида.

5

Наиболее близким по техническому ранению к предлагаемому является устройство для определения минимальных тестов контроля исправности релейных

0 структур, которое содержит триггер, переключатели и источник питания, в котором счетный вход каждого триггера через зa ftiкaющий контакт соответст вующего первого переключа еля и за5ыкaющий контакт общего переключателя соединен с положительной клеммой источника питания, нулевой и единичный входы каждого триггера через залыкающий контакт соответствующего второго

0 переключателя и размыкающий контакт

.общего переключателя соединен с клеммой источника питания 2.

Недостатком данного устройства является невозможность его применения для получения минимизированных тестов контроля сложных комбинационных схем.

Цель изобретения - расширение функциональных возможностей устройства и сокращение времени контроля сложных дискретных автоматов.

Устройство осуществляет ввод выражения и автоматическое получение одного из минимизированных тестов дл проверки дискретного автомата или поиска места дефекта.

Поставленная цель достигается тем что в устройство, содержащее блок индикации и последовательно соединенные блок управления и блок памяти введены блок суммирования, блок срав нения, блок логического умножения и блок инвертирования, причем блок суммирования своими входами соединен с первыми информационными выходами блока памяти, а выходом - со входом блока сравнения, первый и второй виходы которого подключены соответствено ко входу блока индикации и к упраляющему входу блока памяти, второй информационный выход которого через блок инвертирования, а третий информационный выход-непосредственно, подключены ко входам блока логического умножения, выход которого соединен со входрм перезаписи блока памяти.

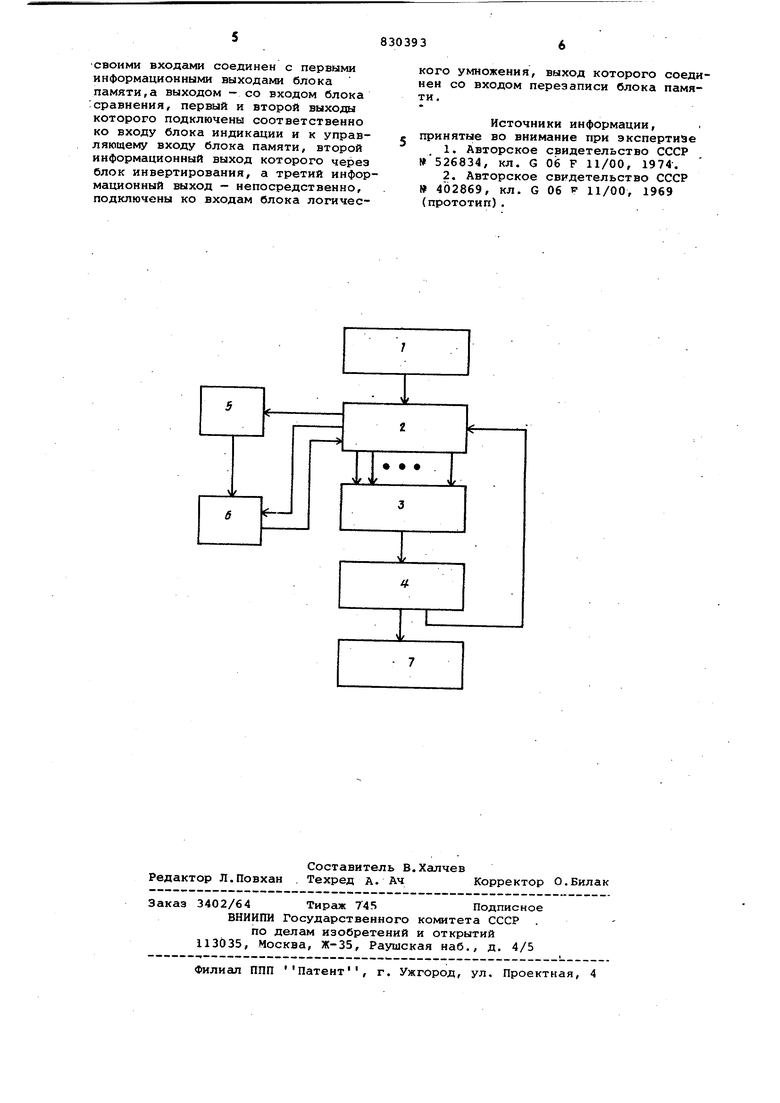

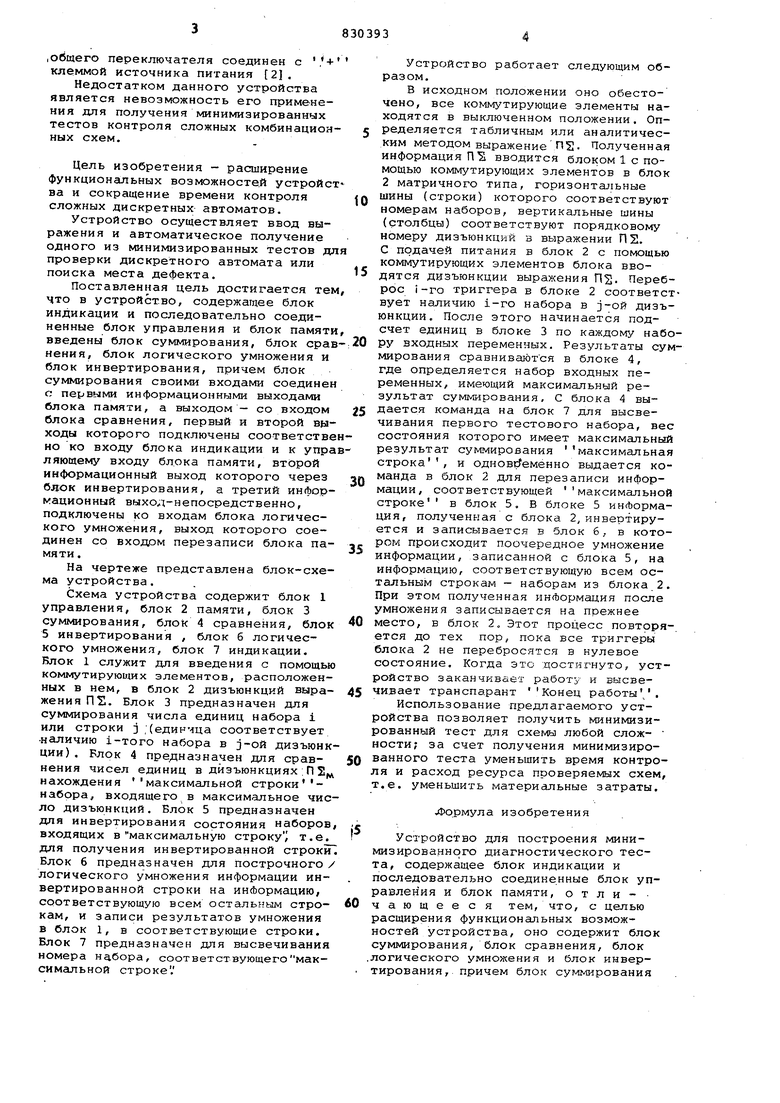

На чертеже представлена блок-схема устройства.

Схема устройства содержит блок 1 управления, блок 2 памяти, блок 3 суммирования, блок 4 сравнения, блок 5 инвертирования , блок 6 логического умножения, блок 7 индикации. Блок 1 служит для введения с помощью коммутирующих элементов, расположенных в нем, в блок 2 дизъюнкций выраженияПХ. Блок 3 предназначен для суммирования числа единиц набора i или строки j ;(единчца соответствует наличию i-Toro набора в j-ой дизъюнкции) . Блок 4 предназначен для сравнения чисел единиц в дизъюнкциях:П 2 нахождения максимальной строкинабора, входящего в максимальное число дизъюнкций. Блок 5 предназначен для инвертирования состояния наборов входящих в максимальную строку для получения инвертированной строки Блок 6 предназначен для построчного / логического умножения информации инвертированной строки на информацию, соответствующую всем остальным строкам, и записи результатов умножения в блок 1, в соответствующие строки. Блок 7 предназначен для высвечивания номера набора, соответствующего максимальной строке .

Устройство работает следующим образом.

В исходном положении оно обесточено, все коммутирующие элементы находятся в выключенном положении. Определяется табличным или аналитичес,ким методом выражение П2. Полученная информация nS вводится блоком 1 с помощью коммутирующих элементов в блок 2 матричного типа, горизонтальные шины (строки) которого соответствуют номерам наборов, вертикальные шины (столбцы) соответствуют порядковому номеру дизъюнкций в выражении П51. С подачей питания в блок 2 с помощью коммутирующих элементов блока вводятся дизъюнкции выражения П2- Переброс i-ro триггера в блоке 2 соответствует наличию 1-го набора в j-ой дизъюнкции. После этого начинается подсчет единиц в блоке 3 по каждому набору входных переменных. Результаты суммирования сравниваются в блоке 4, где определяется набор входных переменных, имеющий максимальный результат суммирования, С блока 4 выдается команда на блок 7 для высвечивания первого тестового набора, вес состояния которого имеет максимальный результат суммирования максимальная строка , и одновременно выдается команда в блок 2 для перезаписи информации, соответствующей максимальной строке в блок 5. В блоке 5 информация, полученная с блока 2, инвертируется и записывается в блок 6, в которог4 происходит поочередное умножение информации, записанной с блока 5, на информацию, соответствующую всем остальным строкам - наборам из блока 2. При этом полученная информация после умножения записывается на прежнее место, в блок 2, Этот процесс повторя ется до тех пор, пока все триггеры блока 2 не перебросятся в нулевое состояние. Когда это достигнуто, устройство заканчивает работу и высвечивает транспарант Конец работы/.

Использование предлагаемого устройства позволяет получить минимизированный тест для схемы любой слож- мости; за счет получения минимизированного теста уменьщить время контроля и расход ресурса проверяемых схем, т.е. уменьщить материальные затраты.

Л ормула изобретения

Устройство для построения минилоизированного диагностического теста, содержащее блок индикации и последовательно соединенные блок управления и блок памяти, о т л и - чающееся тем, что, с целью расширения функциональных возможностей устройства, оно содержит блок суммирования, блок сравнения, блок .логического умножения и блок инвертирования, причем блок суммирования

СВОИМИ входами соединен с первыми информационными выходами блока памяти,а выходом - со входом блока

:сравнения, первый и второй выходы которого подключены соответственно ко входу блока индикации и к управляющему входу блока памяти, второй информационный выход которого через блок инвертирования, а третий информационный выход - непосредственно, подключены ко входам блока логического умножения, выход которого соединен со входом перезаписи блока памяти.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР . 526834, кл. G 06 F 11/00, 1974.

2.Авторское свидетельство СССР 402869, кл. G 06 Р 11/00, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля матриц памяти | 1982 |

|

SU1027780A2 |

| Устройство умножения булевых матриц | 1980 |

|

SU959063A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

| УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ ОСНОВАМ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ | 1991 |

|

RU2011230C1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для управления лучом плоской антенной решетки | 1983 |

|

SU1167616A1 |

| Устройство для контроля матриц памяти | 1980 |

|

SU898507A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

Авторы

Даты

1981-05-15—Публикация

1979-07-20—Подача