(54) УСТРОЙСТЮ дай МОДЕЛИРОВАНИЯ ЦИФРОаК ОБЪЕКТОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования цифровых объектов | 1979 |

|

SU898438A1 |

| Устройство для моделирования цифровых объектов | 1976 |

|

SU610114A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для моделирования цифровых объектов | 1985 |

|

SU1312601A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1983 |

|

SU1111173A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Генератор испытательных последовательностей | 1987 |

|

SU1543396A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

1

. Изобретение относится к вычислительной технике и может быть использовано для проверки правильности работы проектируемых схем различных объектов цифровой вычислительной техНИКИ и автоматики в процессе их разработки, а также для исследования полноты контролируквдих тестов, применяемых при производственном и эксплуатационном контроле этих объектов. .

известны устройства для моделирования цифровых объектов, содержацие переменную моделируюдую структуру матричный коммутатор, блок настройки коммутатора и блок управления ,

Недостаток устройства - большое количество требуемых коммутационных устройств непосредственно в матричHceij коммутаторе, а также в блоке настройки коммутатора.

Наиболее близким техническим решением к предлагаемому является устройство для моделирования цифровых объектов, содержащее блок переменной моделирукщей структуры, выходы которого.соединены с информационными выходсцуш устройства и с первой группой входов коммутатора, вторая группа входов которого является ин- формацйонным входом устройства, и

блок памяти, вход и выход которого подключены соответственно к первому выходу и первому входу блока управления, второй и третий выходы которого соединены соответственно с информационным и упргшляюцим входами блсжа переключения выходы которого подключены к входам регистра, выходы которого соединешя-с входами блока переменной моделирующей структуры, четвертый и пятый выходы блока управления подключены соответственно к управляющему входу регистра и к управляющему выходу устройства, третий вход блока управления соединен с управляюацяы входом устрсЛ ства 2.

При работе известного устройства реализуется программируеьшй последовательный обмен инфо рмгщией между выходами и входами .интегрсшьных схем, ВХОДК1ЦИХ в блок переменной моделирующей структуры,.в соответствии с таблицей их соединений -в моделируемом объекте. При этом соединение-заданного выхода некоторой микросхеки с входами других микросхем задается программно в виде цепочки команд, где первая команда указывает номер (адрес) данного выхода, а последующие команды - номера (адреса) входов.

с KOTOpfcoMH этот выход должен быть соединен.

Недостаток устройства - увеличенный объем блока памяти за счет наличия первой команды в каждой цепочке команд, хотя по самой процедуре функционирования устройства это является излишним. Метод итерации Зейделя, используемый в из.вестном устройстве Для определения логических состояний моделируемого объекта, предполагает последовательное изменение состояния на каждой группе соединенных между собой входов микросхе моделируемого цифрового объекта в соответствии с состоянием выхода микросхемы, связанного с этими входами, и последующий опрос всех выходой микросхем с целью обнаружения изменения состояния хотя бы одного из них. Изменение состояния в каждой итерации хотя бы одного из выходов микросхем свидетельствует о том, что процесс установления нового состояния модели не закончился и необходимо продолжение цикла итераций.

Таким образом, в каждой итерации

необходим опрос состояния всех вьдходов микросхем и сравнение этого состояния с предыдущем состоянием этого же выхода. Вследствие этого адресный опрос выходов микросхем, используемый в известном устройстве, может быть заменен циклическим (последовательным), опросом, что приводит к сокращению длины каждой цепооди команд и, следовательно, к сокращению объема памяти, а также некоторому повышению быстродействия устройства.

Цель изобретения - уменьшение объема памяти устройства для моделирования цифровых объектов и повышение быстродействия.

Поставленная цель достигается тем что в устройство, содержащее блок переменной моделирующей структуры, выходы которого соединены с информационными выходами устройства и с пер вой группой входов коммутатора, вторая группа входов которого является информационным входом устройства, и блок памяти, вход и выход которого подключены соответственно к первому

, выходу и первому входу блока управления, второй и третий выходы которого соединены -соответственно с информационным и управляющим входами блока переключения, выходы которого подключены к входам регистра, выходы которого соединены с входами блока переменной моделирующей структуры, четвертый и пятый выходы блока управления подключены соответственно к управляющему входу регистра и к управляющему выходу устройства, третий вход блока управления соединен с управляющим входом устройства, введен счетчик, вход и выход которого соединены с шестым выходом блока управления и с управляющим входом коммутатора,соответственно, седьмой выход блока управления подключен к адресному входу блока памяти.

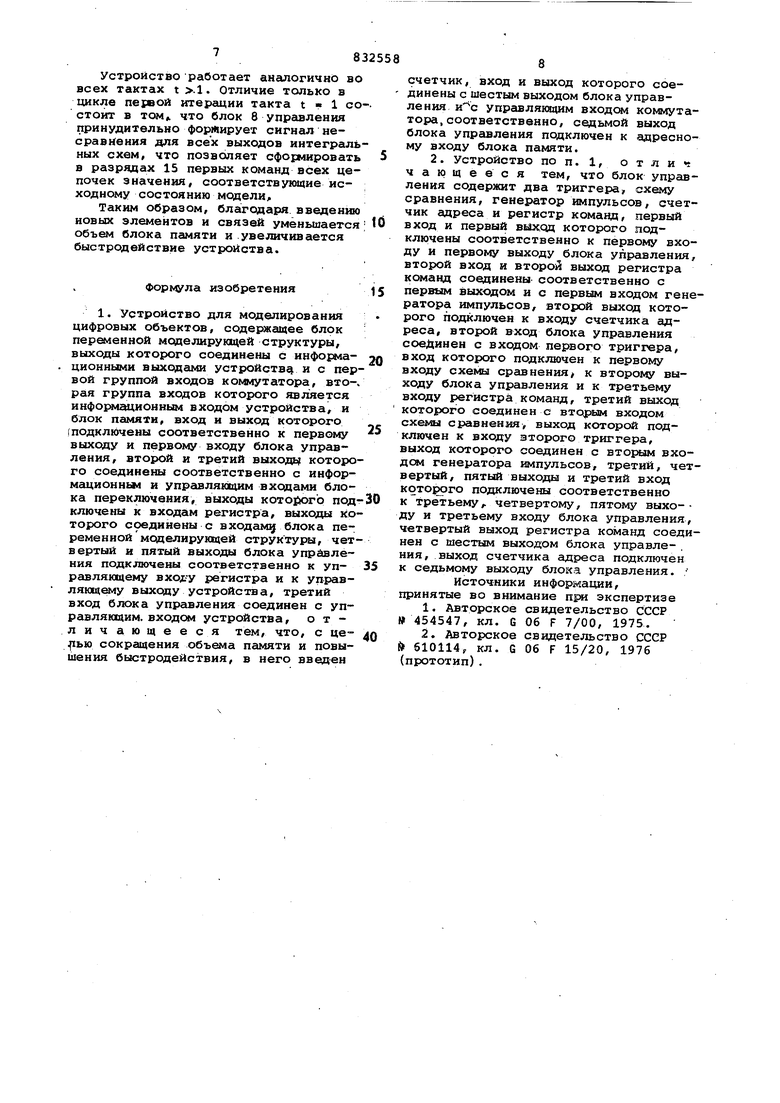

Кроме того, блок управления содержит два триггера, схему сравнения, генератор импульсов, счетчик адреса и регистр команд, первый вход и первый выход которого подключены соответственно к первому входу и первому выходу блока управления, второй вход и второй выход регистра команд соединены соответственно с первым выходом и с первым входом генератора импульсов, вто.рой выход которого подключен к входу счетчика адреса, второй вход блока управления соединен с входом первого триггера, выход которого подключен к первому входу схемы сравнения, к второму выходу блока управления и к третьему входу регистра команд, третий выход которого соединен с вторым входом схемы сравнения выход которой подключен к входу второго триггера, выход которого соединен с вторым входом генератора импульсов третий, четвертый, пятый выходы и третий вход которого подключены соответственно к третьему, четвертому, пятому выходу и третьему входу блока управления, четвертый выход регистра команд соединен .с шестым выходом блока управления, выход счетчика адреса подключен к седьмому выходу блока управления.

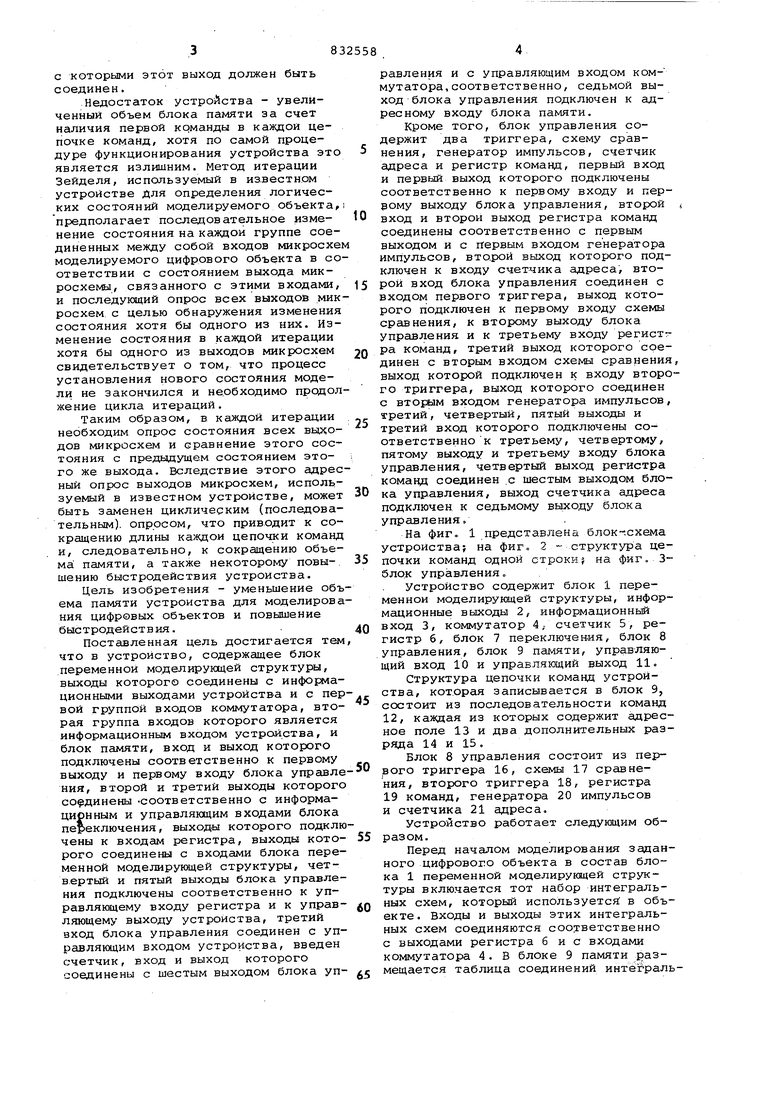

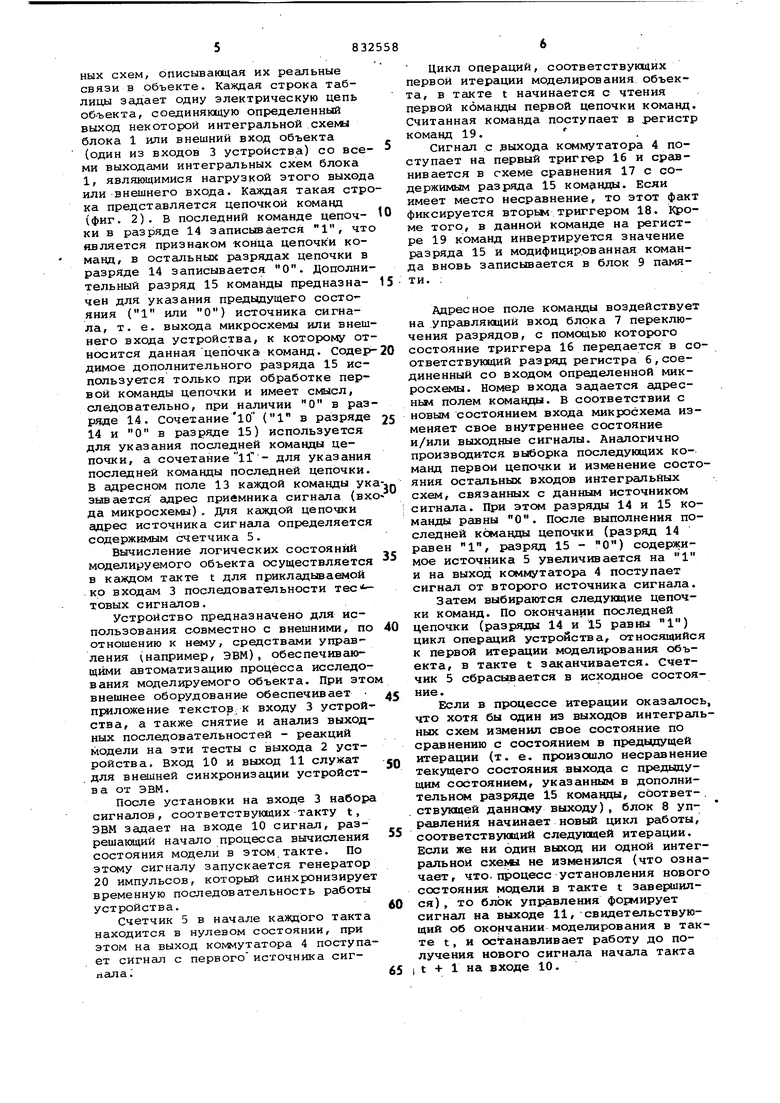

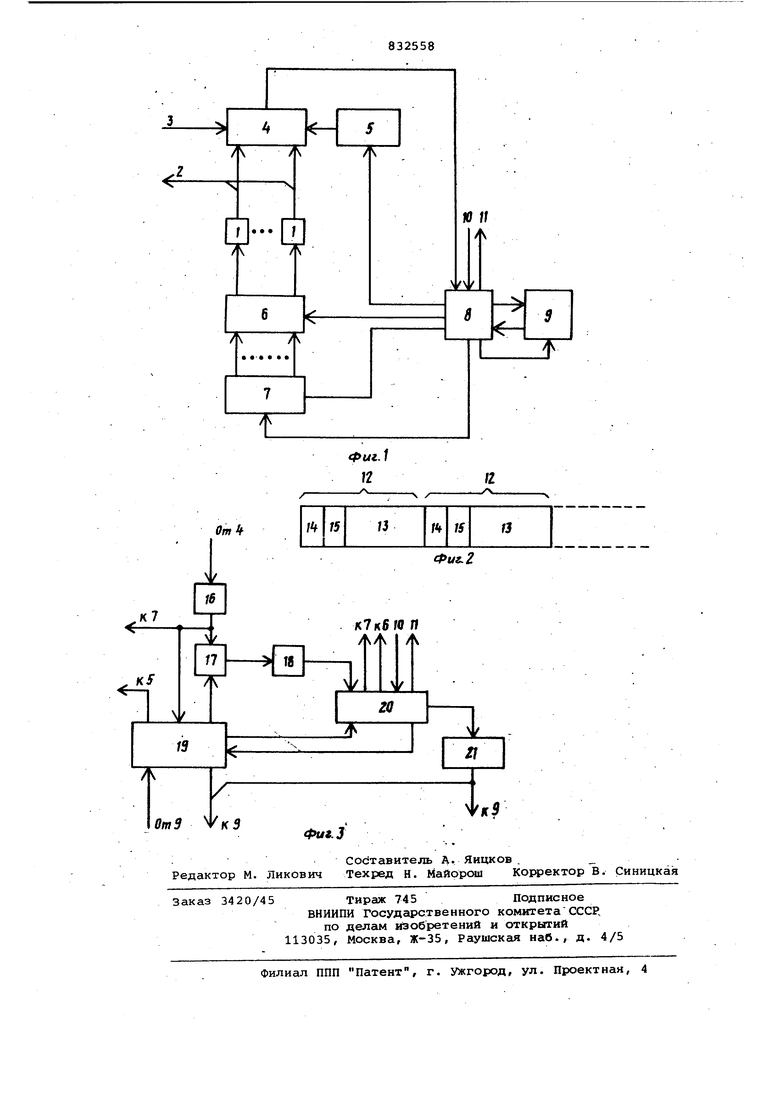

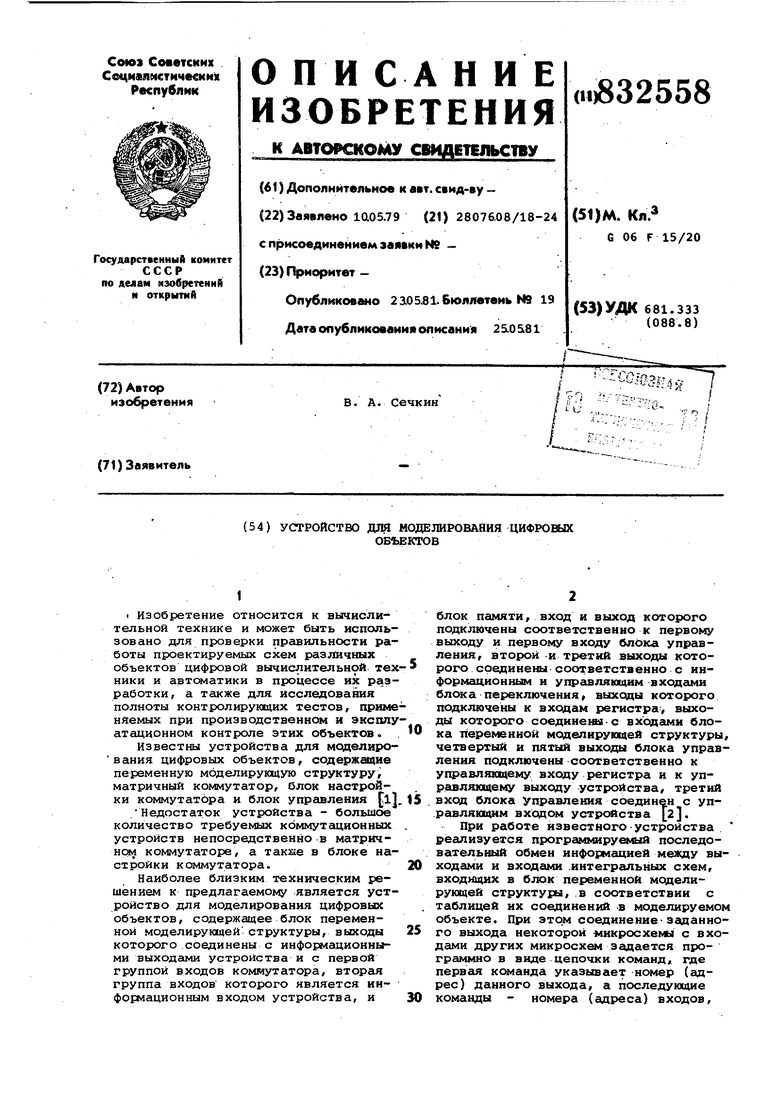

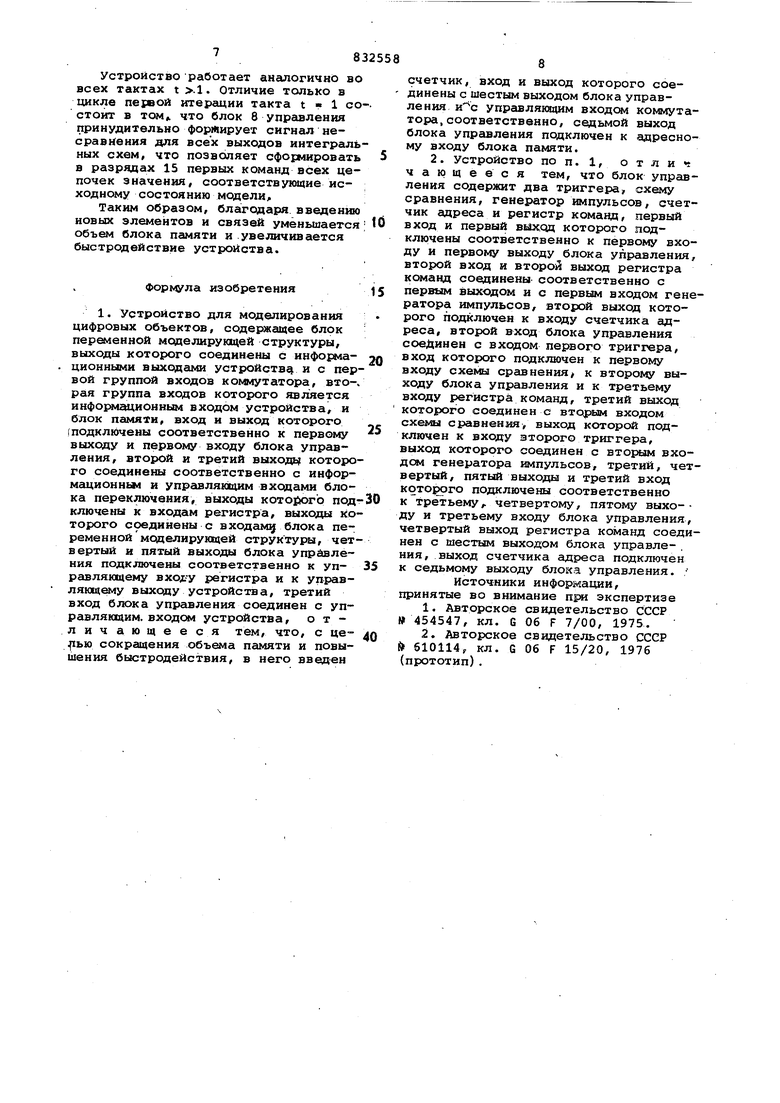

На фиг. 1 представлена блок-.схема устройства; на фиг. 2 - структура цепочки команд одной строки на фиг. 3блок управления.

Устройство содержит блок 1 переменной моделирукЕцей структуры, информационные выходы 2, информационный вход 3, коммутатор 4,- счетчик 5, регистр 6, блок 7 переключения, блок 8 управления, блок 9 , управляющий вход 10 и управлягадий выход 11.

Структура цепочки команд устройства, которая записывается в блок 9, состоит из последовательности команд 12, каждая из которых содержит адресное поле 13 и два дополнительных разряда 14 и 15 .

Блок 8 управления состоит из первого триггера 16, схемы 17 сравнения, второго триггера 18, регистра 19 команд, генератора 20 импульсов и счетчика 21 адреса.

Устройство работает следугацим образом.

Перед началом моделирования заданного цифрового объекта в состав блока 1 переменной моделирукщей структуры включается тот набор интегральных схем, который используется: в объекте. Входы и выходы этих интегральных схем соединяются сооз ветственно с выходами регистра бис входс1ми коммутатора 4. В блоке 9 памяти размещается таблица соединений интегральных схем, описывающая их реальные связи в объекте. Каждая строка таблицы задает одну электрическую цепь объекта, соединяющую определенный вьоход некоторой интегральной схекы блока 1 или внешний вход объекта (один из входов 3 устройства) со все ми выходами интегральных схем блока 1, являющимися нагрузкой этого выход или внешнего входа. Каждая такая стрка представляется цепочкой команд (фиг. 2). В последний команде цепочки в разряде 14 записывается 1, чт является признаком -койца цепочки команд, в остальных разрядах цепочки в разряде 14 записывается О. Дополнительный разряд 15 команды предназначен для указания предыдущего состояния (1 или О) источника сигнала, т. е. выхода микросхемы или внешнего входа устройства, к которюму относится данная цепочка команд. Содер димое дополнительного разряда 15 используется только при обработке первой команды цепочки и имеет смысл, следовательно, при наличии О в разряде 14. Сочетание 10 (1 в разряде 14 и О в разряде 15) используется для указания последней команды цепочки, а сочетание 11 - для указания последней команды последней цепочки. В адресном поле 13 каждой команды укзывается адрес приемника сигнала (вх да микросхемы), Для каждой цепочки

адрес источника сигнгипа определяется содержимым счетчика 5.

Вычисление логических состояний моделируемого объекта осуществляется в ка)едом такте t для прикладываемой ко входам 3 последовательности тес товых сигналов.

Устройство предназначено для использования совместно с внешними, по отношению к нему, средствами управления (например/ ЭВМ), обеспечивающими автоматизацию процесса исследования моделируемого объекта. При это внешнее оборудование обеспечивает приложение текстов,к входу 3 устройства, а также снятие и анализ выходных последовательностей - реакций модели на эти тесты с выхода 2 устройства. Вход 10 и выход 11 служат для внешней синхронизации устройства от ЭВМ.

После установки на входе 3 набора сигналов, соответствукиих такту t, ЭВМ задает на входе 10 сигнал, разрешающий начало процесса вычисления состояния модели в этом такте. По этому сигналу запускается генератор 20 импульсов, который синхронизирует временную последовательность работы устройства.

Счетчик 5 в начале каждого такта находится в нулевом состоянии, при этом на выход коммутатора 4 поступает сигнал с первого источника сигнала.

Цикл операций, соответствующих первой итерации моделирования объекта, в такте t начинается с чтения первой команды первой цепочки команд Считанная команда поступает в регистр команд 19.

Сигнал с эыхода коммутатора 4 поступает на первый тригге-р 16 и сравнивается в схеме сравнения 17 с содержимым разряда 15 команды. Если имеет место несравнение, то этот факт фиксируется вторьм триггером 18. Кроме того, в данной команде на регистре 19 команд инвертируется значение разряда 15 и модифицированная команда вновь записывается в блок 9 памяти. :

Адресное поле команды воздействует на .управляюций вход блока 7 переключения разрядов, с помощью которого состояние триггера 16 передается в соответствующий разряд регистра 6,соединенный со входом определенной микросхемы. Номер входа задается адресньм полем команды. В соответствии с новым состоянием входа микросхема изменяет свое внутреннее состояние и/или выходные сигналы. Аналогично производится выборка последующих команд первой цепочки и изменение состояния остальных входов интегральных схем, связанных с данным источником сигнала. При этом разряда 14 и 15 команды равны О. После выполнения последней команды цепочки (разряд 14 равен 1, разряд 15 - О) содержимое источника 5 увеличивается на 1 и на выход коммутатора 4 поступает сигнал от второго источника сигнала.

Затем выбираются следующие цепочки команд. По окончании последней цепочки (разряды 14 и 15 равны 1) цикл операций устройства, относящийся к первой итерации моделирования объекта, в такте t заканчивается. Счетчик 5 сбрасывается в исходное состояние.

Если в процессе итерации оказалось что хотя бы рдин из выходов интегральных схем изменил свое состояние по сравнению с состоянием в предьщущей итерации (т. е. произошло несравнение текущего состояния выхода с предыдущим состоянием, указанным в дополнительнее разряде 15 комаццы, сЬответствукщей данному выходу), блок 8 управления начинает новый цикл работы, соответствукщий следукшей итерации. Если же ни одкн выход ни одной интегральной cxeiiu не изменился (что означает, что. процесс установления нового состояния модели в такте t завериился), то блок управления формирует сигнсШ на выходе 11,свидетельствующий об окончании моделирования в такте t , и останавливает работу до получения нового сигнала начала такта t + 1 на входе 10. Устройство работает аналогично во всех тактах t .1. Отличие только в цикле первой итерации такта t 1 со стоит в том что блок 8 управления принудительно формирует сигнал несравнения для всех выходов интеграль ных схем, что позволяет сформировать в разрядах 15 первых команд всех цепочек значения, соответствующие исходному состоянию модели Таким образом, благодаря введению новых элементов и связей уменьшается объем блока памяти и увеличивается быстродействие устройства. формула изобретения 1. Устройство для моделирования цифровых объектов, содержащее блок переменной моделирующей структуры, выходы которого соединены с информационными выходами устройству и с пер вой группой входов коммутатора, вторая группа входов которого является информационным входом устройства, и блок памяти, вход и выход которого (подключены соответственно к первому выходу и первому входу блока управления, второй и третий выходь; которо го соединены соответственно с информационные и управляющим входами блока переключения, выходы под ключены к входам регистра, выходы ко торого ссюдинены с входамц блока переменной моделирунщей структуры, чет вертый и пятый выходы блока упрдвления подключены соответственно к управлянщему axof-y регистра и к управляющему выходу устройства, третий вход блока управления соединен с управляющим, входом устройства, о т л ич ающе е ся тем, что, с сокращения объема памяти и повышения быстродействия, в него введен счетчик, вход и выход которого соединены с шестым выходом блока управления управляющим входс коммутатора, соответственно, седьмой выход блока управления подключен к адресному входу блока памяти. 2. Устройство по п. 1, отлип чающееся тем, что блок управления содержит два триггера, схему сравнения, генератор импульсов, счетчик адреса и регистр команд, первый вход и первый выхсд которого лодклк)чены соответственно к первому входу и первому выходу блока управления, второй вход и второй выход регистра соединены соответственно с первьш выходом и с первым входом генератора импульсов, второй выход которого подключен к входу счетчика адреса, второй вход блока управления соединен с входом первого триггера, вход которого подключен к первому входу схемы сравнения/ к второму выходу блока управления и к третьему входу регистра команд, третий выход которого соединен с вто1{жм входом схемы сравнения, выход которой подключен к входу второго триггера, выход которого соединен с вторым входом генератора импульсов, третий, четвертый, пятый выходы и третий вход которого подключены соответственно к третьему,, четвертому, пятому выко- ду и третьему входу блока управления, четвертый выход регистра команд соединен с шестым выходом блока управле- . ния, выход счетчика адреса подключен к седьмому выходу блока управления. / Источники информации, принятые во внимание прк экспертизе 1.Авторское свидетельство СССР №454547, кл. G Об F 7/00, 1975. 2.Авторское свидетельство СССР ft 610114, кл. G 06 F 15/20, 1976 (прототип).

Фиг. 2

Авторы

Даты

1981-05-23—Публикация

1979-05-10—Подача