H.TOOjH TOiine относится к вычислительной К Хмикс и можс-г быгь исио. и.зовино д.чя про в.рки пргс ллыин ти работ1 1 проекгирчч мых логических схем разли П11 1х объектов цифровой техиики и автоматики и процессе их 1)а:фаботки, а также д.пн исследования (}|екгинности (io. UioTi i) контролирующих lecroB, применяемых при ироизводсгвепном и : ксплуатапионном коптроле этих объектов.

lie. ibK) и юбретения яв,чяе 1 ся расширение функнио11а.11)ИЫх возможностс-й за счет обес- нечопия модсмирования об1,ектов. содержащих интеграл1Л1Ыо схемы с В1 1ход11ыми контактами, об 1 еди11ясмымн в общую тину, 1икрос е И)1, имсмошие выхо. с тремя ус1()й- чивыми состоящими, и микросхем) е диу- 1и111)аил(-иными кои 1 ак га ми.

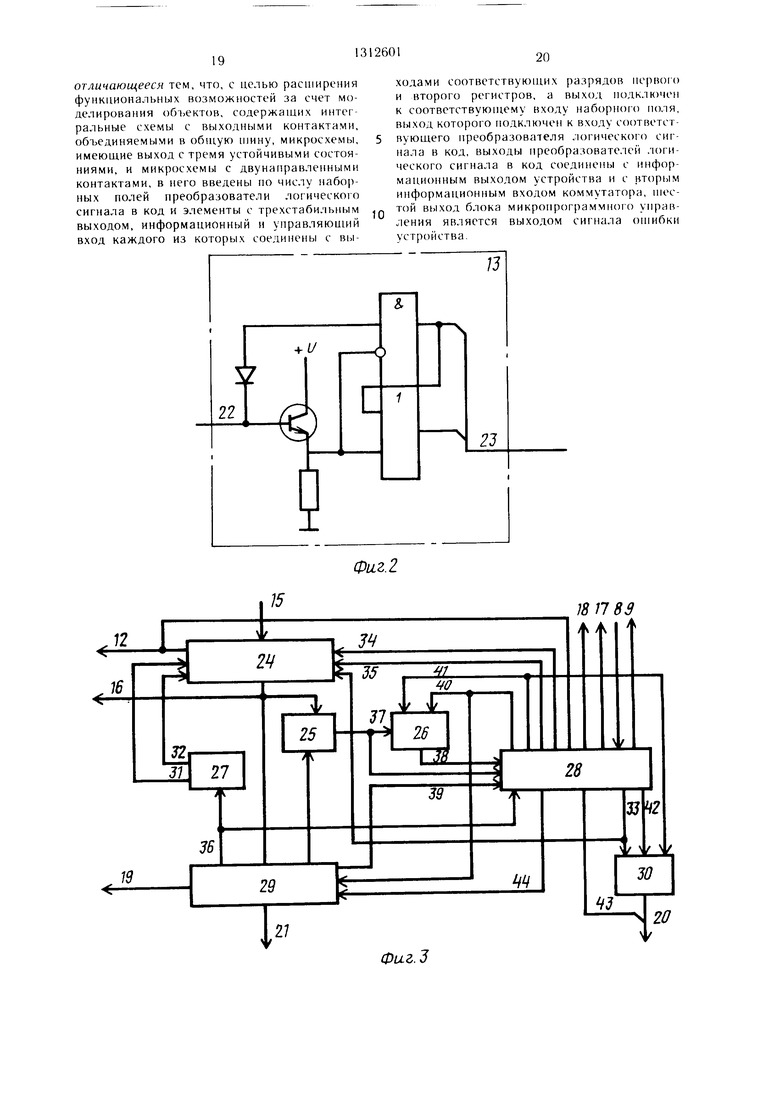

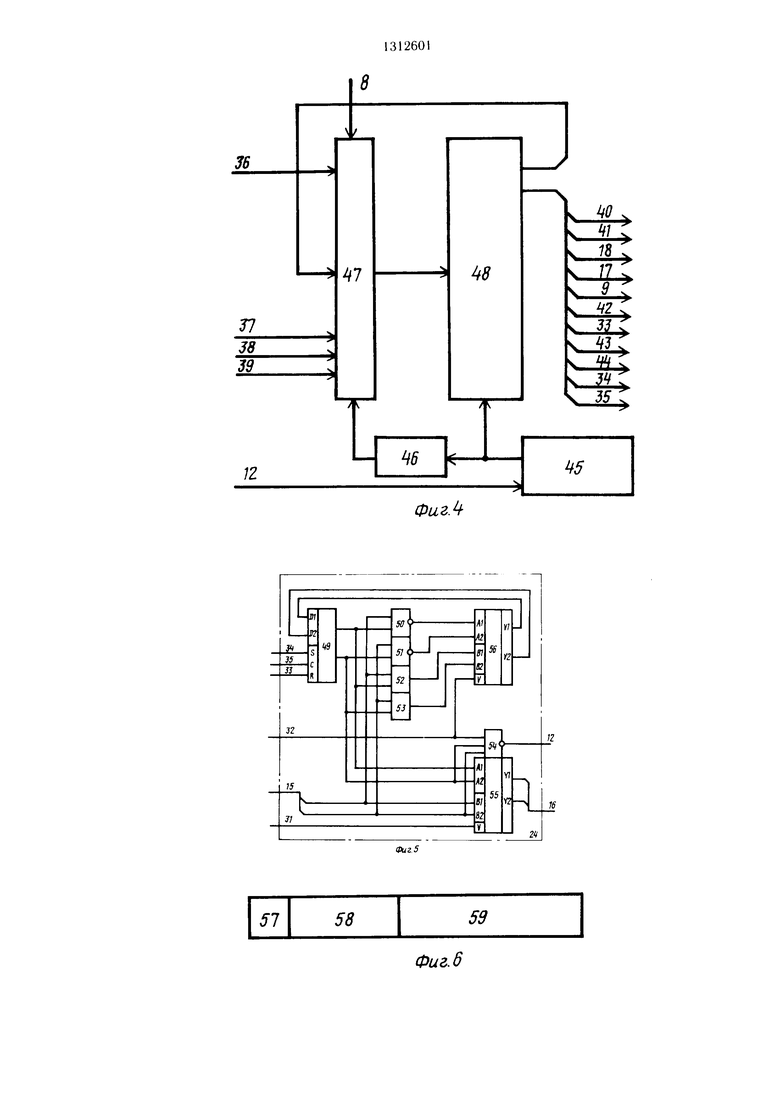

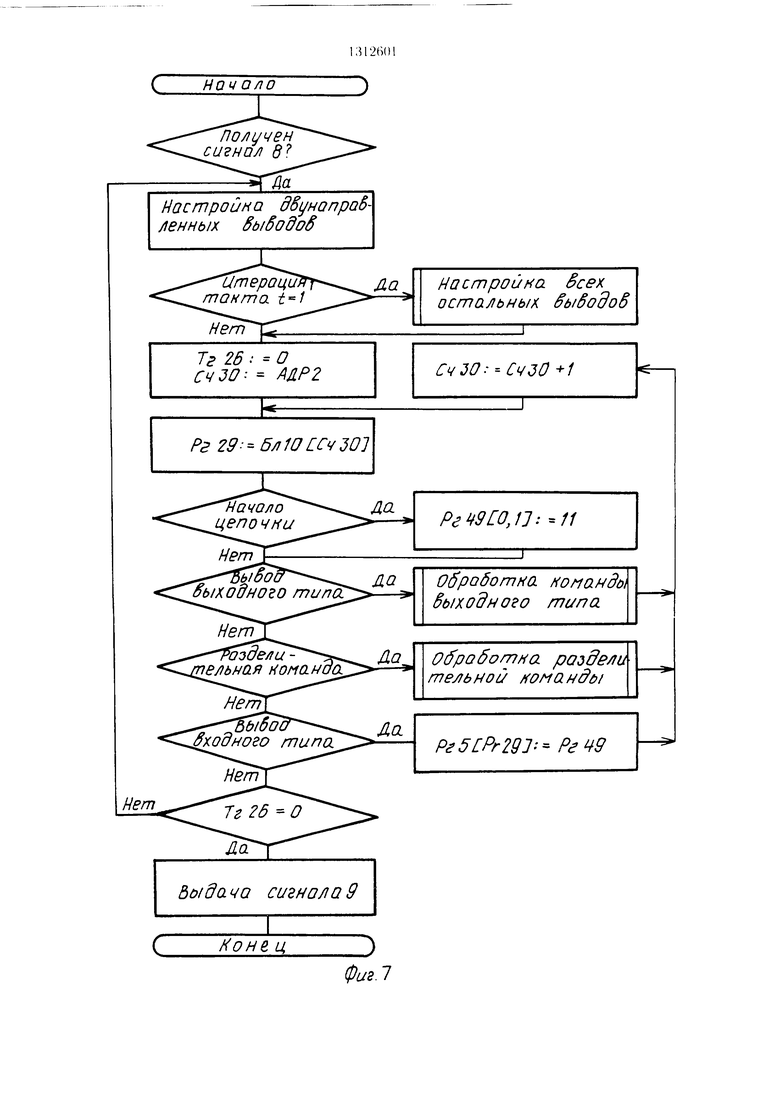

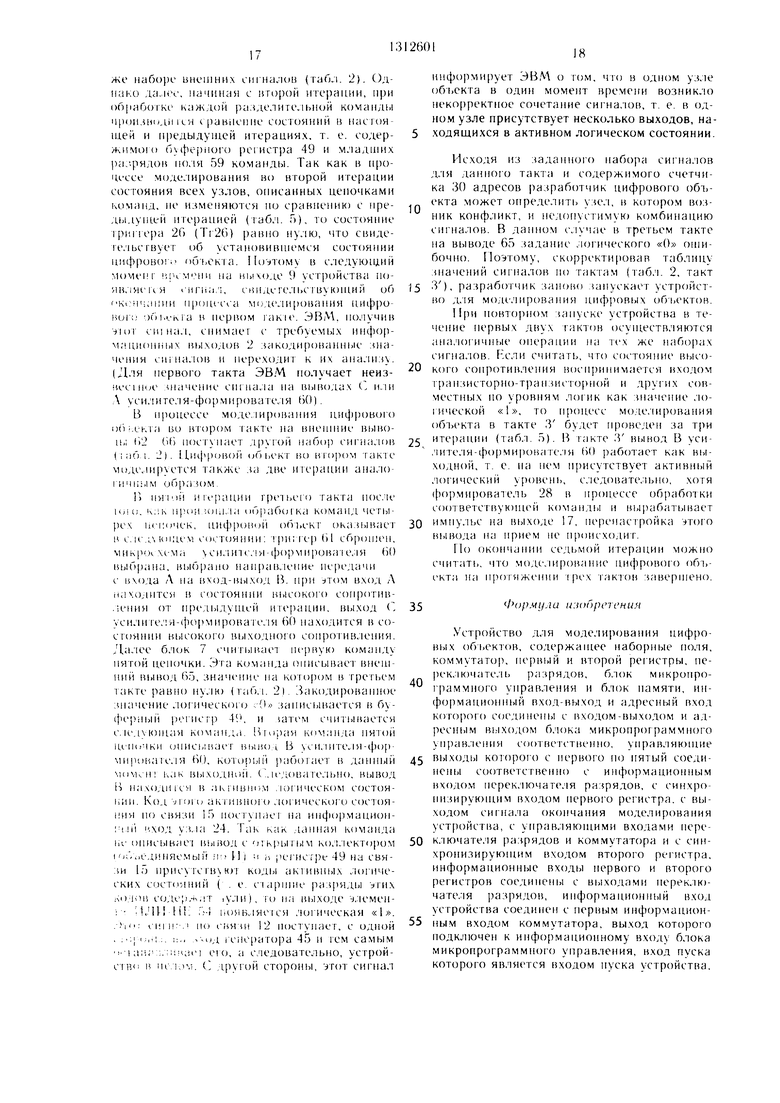

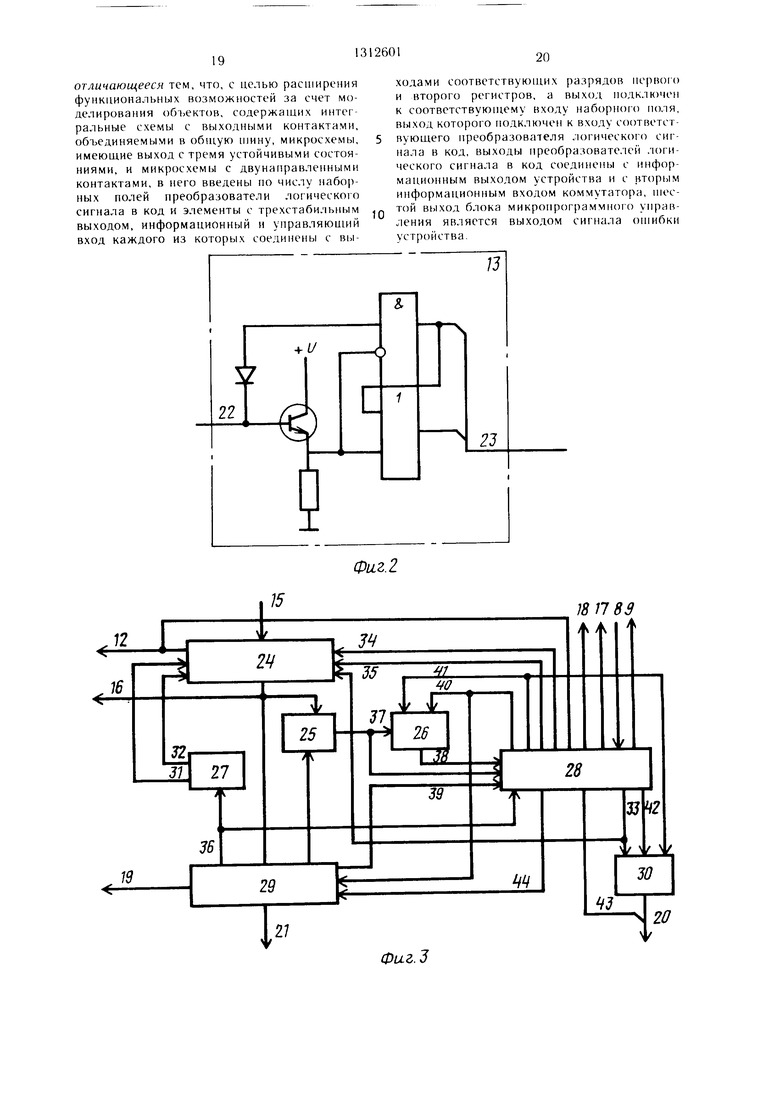

11,1 фи1. 1 представлена структу1)ная схема ycifioiic гна; на ijinr. 2 (|)у пкпиона.пьная схема u)eo6pa.ujiia 1е. 1Я логическог о сиг нала и код на базе гранзисторио-транзисгорной .югнкп. па ()П :5структурная схема

блока мик)опро1 раммно о управления; па фи. 4 структурная схема (fioiiMujxjua геля микрокоманд; на (finr Г) (}1ункииона. 1Ы1ая схема 3,ia ().имп1Я состояния; на ijini (i(f opMai комаады цепочки; на

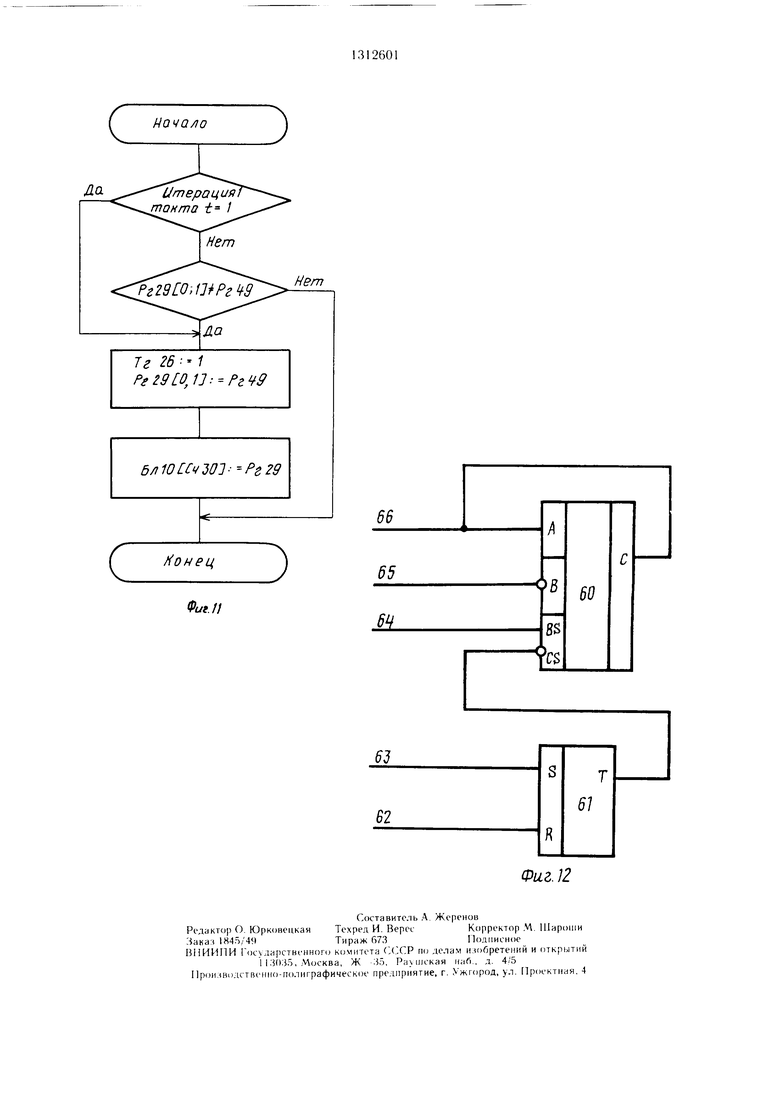

(j)iii. 7 б.ток-схема а.пгоритма, 11еализуе- мого блоком микропро раммпо о уп)ав.те- пия; на (JMir. 8 блок-схема алго|)итма опе- рапии настройки шчл л.вунанрав..|енных вы- иодов на П .фе.чачу; на i()Hr. 9 блок-схема а.поршма операции nacipoiiKii всех ocra.ii..- :и,1х ,|)дов моде. 1ируе 1П| о обт.ек1а; на i|)Hr. И) блок-схема алг() операции обрабогки команды, ()1П1СЫван)Пей выходной В,п ,о.1; на фпг. I I б, 1ок-с ема алгоритма onefiaiutn обрабогки )аз.и-Л11Т1-. команды; на фпг. Г2 схема Mo.te,in iyeMoi o в ка- чесгве прнмера niu}ipoBoio обьекта.

сгройстио 1 о.тержнт иаборпые по. Ш 1, iiH())opManiu)Hiii,ii ш.гход 2. KoMMyi arop , 5, ннформацио|шы11 ВХО.1 4, регисгр Г), нерек.чю- чаге, 11) () разрядов, б.юк 7 мик()о11 1ограммно- о уцрав, 1ения, вход ,S, в. Н. б.юк И) намя- ти, регис1р 11, В11гход i . |реобра.ова ie,H) 1И логической) сигна. 1а и код, -л 1емен 1Ы 14 с грехсгаби.чьным выхо.гом. С)язн 15 23,

с|)авнен11Я, тример I ti, .ченмфра го) 2/, ((ю)- ми)овате,|11, 28 мнкрок(., регнсгр 29 ко- Mafn, счетчик НО а.цх сон. свя.Н ,-i I 44, гене- |)а юр 4Г| гакговых iiMiiy.ibcoB, -j. ieMi. iiT 46 адержки, р(гисгр 47 адреса с, 1едук)пап1 м;|крокоманды, u .;i 4Н М()стоянной памяти, 6yijiepHi ui peiHcri) 49. ;, еменп 1 ИС.КЛ ЮЧ.Л- KMlU i- n;ill ill r,(i II .-,. ,|емен1Ы И 52 и 53 |.1еменг 11. 1И-П1 54, мv. ii) ин.и ксо 1Ы 55 и 5(i, io,ie 57 н;ч м:ака. iio.ie ,S кода команды nir,ir 59 адр1| а, itriHie., (})о 1 1нрова le.n. (И) I j Hi гер fi 1 . (Дс,1 ;и ti2 tit).

: ii .M i.iMa. iO .i мо.1е, 1И|)онания .(1|данно- : j iuu(4 Mi(j o ()б1 1 кта в сос 1 аве наб()1)Н()го 110,14 кч.иочаегся юг набор инте1()альных . ь.п I ciib ii исно. HI (уетея в обнекчс Под0

к, 1К)чение интегральных схем осу тест в.чяет- ся с помощью снспиа.чьпых колодок, выводы которых имени :,11 ктрический контакт с выводами микросхем и жестко соединены с соот- ветствующими входами 11реобра;и)вателей 13 и с выходами - лемептов 14. Каждый выход элемепта 14 может принимать как активное (логический «О, ,101ическая «1), так и пассивное (высокое сопрогив.ченис) состояние. В1)1ход : лемента 14 п|1инимаег состояние BbicoKoi o соцротив.чения, если на его управ- ,чяюн1ем входе присутствует низкий уровень (,Ц)гический «О), п,1и на инфо|)ма1и1онн()м входе присутствует соответствующий код состояния BhicoKoi o с()против;1еиия. В осталь5 иых с, 1учаях Н1,1ход :,1емента 14 принимает (. сосгояние в заниси мости от состояния инфо|)мационного входа. IlfMi :)том можно считагь, что когда выход : лемента 14 находится в сосгоянии высоко| о сонротив, 1е- ния, он яв.чяегся ;|огически o l к,1юченным

0 от наборного no,:m . i. е. последнее OKa;U)i- иаегся насгроенпым на передачу инфо()- мацни.

В б,1оке 1(( памяти |)а.змеп1акггся 1аб,.1ица нас1)()йкн вьпи)дов наб()рног() но,1Я и таб,и5 на соединений ин Г1Ч ра,тьных схем, описьша- юп1ая их реа, 1ьные связи в обьекге. Первая габ,:1ица с,|ужиг д;1Я пастройки каждого вглвода наборн(1Г() по,чя I па гг)ием иггформа- ппи, ее,ill соотвегс г г)ук)П1ИЙ ему вГ)Гги)Д иггтег - ральпог схемь яг(,1яегся г ходом, и,1и на irepe

Q дачу нн(|«)рма1г.г1и, ec.iri coo гнетствуюгпий UiUux i являемся выходом. Во tu()()oii ia6, irine каждая сг()ока задаег одну :1,чектрическую пегп, обьекга, соединяюн1уг) онреде,гегпгьге г()1ходг,1 (вг,гход| пп гег ра,чг, схем наборного 1го,чя 1 и, 11 EiHeinHHe вход1)Г (вход) 4

5 обГ)екта с всемгг входами игггег ра,чьньгх схем 1го,1я 1, яв,гяюгги1мися нагрузкой. Одна строка таблицы соединений представ,гяегся цепочкой комаггд, н|)и :1том снача,:га с,гедуют команды (команда), описывающие вг гход- 1ГЫС когпактьг (конгакт), да,чее с,1едует раз- де,1И ге,гглгая команда, а .затем команды, описыЕ аюгцие г(ходггг ге ко1ггакты. Каждая К1)манда (фиг . til содержиг гго,че 57 призггака нача,ча цеггочки, гго,че 58 кода командьг и Н();ге 59 адреса. Комаггда, онисГ)и)аюгпая

5 вьгвод, содержит в но.че 58 кода командг г тигг контакта, а в по,че 59 ег о адрес. 1- азде,1ительпая команда в ноле 58 со:и )жит прнзггак разде,гг1 ге,:гьггой к(.)мандьг, а в гго- ле 59 закодированное значение нредыду- гцего СОСГОЯГП1Я данггогч) узла (логический

0 « Ь, ;ю1Д1ческая «1 гг,чп высокое вьгходное согг|1ог ив.чение). В Г1ерги)й комаггде каждой ги почки в гг()ле 57 заггисГ)Гваегся «1, что яг,чяется прггзггаком нача,1а пеночки комаггд, в остальньгх командах УТОЙ цеггочкгг в rio,ie 57 (аггнсг:)Гва1 гся «О, fi гго.те 59 команды, опи5 сГ)1вагошей вг 1ходной вГ)Гвод, ука;и,1Еи1ется адрес, KOTopr.rii с, 1ужг1т для управления коммутатором 3 и определяет источник сгггггала (ги)Гход иптегра, схемг, и,1и один из

0

входов 4), а н алр сном iio. ie команды, описывающей входной вывод, адрес, который ис11оль:(уется для управления нереключате лем и определяет приемник еигна.па (вход интегральной схемы, с которым связан источник). Так как двунанравленные выводы могут работать в разные моменты времени как входные и как выходные, они должны быть также дважды описаны в пеночке при помощи соответствующих команд. При этом в таблице настройки выводов наборного ноля 1 они задаются только как выходные, так как блоком 7 сначала анализируются команды цепочки, описыващие выходные выводы, и в процессе анализа состояния двунаправленных выводов происходит их перенастройка на входной тин вывода в c/iy чае обнаружения того, что на двунанрав- ленном выводе наборного поля 1 отсугствус активное В1 1ходное состояние. Таблица настройки представляется как одна цепочка команд, онисываншх выводы вс(х типов наборного поля 1. Формат команды габлищ) настройки аналогичен (|)ормату команды таблицы соединений, однако поле 57 формата команды (нризнак начала цепочки) в таблице настройки не учнтывается. Прп 4том в данной таблице снача.ча описываются все двунаправленные выводы наборного ноля I затем все выходные выводы и, наконец, все входные выводы наборного ноля 1.

Устройство предпаз 1ачено д;1я iicn(xib- зования совместно с впенщими но спноще ПИЮ к нему средствами упран,1епия, например ЭВЛ, обеспечивающими автс)матизаппю процесса исследования моделируемого объекта па заданных последовательностях входных сигналов (тестах). При ЭВМ обеспечивает приложение тестов к входу 4 устройства, а также снятия п анализ выходных последовательностейреакций модели

на чти тесты с выхода 2 устройства. Вход 8 и выход 9 служат для внеищей синхронизации устройства от ЭВМ. Выход 12 выдает сигнал некорректности сочетания значений сигналов в одном уз.ме при обнаружении нескольких выходных вьжодов одной пеночки, паходящихся в активном состоянии в один моменг времени. Внутренняя синхронизация работы устройства обеснечиваегся формирователем 28, в узле 48 которого в виде мпкропрО1фамм записывается алгоритм работы устройства. Каждая микрокоманда содержит поле адреса следующей микрокоманды и поле микроопераций, которые являются выходами формировате.1Я 28. Входы формирователя 28 яв.тяются входами ус.то- вий, которые учитываются при ветв:1е1П1и хода выполнения микропрограммы. Этими условиями являются результат схемы сравнения, содержимое триггера, признак начала цепочки и код команды, находяще11ся в регистре 29 команд.

Вычисление логических состояний моделируемого обьекта в каждом такте нрик.ш5

5

дываемой к входу 4 нос, 1едовате, 1ьност11 сигналов осуп1ествляется методом И1е(1ацип Зейдс. 1Я. lloc, ie установки на входе 4 набора закодированных значений сигналов, соогветствующих онреде.тепному такту теста, ЭВМ задает па входе 8 сигнал, разрешаю- пи1Й нача. ю вычисления модели в этом такте (фиг. 7). При этом происходит начальная устаповка регистра 47 адреса следующей мик 1окоманды (фиг. 4), и с приходом нервого импульса па вход синхронизации узла 48 постоянпой памяти от генератора 45 но содержимому регистра 47 выбирается первая микрокоманда. С этого момента под воздействием блока 7 начинается цикл онераций соопитетвуюн1их первой итерации модели- Х)вапия обьекта в требуемом такте.

Г абога устройства (фпг, 7) пачипается с )1астройки выводов наборного ноля 1 на прием или па иередачу, д,-1я чег о в соответствии с nepBoii Ta6.:inneii, размещаемой в

0 блоке И) памяти, блок 7 через переключатель Г) разрядов устанавливает разряды регистра 1 1 в заданное состояние. При этом во время первой итерации нервого такта осу Н1еств,чяется настройка всех выводов наборного поля 1, а во в)емя последуюпшх птераппй то.тько двунаправленных выводов, так как настройка выводов других типов остается без изменени в процессе модели- рсшапия.

Поле микроопераций первой выбранной микрокоманды задает снгна,т на выходе 33 формнровате,-1Я 28, который обеспечивает сброс буферного pei HCTpa 49 (Pi 49) и установку счетчика 30 |(ч 30) в состояние, соот- ветствуюпн е начальному адресу (АД1 1) размещения таб, 1ппы настройкн в б, 1оке К) памяти (Бл10| (фн1 8). Адресная часть разрядов -iToii мпкрокомапд| 1 поступает на вхо.ч регистра 47, и с приходом импу„тьса от э,тем1 пта 4() .задержки происходит запись адреса с.тедуюи1ей микрокомапды. Вторая в|,1бранп;)я микрокоманда задает па выхо0 де 44 формирователя 28 спгна.т чтения команды из блока И) намяти но содержимому счетчика 30 адресов. Поскольку каждая команда размепк па в одном слове б,1ока 10 памяти, выборка команды требует одного обрашення. Эта команда принимается в ре5 гпстр 29 (Р- г29). Код данной команды на- стройкп вывода наборного но. 1Я с выхода 3(i регистра 29 команд ностунает па вход формирователя 28, задавая тем адрес следуюп1.ей микрокоманды. Нс,ти да1П1ая команда описывает настройку двуна11)авлен- пого В1 1вода, то по адресу, онреде.тяемому нолем 58 кода команды, находян1.ейся в регистре 29, в регистр 11 ( I ll) ири номощи сигнала па выходе 17 блока 7 по связи 16 через переключате, 1ь 6 записЬ)1вается содер5 жимое ciapniero |1азряда буферт)го регистра 49, равное в данный момент нулю. Пу,те- вое значение данного разряда регистра 11 постунает на унравляюн1ий вход соответст0

0

ВХ()Л111)К ИЫИО П,

.г. Iи К1)м;||1ЛМ II . тиГ) i)) опигынпег 1,1И()Д

BVinei o злемента 14 и усганавлии.ю i см и

выход г. i,4iCT() l)i.li.-(iK()l (j libl(i;UH) C(i

против. И НИЯ, ()C ineci в,:1яя тем самым .ioin- ческое oi клкшешн да1111()1Ч) в1.1Х()да :;i,i. Mcn- та 14 от соответствующего вывода наборного .1Я 1, чго и является насгр(я1кой соогветст- нуюшего Bi.iii(j;ia наборного поля 1 на нере- дачу. (.:|едук)Н1ая мнкрокоманда задает сш иал на выходе 42 формирователя 28 н увеличивает тем самым содержимое счет- чнка iiO адресов на единицу. Ла,1ее но новому содержимому счетчика 30 ()в счигыва- егся с.те.чукиная команда и. габлиЩ) настройки и процесс повторяется, пока не будет осун1ест1(лсна itacr)oiiKa всех двунанравлен- 11ьг Bi,iB)40ii передачу.

данная итерация (ijmr. 7) яв. 1яется первой пт( рацией nejiiioio так1а, ю пеобхо днмо также насгроигь осга. 1и,1воды iia6op;ioi4i по.чя I, i. е ()С1алы1ые В1,1ходп1)1е вывод1)1, на пере;1ач. па npncvi ин((и)рмапнн. nacTpoiiKH u(inr. набо|)И()1Ч) ноля как выходц(И1, ю ныпол- пяется апал)1Л1чпая пропс-дура настройкп вывода па передачу, как и в случае дву- папраилеппого В1))да lu-. in комапда п;( таб- .1ПЦЫ iiac ipoiiKn описывае naocfinofo по.14 1 как входной, K.I для сначала необходимо cianoBnib бу1(н ()пьц) perncrji 49 1 сл1ПП1Ч|1(11,- 1 ос 1Ч)ЯПИ1 (Гг4):11), а (атем по , ()Ц|Н де.1У1емому по,-1ем ;VJ команд., на 40 1Я цеЙ1 я в регпсг е 29 команд, в регисгр II ча 1исагь по свя in Hi содержимое гтар- niero ючряда oytju iiiioro peiiic ipa 44 при помощи (.,ia па вилходе 17 б, 1ока 7. 1:ди- ппчпое «пачепие даипш о разряда нлт1С 1 ра 1 iiociynac T па управ,1як)П1иГ| вход соот клс гвуюним о лемепта 14 и перек.лючает 1ЧЧ выхоч в акгивпое c(JCT()янпe, насграивая гем самым соогветствующпи вывод наборного по.:|я 1 па ирпем ппфо)мац,11и.

После настройки |ребуемых выводов д.тя данпой )Пии ycTpoiicnut (ij n.. 71 прпсгупает непосредс i ве)1но к :irany моде,1и рования. ;1,чя эгого {|)ормир(1ва1Ч , 1Ь 2(S ча- даег на вь;ходе 4 снгиал, ко юрый обесми-- MHiuieT сброс ipHiiepa 2ti ( |2)) п установку счетчика 30 адресов в сосгоянпс, соотвечст- иуюшее нача.чьному размещения (,Л;1,Р2) таб,:1ппы соединепия в б,ч()ке К) памяги. 11ос,е 4ioi() па выходе 44 фо)мп- рова1 е,;1я 2Н |;оявляегся сигна,ч чтения ко- манд1.1 из б,1ока 10 памяти по содержимому сче1 чика 30 ад)есов. .-)та комапда прини- ма(гся в perncip 2.) команд. Код комаид1 1 с иыхо.ча ЗС) 29 цос1уиа1.л па вход команд форми 1ователя 28, а .значеппе при- .пака нача.ча исночкн поступает с выхода 39 п;; вход нриип .ка )овате,чя 28, зада- ;;: leM ,1м ус,овия вегв.тения для вы- I . p.:: . 1с.1, юи;-, ; микрокоманды. 1.с,1и данная Kiiv.iiLui яв,тяегся первой комапдой це- ;:;: ки (|1ача.1ом пепочки), то на выходе 34 i;; iii. iMi 11 .| сигна. ч 1ановки Ei единичное

5

0

5

0

5

0

5

0

5

сосчоянпе бу(()ерпого )егпстра 49. ;1,а, 1ьней- ;пая o6pii6()TKa комапд) происходит R за- висимости от ее типа.

Гл лп данпая комапда описывает вывод наборного ноля I как выходной д.тя данной цепи соединения, го при (хллцествля- ются следующие действия (фиг. 10). .Адресное цо,че 59 комаид1 1, находящейся в регистре 29 (выход 19 б,:|()ка 7), воздействует па управляющий вход коммутатора ,3, который выби)ает заданное ътп.м но.чем закодированное соответствующим преобразовате- ,1ем 13 з}|ачение адресуемого В1)1вода одной из ингег11а,1ьпых схем (и,1и вход 4) и передает его состоянпе по связп 15 па информа- пио1пп |й вход у ,ча 24 оиреде,чения состояния. Кодироваиие состояний пропзводтся преоб- разовате.чем 13 (фиг. 2) при noMonui двух раз)яд()в с,1едук)П1пм обра.(ом; ,1огический «О 00, .югпческая «1 1)1, высокое с())гив.че11ие («Иеоп1.1еде,1епо)1 1.

Закодированное гакпм образом состояпие iKjcryiiacT па первые ipyninji ппформапион- ных входов у,:1ементов И(.К, 11ОЧ.ЛК) И, 111- |{; 50 и 51 и з,:|ементо11 И 52 и 53. 1 лми данная команда яв,чяется нача.чом пепочки, и,ми иредиа-ствующие комапды даппой цепочкп описывали двунаправ.ченные выводы и,И выводы (. тремя состояниями, которые иаходи. 1ИС1 в момент в|)емепи

в СОСТОЯНИП BI)ICOKOi() ВЬГХОДПОГО COHjJOTnBлепия, тс.) иа вгорые группы входов .leMtni- г()в 50 53 поступают едиппчп1 1е .значепия с вьгчода буферного lerncrpa 49. В этом сосгояиии независимо от гина в1)Гходного вывода закодированное значение с выхо.та му,тьги(пексора 5() без п.зменеппй поступает на И11формациони)|й вход буферн(мч) регистра 49. (,чеду|)ии1Я выбрап |ая микрокоманда задает па выходе 35 формировате.чя спнхро- нпзирук)Н1ИЙ сп1Ч1а,т, но кото|К)му происходит запись закодирО и1Нно1Ч) значения состоя1П1Я в буферн1 1Й (нм истр 49.

Гд ли даииая комаида также О11ис1)1вает выво.т наборп()() ПО.1Я 1 как выходной, но она уже не яв.чяек Я пача. юм шчючкп (т. е. .чапная цеш; соединений содс-ржит неско.чько выходных выводов и11Г(.ч ральи1)Гх схем), то новое зпачепие закодироваппого сосгояппя вывода по связи 15 посгутьчет iia niii)opMa- циоппый вход уз,ча 24, с учегом состоянпя предыдупи1Х выводов даипой пени соединений и их типа осуществляется корректировка значения состояпия в дапный момент времени с иос,1еду1О1пим занесением скорректированного значения в буферный регистр 49. Г.сли ана.чи.зируемая комапда опис1 П ает выходпой вывод, обч едппяемый по И, то с выхода 36 регисгра 29 К(1мапд па вход деп1ифратора 27 поступает соответствующий код команды, в резу,тьтате чего па выходе 32 Д1чпи({)ра гора появляется ,чо1 ическая «1, которая поступает па вход выбора канала мультиплексора 56, разреитя тем самым выдавать на вьгход мультиплексора 56 значение, полученное в результате 110раз1)яднои логической кон1)Юнкции состояний текущего и предыдущих выходне)1х выводов данной цепи. Эта операция л()гической конт юнкцми осуществляется на элементах 52 и 53. Если анализируемая команда описывает выходной контакт другого типа, то на выходе 32 дешифратора 27 присутствует логический «О, и на выход мультиплексора 5(i поступи ют значения с выходов элементов 50 и 51.

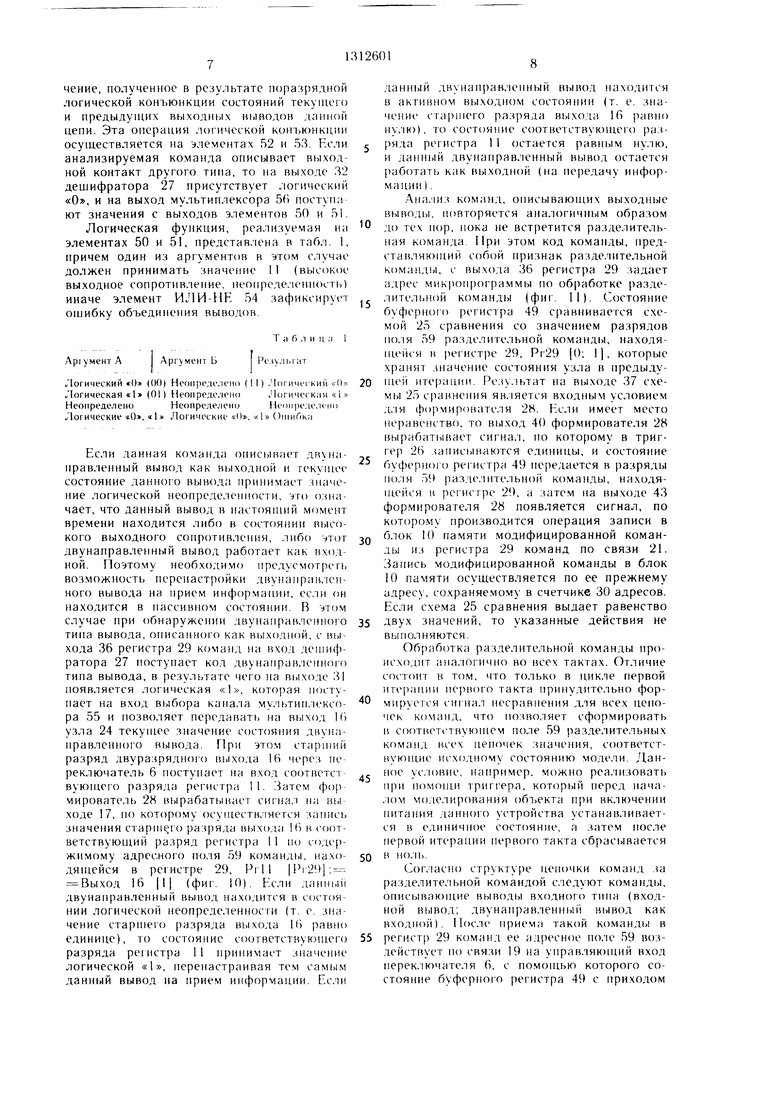

Логическая функция, реализуемая

элементах 50 и 51, представлена в табл. 1, причем один из аргументов в этом случае должен принимать значение II (высокое выходное сопротивление, неопределенность) иначе элемент ИЛИ-НН 54 зафиксирует ошибку объединения выводов.

Лр1 умент А

Аргумент Б

Т ii б л и на 1 14.1ьгат

Чогический «О (00) Ноопцедсмсии (II) Jiorn iei KMii «О 20 Логическая « 1 (01) Неопреде. юноЛогичоскпя « 1

Неоп редели еноНеопределеноНеопрелолсно

Логические «О, «I Логические «О, «1 OMIHOK;)

Если данная команда описывает

правленный вывод как выходной и гскупц е состояние данного вывода принимает значение логической неопределенности, это означает, что данный вывод в настоящий момент времени находится либо в состоянии высокого выходного сопротивлепия, либо этот двунаправленный вывод работает как входной. Поэтому необходимо предусмот|1сть возможность перенастройки двуиаира пленного вывода на прием информации, если он находится в нассивпом состоянии. В этом случае при обнаружении двунаправленного типа вывода, онисанного как выходной, с выхода 36 регистра 29 команд на вход дешифратора 27 постунает код двунаправлеп)1ого типа вывода, в результате чего на выхсхче ,41 появляется логическая «1, поступает на вход выбора кана, 1а мультинлексо- ра 55 и позволяет передавать на выход Hi узла 24 текущее значепие состояпия двуна- нравленного вывода. При этом старншй разряд двуразрядного выхода 1Н через переключатель 6 поступает на вход соответст вуюплего разряда регистра 11. Затем фор мирователь 28 вырабатывает сигнал на выходе 17, по которому осуществляется запись значения старн1его разряда вь11хода И) в оот- ветствующий разряд регистра I 1 по содержимому адрес.ного поля 59 команды, нахо- дяшейся в регистре 29, Pill |Pi29 ; Вы ход 16 |1| (фиг. 10). Если данны1| двунаправленный вывод находится в состоянии логической неопреде. 1енносги (т. е. значение старшего разряда выхода ИЗ равно единице), то состояние соответствующего разряда регистра 1 1 принимает значение логической «1, перенастраивая тем самым данный вывод иа прием информации. Если

0

0

5

0 5 , 0 5

данный двунанрав.ченный вывод находится в активном выходном состоянии (т. е. значение старшего разряда выхода 16 равно ну. 1Ю), то состояние соответствующего разряда регистра 1 1 остается равн1)1м нулю, и данный двунаправленный вывод остается работать как выходной (на передачу информации ).

.Анализ команд, описывающих выходные выводы, повторяется аналогичным образом до тех пор, пока не встретится разделительная команда. При этом код команды, представляющий собой признак разде/1птельной к()ма11Д1 1, с выхода 36 регистра 29 задает адрес микропрограммы по обработке разделительной команды (фиг. II). Состояние буферно1 о регистра 49 сравнивается схемой 25 сравнения со значением разрядов поля 59 разделите.тьной команды, находя- пичн я в регистре 29, Рг29 (0: 1), которые хранят значение состояния узла в предыдущей итерации. Резу.1ьтат на выходе 37 схемы 25 сравнения является входным условием Д.ТЯ (формирователя 28. Если имеет место неравенство, то выход 40 формирователя 28 вырабатывает сигна,, но кото)ому в триггер 26 записываются единицы, и состояние буферного регистра 49 передается в разряды но.пя 59 разделительно команды, находящейся и регистре 29, а затем на выходе 43 формирователя 28 появляется сигнал, по которому производится операция записи в блок 10 памяти модифицированной команды из регистра 29 команд по связи 21. Запись модифицированной команды в блок 10 памяти осуществляется по ее прежнему адресу, сохраняемому в счетчике 30 адресов. Если схема 25 сравнения выдает равенство двух значений, то указанные действия не выполняются.

Обработка разделительной команды происходит ана, 1огично во всех тактах. Отличие состоит в том, что только в цикле первой итерации первого такта принудительно фор- мируегся с-и1 нал несравнения для всех цегю- чек команд, что позволяет сформировать в соответс твуюп1ем поле 59 разделительных команд всех гепочек значения, соответст- вуюнще исходному состоянию модели. Данное ус. ювне, например, можно реа,чизовать п|1и помощи трип ера, который перед нача- ;ioM мо.телирования об1)екта при включении питания данного устройства устанавливается в единичное состояние, а затем после нервой итерации первого такта сбрасывается в ноль.

Согласно структуре цепочки команд за разделите.чьной командой следуют команды, описываюп1ие выводы входного типа (входной В1)1вод; двунаправленны вывод как входной). После приема такой команды в регистр 29 команд ее адресное ноле 59 воздействует по связи 19 на управляющий вход перек.1ючателя 6, с помопхью которого состояние буферного регистра 49 с приходом

сигнала синхронизации с выхода 18 форми- ронателя 28 передастся по связи 16 в соответствующие )азряды регистра 5 (Рг5), выходы которых соединены с информацион- iHjiM входом определенного элемента 14, выходом непосредственно соединенного с вы- иодом наборного поля 1, который задан ад- ()есн1)1м полем команды (. 7). При этом гак как адресуемый входной вывод наборного поля 1 обязан быть настроен на прием информации, то на унравляюшем входе соот- вегствуюпгего э;1емента 14 присутствует ло- 1 ическая «1, в результате чего выход элемента 14 г.ринимает состояние, закодированное двумя разрядами регистра 5. В соответствии с новым состоянием входа интег- 1а.1ьнаи схема изменяет свое внутреннее состояние или/и выходные сигналы. Анало- 1ИЧ1К н1Х)изводятся выборка последующих команд дапно11 нецочки и изменение состоя- HHii остальных входов интегральных схем, связанных (дной цепью.

Данный процесс повторяется д.ля всех пеночек команд, осупк ствляя тем самым обмен информацпей между входами и выходами И1ггегральных схем цифрового объекта. 11о окончании обработки нос. 1едней команды последней пеночки цикл операций устрой- сгва, ()тносяп1ийся к данпой итерации моделирования обьекта в данном такте, заканчивается Формировате.П) 28 иереходит к анализу (фиг. 7) сосгояния Т1)иггера 26, выход 38 KOTOp(jro является входом ус,товпя для формирова 1 еля 28.

Если состояние хотя бы одпой цепи выводов изменилось в резу;1ьгаге любой итерации {г. е. оказалось отличн1)ГМ от состояния 11редыдун1ей итерации, указанно1Ч) в разрядах поля 59 )азде.чительно11 ко.манды), то три1Т ер 2t) находится в состоянии «1. В этом случае формировате.пь 28 начинает новый цикл работы, соогветсгвуюнгий c,:ie- дующей итерации. Г.сли состояние ни одной из пеней выводов, в цикле и|)едыдун1ей иле- рации не изменилось (это озиачает, что иро- цесс установления 1К)В(го состояния модели н такте завер пился), то триггер 26 находится в сосгоянии «О, что является условием для того, чгобы формирователь 28 )або- гал на выходе 9 устройства сигна;, свиде- 1ел1 ствук11ций оС) окончании моделирования в определенном такте, и остановил работу устройства до но, 1учения нового сигнала нача;1а следующего 1акта на входе 8. Ре- Зумыатом моде.чирования ус1ройства явля- Ю и я значения, по,1ученП1)1е па выходе 2.

Определение некорректности сочегаиия .(начепий сигналов на выводах обьекта, под- |:. 1юченных к одному узлу, ()снс)вывается i;:i гом факте, что в один момент времени - |,|пом зл; лпн1Ь один выходной вьпюд может находиться в активном . югическом .ос11)янии (кроме случая об ьединениу выво- ,|)В с огкрытым коллекгором в одном узле).

Поскольку коды активных логических сосгоянии имеют в старн1ем разряде нули, то для обнаружения иодобных недопустимых ситуаций используется элемент ИЛИ-НЕ 54,

выход которого является выходом 12 устройства, информирующим ЭВМ о том, что в узле два или более выходных вывода находятся в активном логическом состоянии.

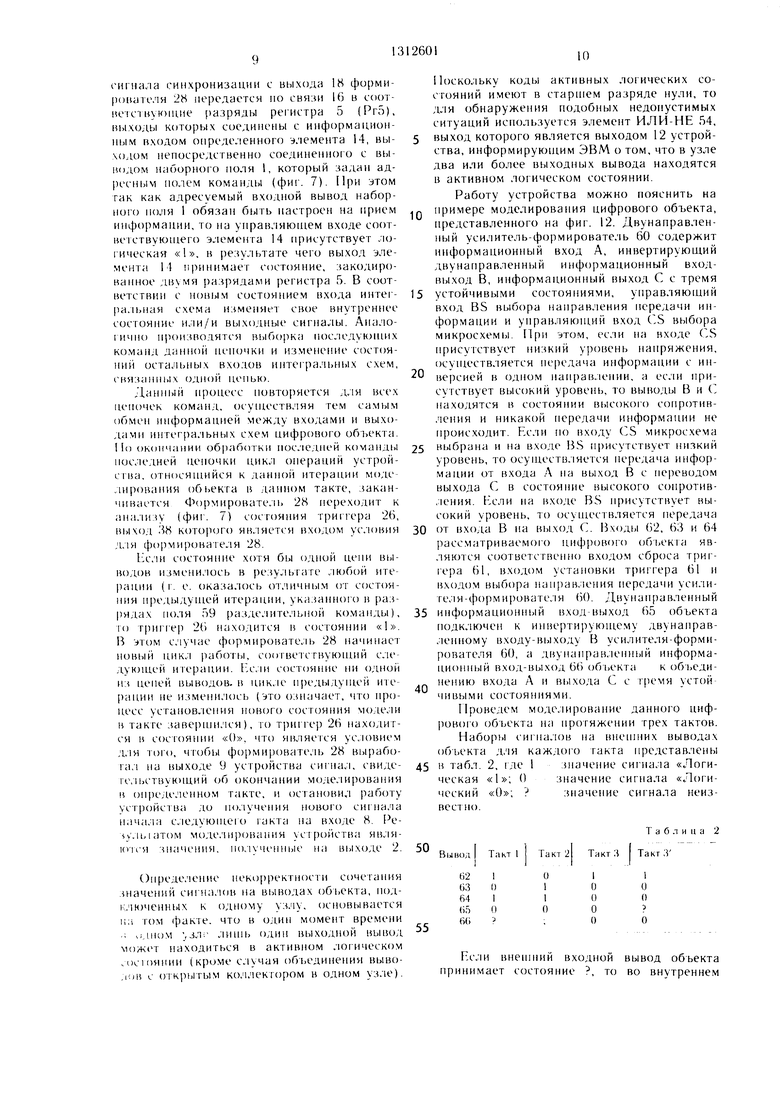

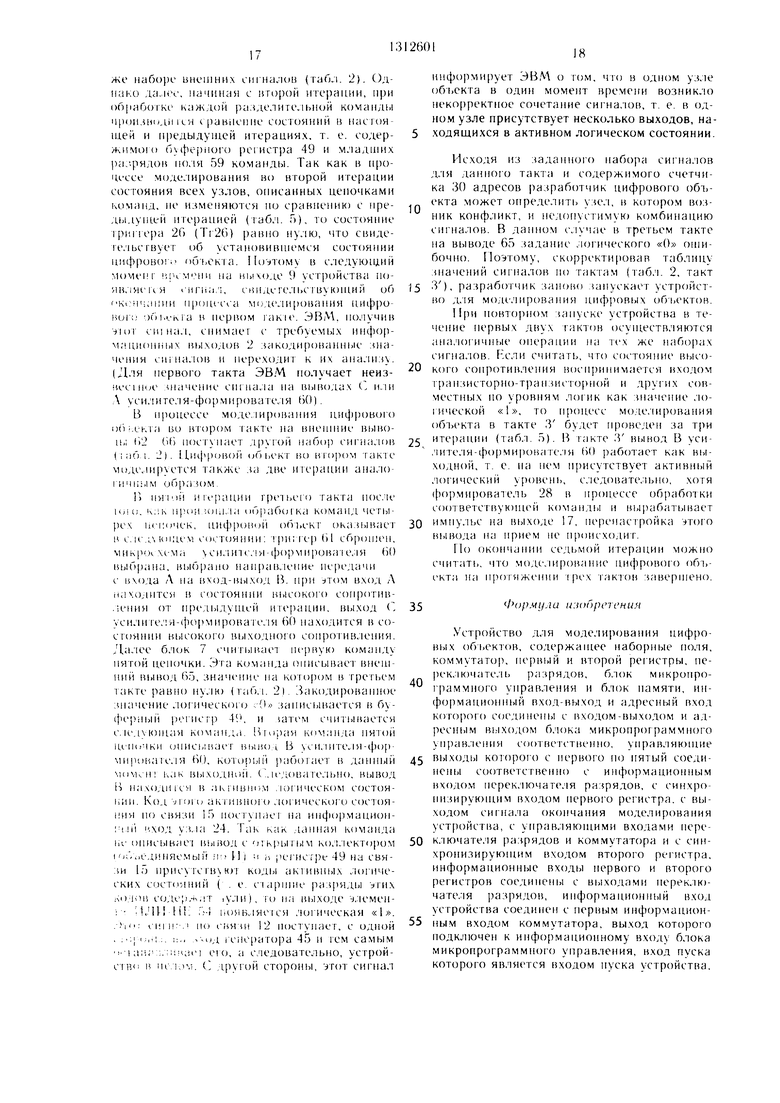

Работу устройства можно пояснить на

Г примере моделирования цифрового объекта, представленного на фиг. 12. Двунаправленный усилитель-формирователь 60 содержит информационный вход А, инвертирующий двунаправленный информационный вход- выход В, информационный выход С с тремя

5 устойчивыми состояниями, управляющий вход BS выбора направления иередачи ип- формации и управляющий вход CS выбора микросхемы. При этом, если па входе CS присутствует низкий уровень нанряжения, осунк ствляется передача информации с ин0

версией в судном наи)авлении, а если присутствует высокий уровень, то выводы В и С находятся в состоянии BiiicoKoro сопротивления и никакой иередачи информации не происходит. Рл ли по входу CS микросхема

5 выбрана и на входе BS присутствует низкий уровень, то осун1еств,тяется передача информации от входа .Л на выход В с нереводс м выхода С в состоя|те высокого сопротив- .пения. Нсли иа входе BS ирисутствует высокий уровень. К) осунк ствляется передача

0 от входа В на выход С. Вход1,1 62, 63 и 64 рассматриваемого цифрового об ьекга яв- , 1ЯК)тся соответственно входом сброса триг- 1 ера 61, входом установки триггера 61 и входом выбора направления нередачи усилите; я-формирователя (К). Двунанравленпый

5 информациониый вход-выход 65 объекта подк. 1ючен к ипвертируюн1,ему двунаправленному входу-выходу В усилителя-формирователя 60, а двуиаправ,:|ен)1ый информационный вход-выход 66 обьекта к об ьеди- нению входа А и В1 1хода С с т)емя устой ч и вы ми состояниями.

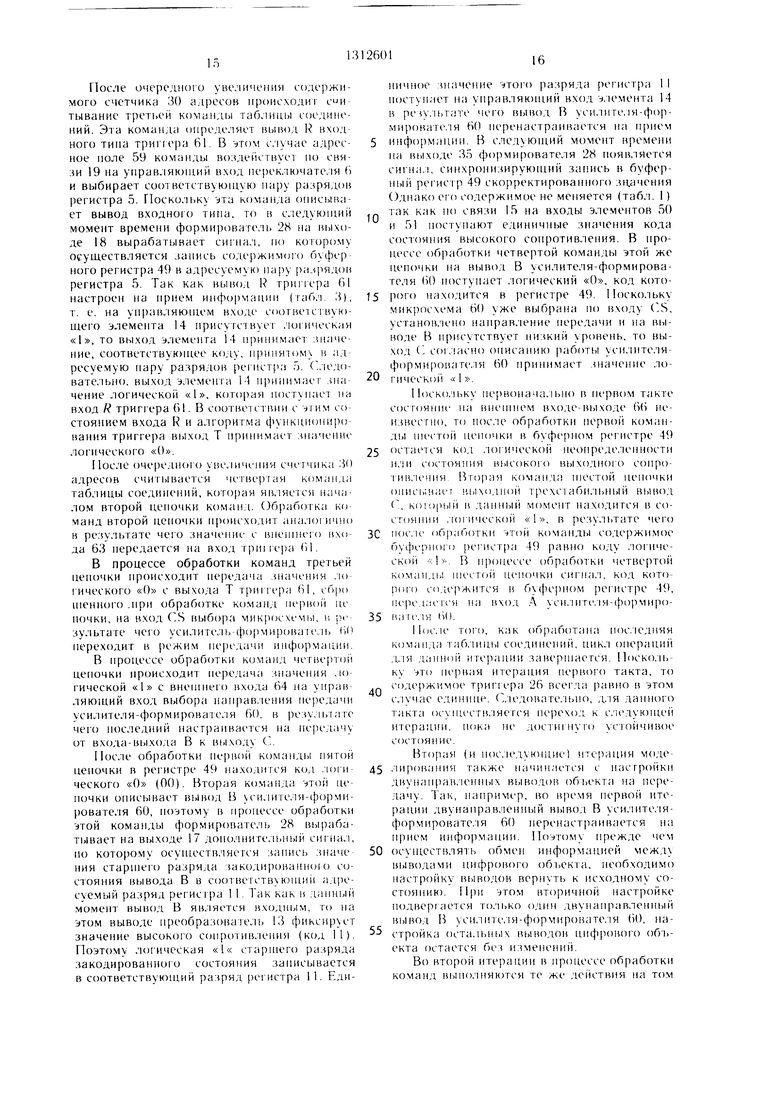

Проведем моде.мирование данно1 0 цифрового обьекта на нротяжении трех тактов. Наборы сигиа,:1ов на внешних выводах объекта для каждого такта представлены

5 ч табл. 2, где 1 значение сигнала «Логическая О значение сигиала «Логическийвест но.

зиачение сигнала неизТаблица 2

50

Вывод Такт 1 Такт 2 Такт Л Такт 3

62 (i3 64 ()5 6(1

0I1

1ОО 1ОО ОО ;ОО

Р,С,ПИ

внен1нии входной

принимает состояние ,

то

представлении устроистии -по (. огтояиц. ии- 1ер11ретир ется как гостоянис Н1)1С()К()Г1) сопротивлении ( 1(.()П Н ;име11о).

Перед моде. и напорное 110,le 1, иып(),:111енное и виде разьемиых КО.1ОДОК, встав. иетси тог набор ингеграль ных схем, Koropi) онреде,1Яег состав luuji- ровсяч) ()6Т)екта (vniKpocxt Miii (ill и (il). 11)и VTOM входу 4 и каждому В111воду наборного поли 1 соответствует свой ннутренни11 адрес, в результате чего каждый выво.1 luufipoBoro об ьекта также имеет свой ад)ес.

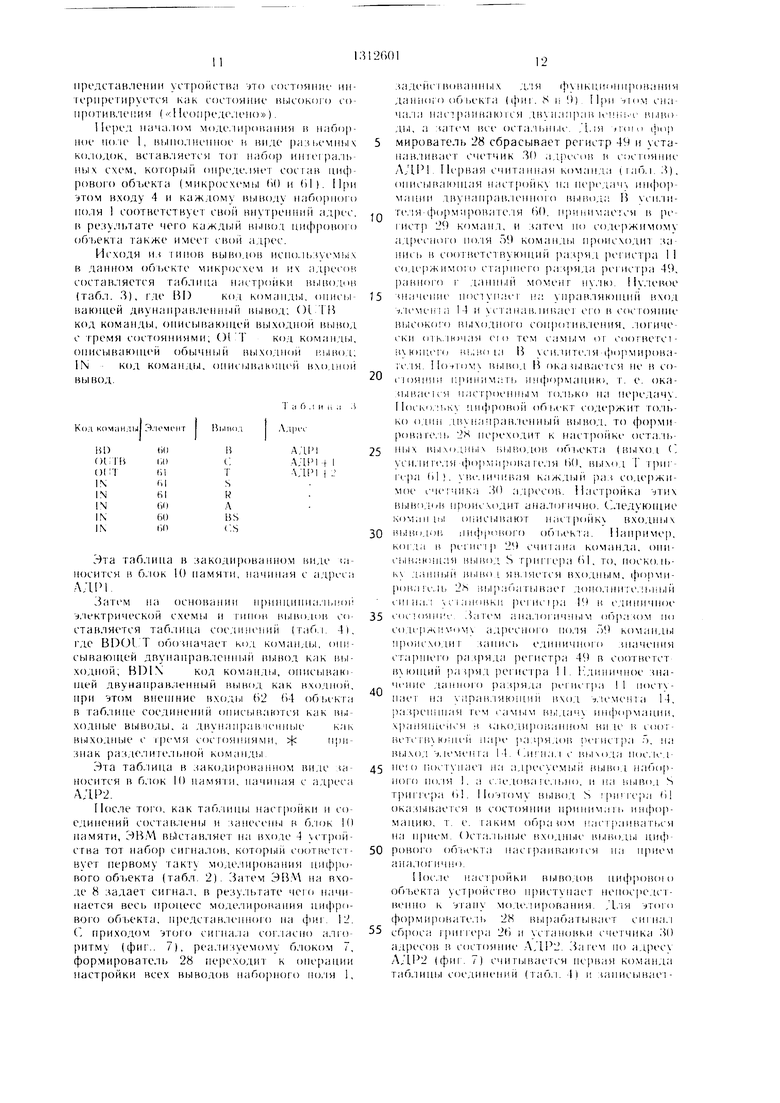

Исходя из гииоЕ выводов исно.1ьзуемы в данном обьекге мнкрос хем и их ад Н Сов составляется таб.тина наст)о11кн В1, (табл. .3), где BI) код команд1 1. описывающей двунан1Швленн1.|Г1 В1)1вод; ()1 код команды, онисыр ак)Н1ей выходной ввшод с гремя состояниями; ()( Т код команд| 1, ()11исывак) обычн)1Й u lxoдн JЙ 1.ывод; INкод кома}1ды. онисыв.шннсй входной

ВЬ)ПК)Д.

Кол К(1 1ПНЛы| З. ЮМОНТ

B

(id

1,0

111 il 61 ()0 60 tiO

И

( Т

s

R Л BS

r.s

АДР A. U l-t I

I

Эта таб.;1ииа в закодирова |ном виде la- носитен в б.:1ок 10 памяти, начиная с адреса

..

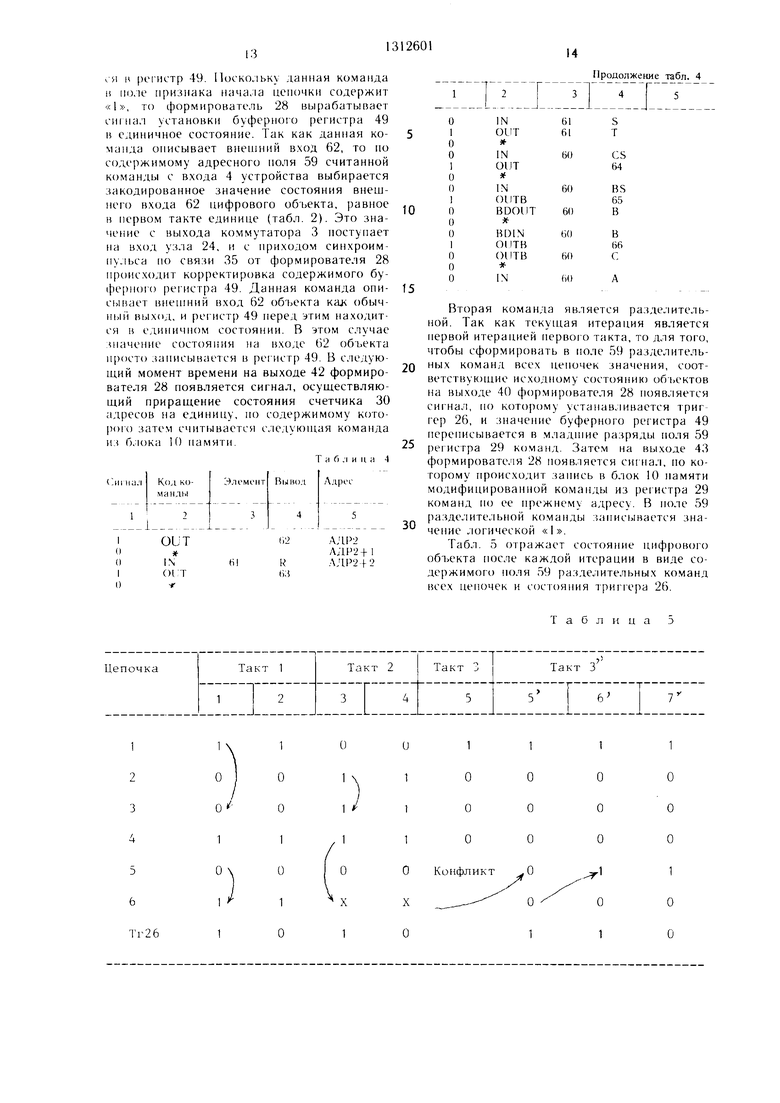

Затем на основании нринциниа. н.мой :. 1ектрической схемы и гипон выводов составляется таб,1ица сосдин1М1И11 (табл. 4i, где BDOI Т обозначает код команд, они- сывающей двуиан11авленн1 1Й вывод как ходной, BDl. код команд,, оннс1,1вак1 пи й двунан()авленный вывод как входной, нри iTOM внеи1ние вхо;1Ы ()2 ()4 обы кга в габ.тине соединений онис1,1 аются как iii,i- ходные В1 1воды. а двуна 1()а1(ленн1 1е как выходные с гремя сое гояннями, : ii|iiiзнак раздел и ге.тьной

Эта таб.тина в закоди|)ованном виде ui- носнтся в блок И) намяги, начиная с адреса ЛЛР2.

После того, как таб,-|ицы насгройки и со- едииений состав.тены и занесе1н,1 в б.юк 10 намяти, ЭВМ BijIcTaB. meT на входе 4 ства тот набор сигналов, который COOTBCTCI- вует первому такту моде.ирования uH(f)po- вого объекта (табл. 2). Затем . на входе 8 задает сигна:, в резу.тьтате чек) начинается весь нронесс моделирования ци(()ро- вого обьекта, нредстав.и нного иа (Jutr. 12. С ириходом :1Т(Я() CHi Ha.ia coi .iacHO ал1()- ритму (фиг .. 7), реа,1изуе 1ому б.чоком 7, формирователь 28 переходит к операции настройки всех выводов наборного 11о. 1я 1,

0

5

0

5

0

5

0

5

5

зад1 йс I вованн1 1х д.ч я (jiyHKii,h iHHpoBaHHvi данного обьекта (q Hi. 8 п 0) 1)и юм сна- ча. 1а наст paimaio гея двунамрав iv-niii-T ni.ufo- ды, а затем все ocTa.,ie. , 1.1Я лчмч ijiop мирователь 28 сбрасывает регистр 49 и уста- нав. счетчик . адресов в сосюяни ЛЛР1. Первая считанн 1Я коман.ча (ia6.i. Л), онис1,1ва1он1ая наст|И)11ку на нер1мач 1 нн(|)ор- мации дву HaiipaB.ieHHoro выво,;:; В си. 1И- те. 1Я-ф(1рм .1)овате.1Я ()(). iijiHiHiMae icvi в ре- 29 команд, и но сод1-ржимому ад)есного HO. IH 59 команды 11(1онсходит запись в С001 ветсп ByKiHuiii разряд pei ис1|)а 1 1 содержимого старн1его тазряда регистра 49, ра 1ного г данньи моменг ну. Ж). Пу.тевое значение ноет м..е |- на унрав. 1ЯК)Н1И11 вход i.ieMeii I ;i 14 и устанав. 1ивае1 ei o в сосгояние высокого выходного со|||)отив.1ения, .югиче- скн отк.1Н)чач CIO тем самым ог соогветс - iUKHiuM o Н1,:ио i;i В уси.1Ите. 1Я-4 ормирова- 1е.1Я. 11о-)То вывод ока ываен Я не в со- сюянии принимап, 11Н())о)маник), т. е. оказываемся настроенным го. 1ько на нередачу. locK i. м.к lUKJipoBoii обьект содержит то.чь- ко однн . 1енны(1 вывод, то фо1пп1 loBaixMb 2Х 11С)еходит к HaeTpoiiKi оста.ть- ны .1пы )дов обьекта ( С, уси.1И1 е. 1Я-фо);ирова Г1 . 1Я lid, выход Т триг- ri. 111). 1и .1ичивая каждый jia.i мое счегчик;) . 50 ад(1есов. Настройка 1 ыводо1 происходит аналогично. (Следующие KoM.iHUii о1 исывак)г H;ici|KiiiK вх()Д111,1х 1 ыводов |1иф|1оио|-о обьекта. Панрнмер, ко|да в penicip 29 счи1ана К1)манда, оии- сываюшля S Т |1иггера dl, то, иосколь- к данный libiBOi яв.1Я1. тся входным, формн- loBare.ib 2н iiijipaoaTbiBiier . юно.чннтс.,iii CHI на. i i ;ni HiKii perncipa 19 в единичное сосИ1ЯН1 г Затем ана. 1О| Ичным образом но сод1 |1Ж11 1о адресного Н(). 1я .)9 команды 1(1оИ1. ходи г занись единичного .(начсния CTapiHci o pa.(ряда регист 1а 49 в соответст в loHuni pa ряд peiiicTpa 11. 1 днничное значение данного разряда peincrpa 11 носту- Haei на ч прав. 1як)1нин вход .-leMCHia 14, ра. самым выдачч ин|})ормацин, хранящейся ;з (акоди 1О ,анном ни le в соог- ветс г Kjiiieii iia(H ра.рядов регистра .), на В1,1ход лемен1 а 14. (лильч. с iu,iM). ui нос.км- не о иостунае 1ьч адре сус мьп) вывод наборного но. 1Я 1. а с. к-дова ге. 1ЬН1. и на ььигод S трнгге)а Г. вывод S (И оказывае1ся в состоянии принимать инфор- маник), т. е. гаким обра ом пас i |1анваться на нрнем. ()ста. входные выводь циф- 0 рового o6i,i-KTa нас i ранваю i ся на нрнем ана. 101Л1чно.

locMC насгройки выводов цифровою об ьекта уст|)ой(. гво приступает неносредстВеННО к :)ГаНу моде-. ИрОВаНИЯ. Л.1Я :)ТО| о

($)0)мировате. 1ь 28 ырабат ывает сигна.: сброса rpniiepa 2Г) и усгановкн счегчика .40 ад)есов в состоянн. .. 3aieM но адресх ЛЛР2 (фи1. 7) счигы| аегся первая команда таблицы соедин1Ч1И.й (таб.1. 1) и занис1 1вае1 Продолжение табл. 4

После очередного увеличения содержимого счетчика 30 адресов происходи г тывание третьей к()манд)1 табдиць} соединений. Эта команда определяет вывод R входного типа триггера 61. В этом случае адресное поле 59 команды воздейстЕП ет но свя- 19 на у11рав;|як)|ций вход 11ерек;1ючате;1я 6 и выбирает соответствующую пару разрядов регистра 5. Поскольку эта команда описывает вывод входного типа, то в с.1едуюни1Й момент времени формирователь 28 на выходе 18 вырабатывает сигна., по которому осугцествляется занись с()л,ержим(1го буфер ного регистра 49 в адресуемую пару разрядов регистра 5. Так как вывод R три пера 61 настроен на прием информании (табл. 3), т. е. на управляющем входе соответствующего элемента 14 ирисугствуег .логическая «1, то выход злемента 14 принимает значение, соответствующее коду, нрипяюмч и адресуемую пару разрядов peiMicTpa 5. (..тедо- вате:1ьно, выход элемента 1-1 принимает .5иа- чение логической «1. которая поступает на вход К трип ера 61. В соответст вни с тим состоянием входа R и алгоритма функциопи)- вания триггера выход Т принимает значение ло1 ического «О.

После оче)едного увеличения счегчика 30 адресов считывается четвертая команда таблицы соединений, кот(:))ая является началом второй пеночки команд. Обрабогка ко манд второй цепочки происходит аналогично в ре.зультате чего значение с внеп1пего входа 63 передается на вход трип ера 61.

В процессе обработки команд третьей пеночки происходит передача значения .ю- гического «О с выхода Т триггера 61, сбро щенного Л1ри обработке команд nepBoii пс почки, на вход CS выбора микросхемы, и зультате чего усилпте;1ь-({10|1мир(.ль fii) переходит в режим передачи информации.

В процессе обработки команд четве|П()1( цепочки происходит передача значения логической «1 с внешнего входа 64 на управляющий вход выбора направ, 1ения передачи усилителя-формировате. 1я 60. в резулыатт чего носледний насг)аивается на нс)едачу от вх(да-вь1хода В к вьгходу (..

После обработки HepBoii команды пятой цепочки в регистре 49 находится код .логического «О (00). Вторая команда :1той цепочки описывает вывод В силителя-(})орми- рователя 60, поэтому в пропессе обработки этой команды формирователь 28 вырабатывает на выходе 17 донолните. сигнал, по которому осуществляегся за1П1сь значе ния старшего разряда закодированною состояния вывода В в COOT вегствуюпиш ад)е- суемый разряд регисгра 1 1. Так как в данный мо.мент вывод В яв, 1яется входным, I o на этом выводе нреобразователь 13 фиксирует значение высокого сопротивления (код И). Поэтому лог ическая «1« старн1его разряда закодированною состояния записывается в соответствующий разряд регистра И. Еди0

ничное значение этого разряда pei ncTpa 1 I поступает па управляющий вход э.пемента 14 в резу.тьтате чего вывод В усилите,1Я-фор- мирователя 60 11ерепастрап ается на прием инф())мации. В следующий момент времени па выходе 35 формирователя 28 появляется си|-нал, синхронизирующий запись в буферный рег истр 49 ско 1ректпрованпого значения Однако ei o содержимое не меняется (таб,ч. 1) так как по связи 15 на входы элементов 50 и 51 поступают единичные значения кода сосюяния высоког о сопротивления. В нро- цессе обработки четвертой команды этой же цепочки на вывод В усилителя-формирователя ()0 ноступает логический «О, код кото5 рого находится в регистре 49. Поскольку микросхема 60 уже выбрана по (-S, установлено панравление передачи и )ia выводе В присутствует низкий уровень, то выход С. cor. iacHO онисаник) |1аботы уси, 1ите. 1я- форми)овате.1Я 60 нринимает значепне ло0 гической 1.

Поскольку первоначально в первом такте состояние на BHCIHUCM входе-выходе (i() неизвестно, то после обработки первой команды niecToii пеночки в буферпом регистре 49

5 остается код . 1огическо11 неонреде.пенностп пли состояния ВЫСОКО10 выходного сопротивления Вторая команда П1естой цепочки oHHCbiHai-F ,ь1 одно|1 1 ехстабильпый вывод Г, Koujpbiii в ;1анньп1 момент находится в состоянии .югической «1, в результате чего

С noc.ie обработки этой команды содержимое 6yij)epnoio )егистра 49 равно коду логиче- CKoii .. В пропес се обработки четвертой команды niecToii цсмючкп сигна.ч, код которого сп.ич1жится в буфе)ном рег истре 49, передастся на вход .4 усилите.тя-формиро5 вате.чя ((}.

Toi o, как обработана пос.тедпяя комапда таблицы соединений, цикл операций Д.1Я JiaiiHoii итерации завершается. Поско,)- ку это первая итерация первого такта, то

„ содержимое трипера 26 всегда равно в этом случае единице. (.,:1едовате. 1ьпо, для даппого такта осупи ств;1яется переход к с, 1(туюн1ей итерации, пока пе достигпуто усго11чивое состояние.

Вторая (и после.тукмцие) итерация моде5 лировапия также начинается с пасгройкн двунап)авленнь1х выводов обьекта на передачу. Так, например, во время первой итерации двунаправленный вывод В усилнте.чя- формирователя 60 неренастраивается на прнем информации. Поэтому прежде чем

0 осуществлять обмен информацией между В1)1водами цифрового , необходимо настройку В111ВОДОВ вернуть к исходному состоянию. При этом вторичной настройке подвергается то.чько один дву11аправ,1еп1п,1Й выво.т В уси,1ите,1я-формировате. 1Я tiO, па5 стройка остальн.1х вьпихчов цифрового екта остается без изменений.

Во второй итерации в нроцессе обработки команд вы11о, 1няк)тся те же действия на том

же наборе BueiiiHUx сш на.пои (таб.,1. 2). Однако да.ич , начиная с IITOJXJM нтерании, при опраОотке каждой ра,делите.1ьной команды |Ц)(111.(Н1)ДИ 1 ея (|)авненне С(кгояннй н насгоя- нхей н 11|)едыду1цей нтерациях. т. е. с одер- жнмо1() буферного регистра 49 и младших ра: .рядои но.чя 59 команды. Так как к и()о- цесее моделирования во второй итерации еоетояния всех узлов, онисанных цепочками 1чоманд, не и:-1меняются по ераниению с нре- дыдуньей 11те1)анией (габл. Г)), то состояние тршгера 2Г) (Ti26) равно нулю, что свиде- гельсгвуег об установившемся состоянии цифрового об ьекта. 11о :)тому в следую1ций момент ;гчМ :нн на ()де 9 устройства H(J- ив,1Я(МЧЯ cHrii:i. i, сиидегс. 1ЬСГвук)Н1ИЙ об f KCH iJiiHM 11()()1Ич са М1)де:1ировиния luitjipo- tioi;; ofiLcKia в нервом laKie. ЭВЛ, нолучив -)(П сшнал, снимает с требуемых инфор- м; ционньгх вьгходов 2 :и1коди))ванные ;(на- чення сигна,1ов и переходит к их аналн: у. (Для первого такта ЭВМ получает неиз- iieciHue (начение CHI нала на вЫ ода-Х С или Л усилите. 1Я-формироватео1Я ВО).

В (цюцессе моде.1И|)о1)ання циф1)овог() |)1;.екта во вч ором laKie на внснн1ие BijUto- U,; 1)2 (if) носгунает другой набор сигналов (iaoi. 2). il,Hij )OBoii обьект во втором такте моделируется также .ta две ите|) аналогичным )М.

Г) ня1 и1 игерацин rpeibeio такта noc. ie НЛО. :;к нрои ujiUv ia обработка команд чет1)1- рех 11Г|:()чек, циф)оной объект оказываег и слсл .кнщ М состоянин; i|iiirre() (И сброним1, MHKpov хема силипсл.я-1|)ормирова i е;1Я tJO выб|)ана, Bbi6)aiio нанра1 ление не)едачи С ихода Л на вход-вьгход 5. при :(том вход Л |1аходнтся в состоянии lu.icoKoi o сонротив- . от пред|)|дунич1 итерацин, С чсили теля-(|1ор 1ирова те.1я 60 находится в со- егоянии высокого вь,г одного сопротивления. /1,а.тее блок 7 считывает не)р(ук) команду пятой ценочки. Э та команда онисывает внешний вывод 65, значение на котором в третьем такте равно нулю (табл. 2). Закодироваиное значение ,1О1 ическо| ij ; (I занисьн ается в бу- (|н рньн1 |)е1исг1) 4Г , и ипем счи плвается с.)н1ая команда. И|ч;)ая к( нятой цеиичкн (jHHCi,iisaeT lihsnoi В уси.1нтеля-4 ор- мироиате.1Я 60, KOTO)i, работает i данный момсн: iwiK ввгходно). С л1 довате.:1Ы1о, вывсхч т находи 1СЧ в akiHBHii.M ,1О1НЧ1 ском состоянии. Код -лого aKTHHHOio логическогс) сос юя- но связи 15 ностунас на инфо()мацион- ми | .х()д узла 24. Так как данная команда Не оннсывае вьпзод с )ГК1П1Гтым к()Л.1ектором I ); ,,,едит1яемы1 | П) и h регнсгре49 на связи 15 присутствуют коды ак1ивных логических сост 1иний ( . е. 1-|ар1иие раз|)яды этих )ll c(Jдe;),-i,гг Л ;:и), то на выходе 4.:ieMeii- : -Ijin ;,- юявляек я логическая «1.. . .1 но связи 12 иостунает, с одной . : .| iji i;. .-..I i ене)атора 45 н тем самым 1 а: .; :;. ;::n;ii i ею, а следовательно, устрой- стн I HiM.iM. ( другой стороны, сигнал

информирует ЭВЛ о том, что в одиом узле об ьекта в один момент времени возникло неко)ректпое сочета)1ие сигна, 1ов, т. е. в одном узле присутствует несколько выходов, на- холящихся в активном логическом состоянии.

Исходя из заданно1Ч) набора сигналов для данного такта и содержимого счетчика 30 адресов |1азработчик цифрового o6i)

екта может от1ределить узе,т, в котором возник конфликт, и недопустимую комбинацию сигналов. В данном с,:1учае в третьем такте на выводе 65 задание логического «О О1пи- бочно. Поэтому, скорректи(1овав таблицу значений сигналов но тактам (таб,ч. 2, такт

3), разработчик заново занускает устройство д,тя мод1 лнрования цифровых об ьектов. При иов1О1)ном запуске устройства в течение первых двух гактов осуи1ествляются анало1 ичные операции на тех же наборах сигна,тов. F- C,TH считать, что состояние высокого сонротивления восиринимается входом граизисторио-транзист орной и друшх совместных но уровням Л01НК как значение , i()- I ической «1, то ироцесс моде.мирования в такте 3 будет нроведен за три

итерации (табл. 5). В такте 3 вывод В уси- .чителя-(к)()миронате. 1я fiO работает как выходной, т. е. на нем присутствует активный логический уровень, с,тедовате;1ьно, хотя (()ормироват1 1ь 28 в пронессе обработки соответствукице11 команды и вырабатывает

имнульс на вьгходе 17, перенастройка Toi o вь1вода на прием не нроисходит.

По окончаипи седьмой итерации можио считать, что моделированне ци(|) обТ)- екта на нротяженни трех тактов завери1ено.

1 ормула изопретения

Устройство для моделирова1П1я цифровых обьект ов, содержантее т(аборные гкхпя, коммутато, перв1.1Й и второй регистры, пе- рек, 1К)чате,:и) разрядов, блок микронро- 1 раммиого уиравления и блок памяти, ин(})ормационньи1 вход-выход и адресный вход которого соединены с входом-выходом и адресным в1..|Х()дом б,ч()ка микропрограммиого управления соответственно, унр чвляюни1е

выходы которого с нервого по пятый соединены соответственно с информационным входом нереключателя разрядов, с синхро- 1П13ирук)цим входом первого регистра, с выходом сигнала окончания моделирования устройства, с управ,:|яюи1ими входами нереключате,чя разрядов и коммутатора и с син- хронизируюн1им входом второго регистра, информационные входы нервого и второго регистров соединены с выходами иереклю- чате,:|я разрядов, информационный вход уетройства соединен е первым информационным входом коммутатора, выход которого нодключен к информационному входу блока микропрограммного управления, вход пуска которого является входом пуска устройства.

отличающееся тем, что, с целью расширения функциональных возможностей за счет моделирования об1,ект()в, содержащих интегральные схемы с выходными контактами, объединяемыми в общую тину, микросхемы, имеющие выход с тремя устойчивыми состояниями, и микросхемы с двунаправленными контактами, в него введены но числу наборных полей преобразователи логического сигнала в код и элементы с трехстабильным выходом, информационный и управляющий вход каждого из которых соединены с вы

ходами соответствующих разрядов псрвогч) и второго регистров, а выход подключен к соответствующему входу наборного поля, выход которого подключен к входу соответствующего преобразователя логического сигнала в код, выходы преобразовате, 1ей , К)ги- ческого сигнала в код соединены с информационным выходом устройства и с вторым информационным входом коммутатора, Hiec- той выход блока микропрограммного унрав- ления является выходом сигнала ошибки устройства.

15

гц

Фиг. 2

34

;я /7 8 k /

35

-42

W

п,

т 27

37

26

ПС22

28

55

/5

29

е

27

39

42

V V V

30

J I

Фиг.д

Фиг А

Фиг. 6

с ночоло

)

Иастройна дбунопраВ- /1енных быбодоб

Hernrz

Настройна ёсек ocmajJbHbix §ь/6одо6

Т г 26: 0 ЛР2

Рг29--

CчЗO:--C дO

J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для связи процессора с устройствами ввода-вывода | 1973 |

|

SU495659A1 |

| Управляющая логическая машина | 1974 |

|

SU539301A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для моделирования цифровых объектов | 1979 |

|

SU898438A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Процессор цифровой вычислительной системы | 1971 |

|

SU475897A1 |

| Вычислительный модуль и способ обработки с использованием такого модуля | 2018 |

|

RU2689433C1 |

| Микропрограммное устройство управления,диагностирования и реконфигурации | 1986 |

|

SU1392561A1 |

| Устройство для контроля логических схем | 1976 |

|

SU595735A1 |

| Устройство для сопряжения разнотипных вычислительных машин | 1986 |

|

SU1381526A2 |

Изобретение относится к вычислительной технике. Целью изобретения является рас1иире}1ие функциональных возможностей за счет обеспечения моделирования объектов, содержащих интегральные схемы с выходными контактами, объединяемыми в общую И1ину, микросхемы, имеющие выход с тремя устойчивыми состояниями, микросхемы с двунаправленными контактами. Устройство содержит наборные иоля 1, выход 2, коммутатор 3, вход 4, регистр 5, нереключатель 6 разрядов, блок 7 микропрограммного управления, вход 8, выход 9, блок 10 памяти, регистр 11, выход 12, преобразователи 13 логического сигнала в код и элементы 14 с трех- стабильным выходом ио числу наборных полей. 12 ил., 5 табл. W оо o о:)

Ре 9 СО, П: 11

Оброботно. HOfiandoi §ы). типа

Об робогпна роддели те/гьиои /{омандо

Рг5 Рг291 Ре 9

&о/да ч о сигнала 9

Ноне, ц

Z)

Фиг.1

С

Начало

Надиробание

&ыбОр UCfnOVHUHQ по

РеШ

Фиг 9

Фиг.Ю

7г Z6- 1 ,

5л10ССч 1---Рг29

(Нонецj

Редактор О, Юрковенкан Зака: 1845/49

Составитель А. Жеренов

Техред И. ВересКорректор М. Шароши

. i /т: Тираж 673Подписное

ВНИИПИ 1()сулнрственного комитета (:(.СР по делам изобретений и открытий

1 13035, Л осква, Ж 35, Раушская иаП., д. 4/5 Производствеиио-полиграфическое предприятие, г. Ужгород, ул. Троектиая, 4

62

61

Фиг. J2

| Устройство для моделирования цифро-ВыХ Об'ЕКТОВ | 1979 |

|

SU832558A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования цифровых объектов | 1979 |

|

SU898438A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-05-23—Публикация

1985-06-12—Подача