Изобретение относится к вычислительной технике, в частности к средствам автоматической проверки цифровых объектов, и может быть использо- вано для функционального контроля процессоров, контроллеров, запоминающих устройств и прочих блоков ЭВТ1 и других средств цифровой техники при их производстве и техническом обслу- живании.

Цель изобретения - повышение быстродействия.

Введение блока моделирования неустойчивости и второго генератора псев- дослучайных кодов позволяет производить запись сформированной испытательной последовательности в выходной регистр (и, следовательно, выдачу ее на объект диагностирования) в раз- личные для каждого выхода моменты времени в каждом цикле Лорнирования последовательности, что позволяет достаточно просто определить устойчивость работы объекта диагностирования при подаче на него этой последовательности (т.е. оценить качество испытательной последовательности). Это, в свою очередь, дает возможность использовать в качестве испытательных последовательностей наиболее эффективные (псевдослучайные) в максимальном объеме, что приводит к уменьшению времени проверки цифровых блоков.

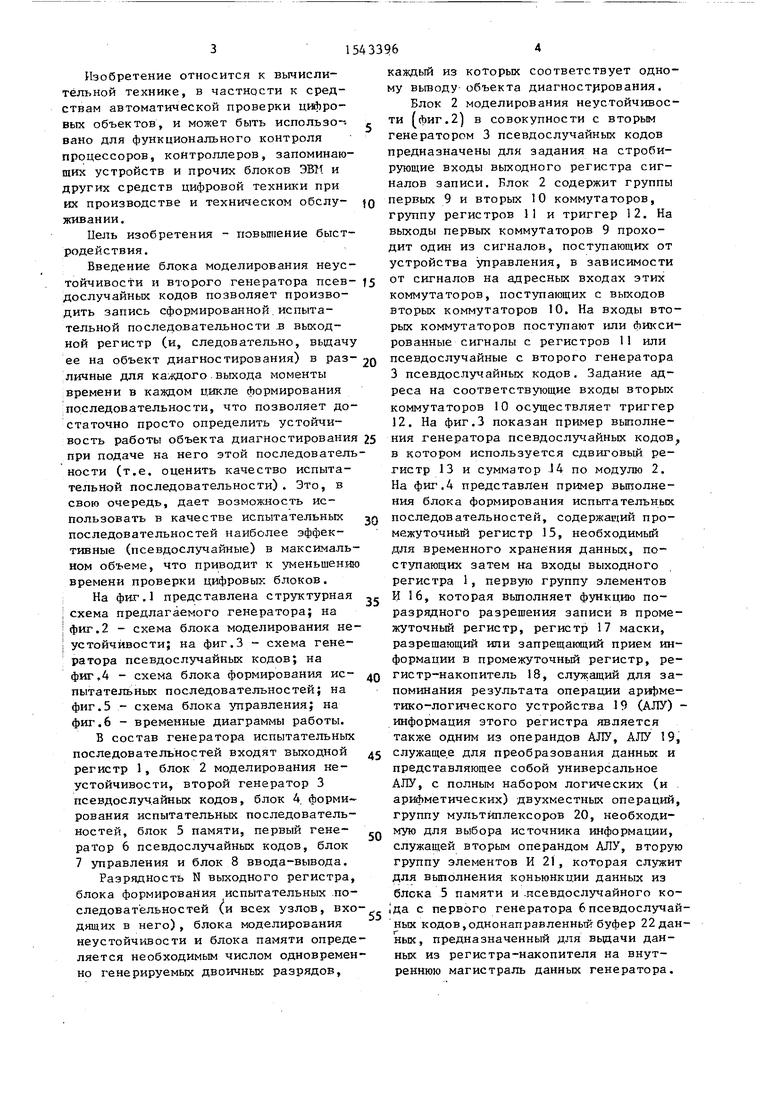

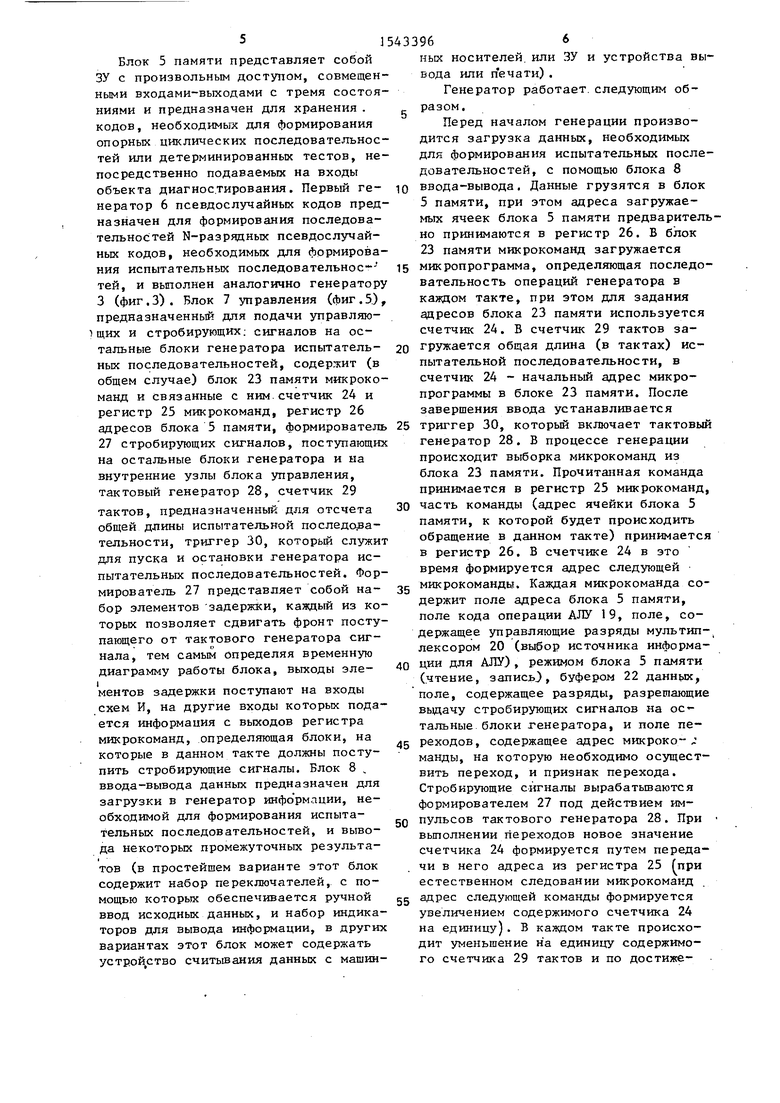

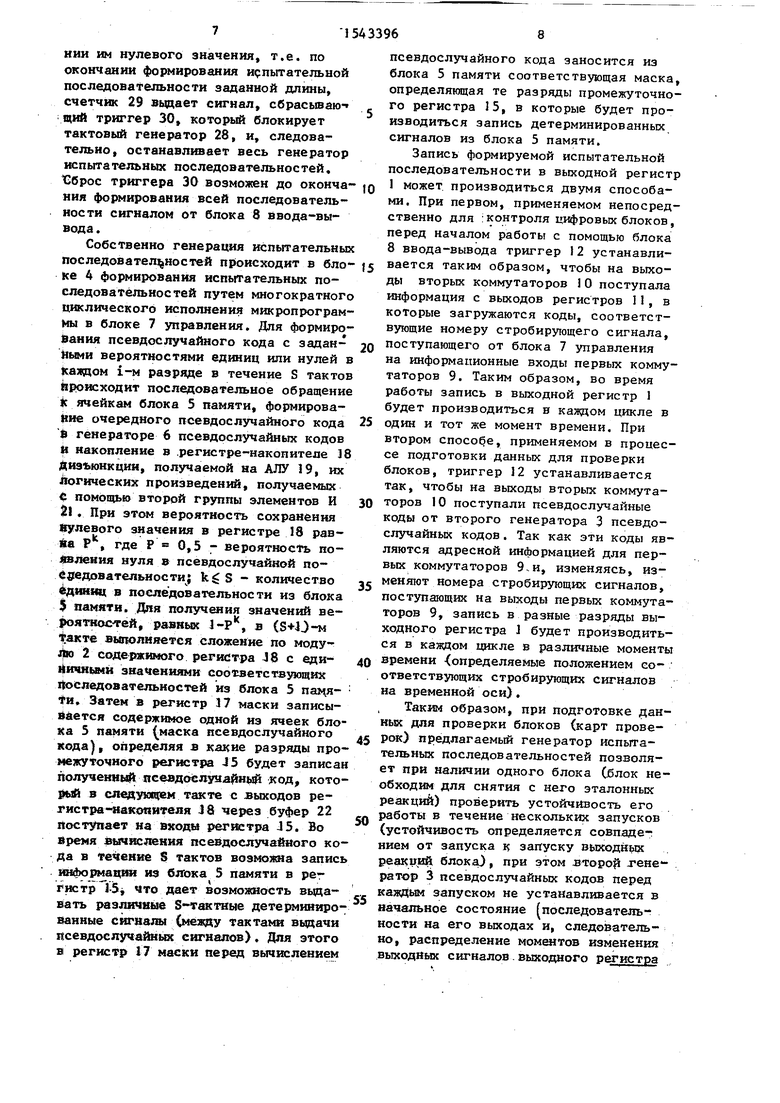

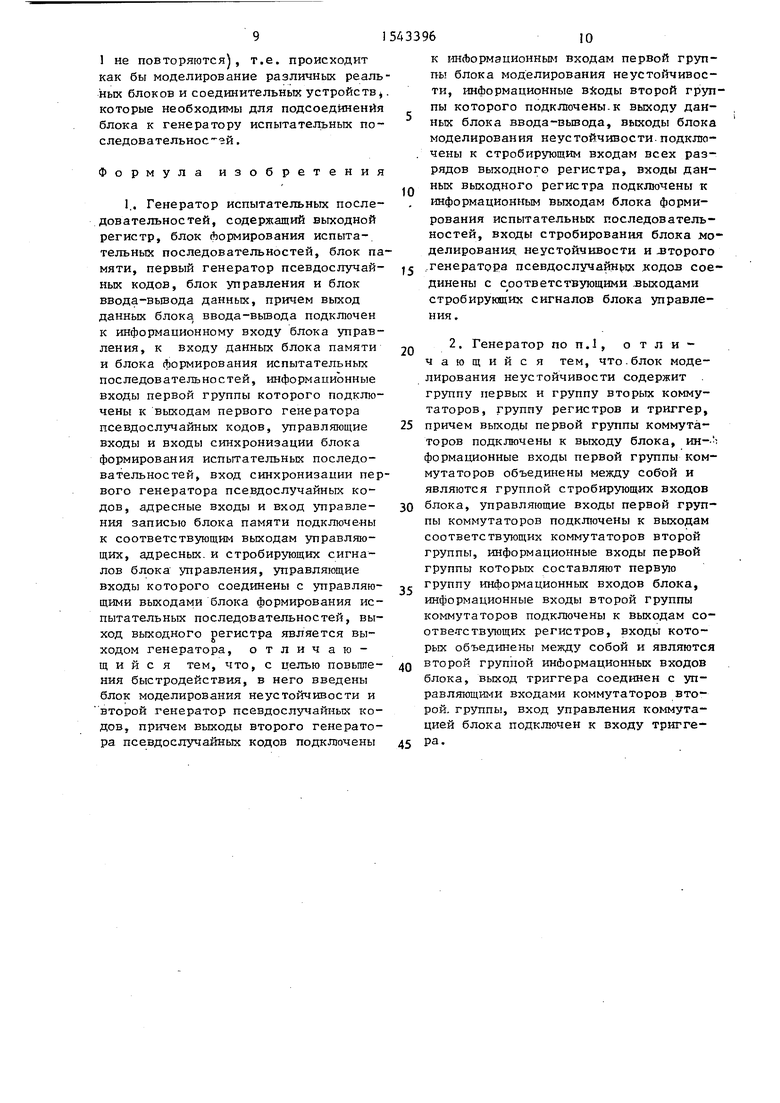

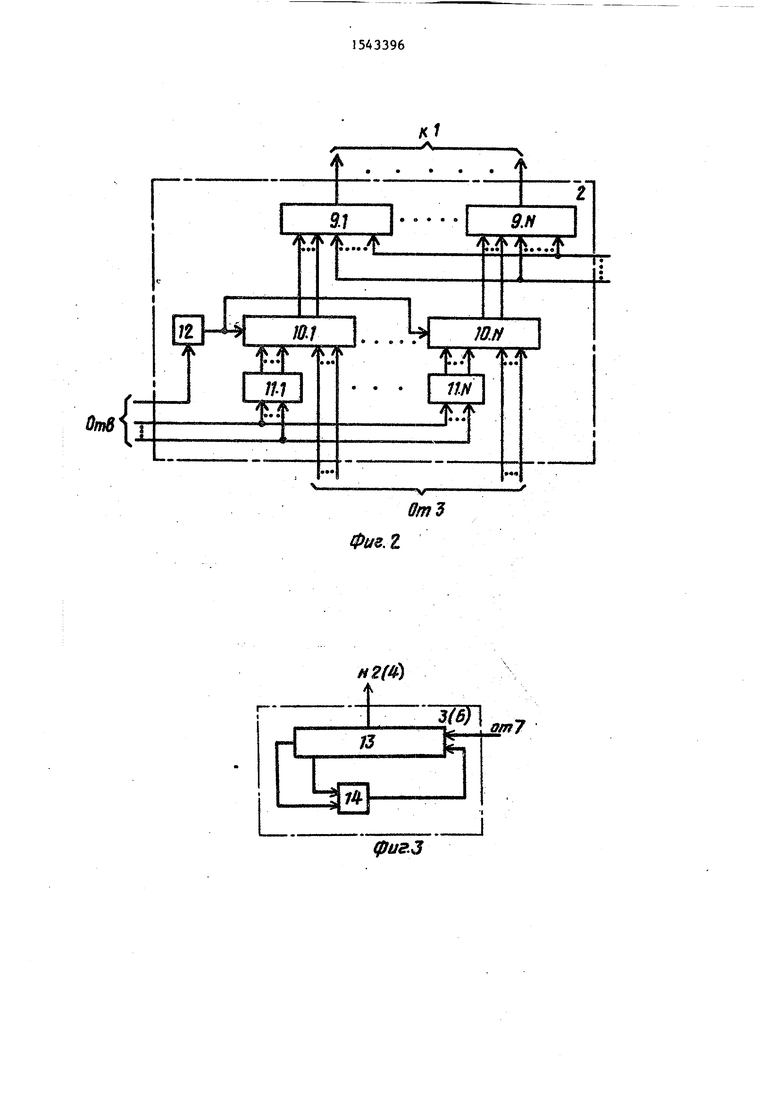

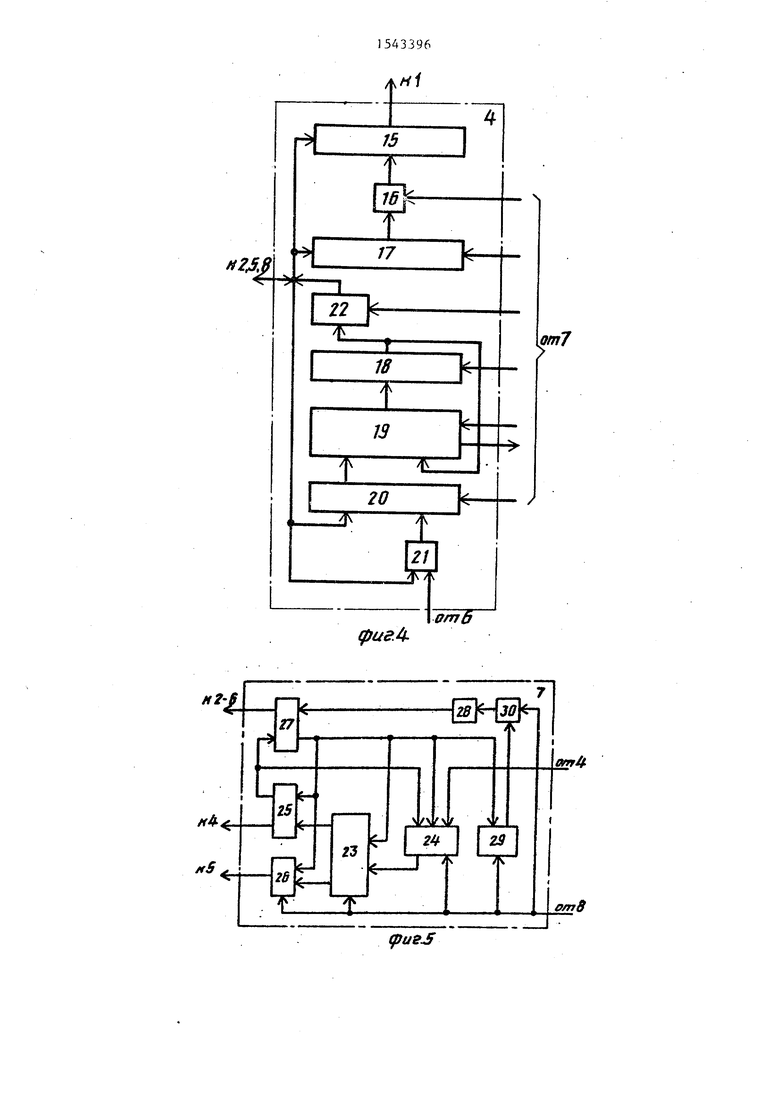

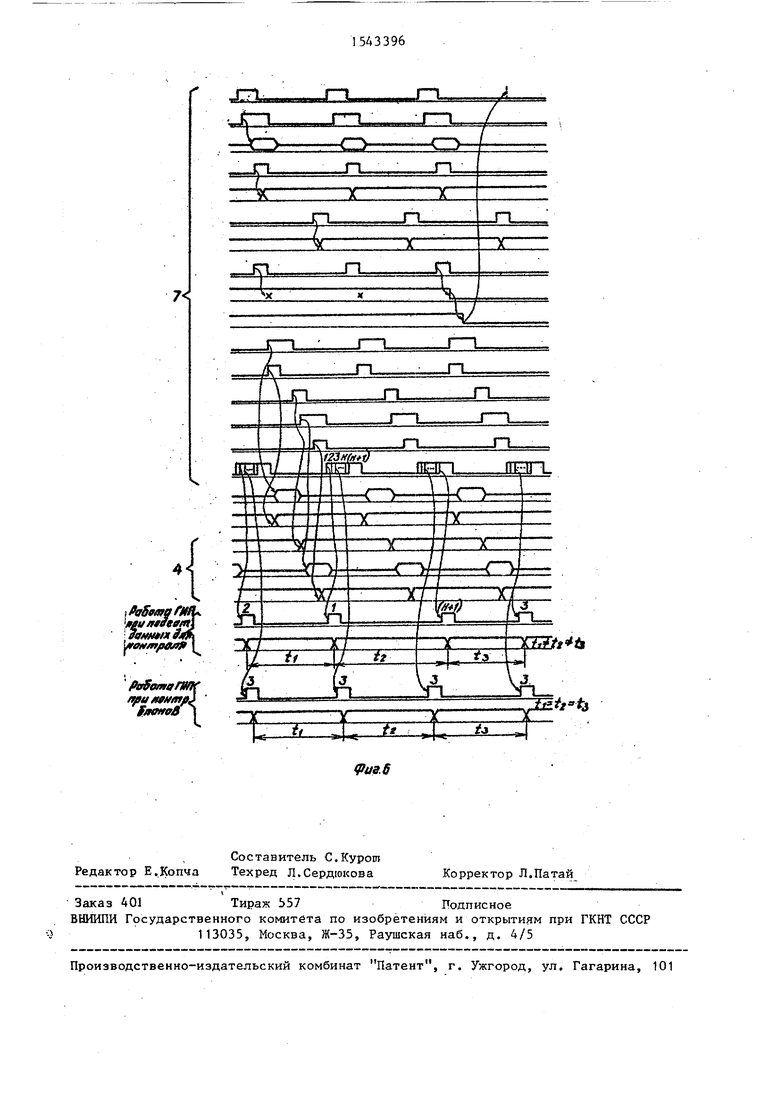

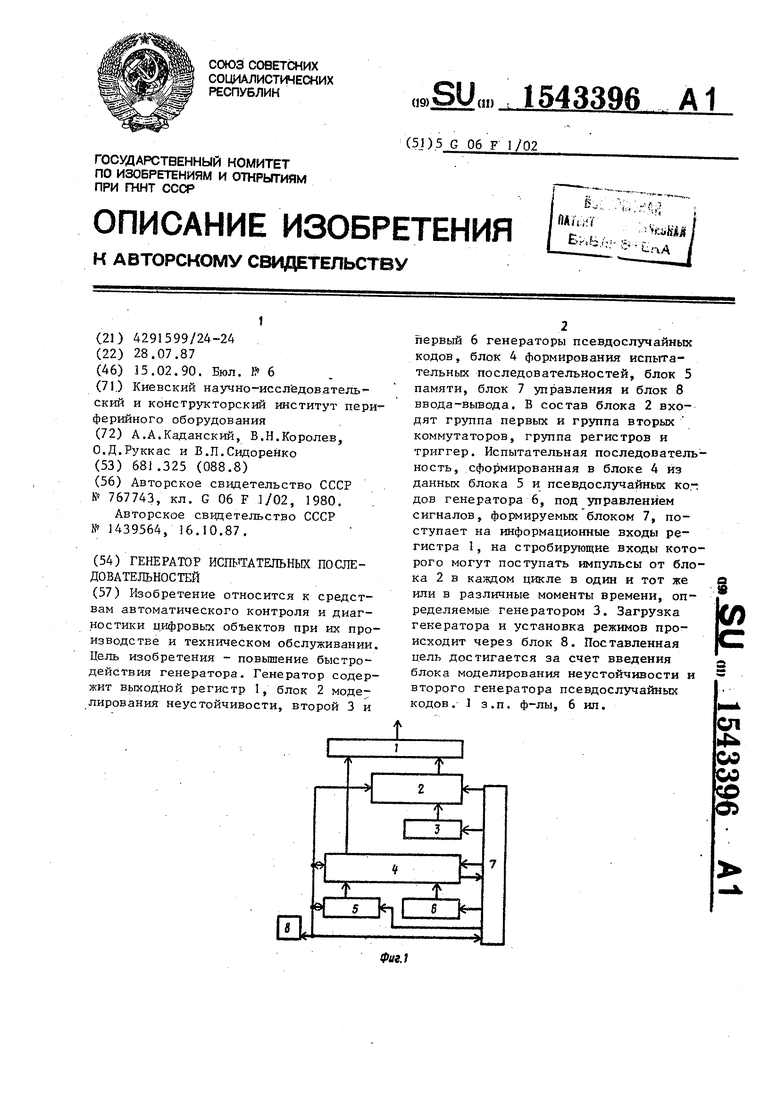

На фиг.1 представлена структурная схема предлагаемого генератора; на фиг.2 - схема блока моделирования неустойчивости; на фиг.3 - схема генератора псевдослучайных кодов; на фиг,4 - схема блока формирования ис- пытательных последовательностей; на фиг.5 - схема блока управления; на фиг.6 - временные диаграммы работы.

В состав генератора испытательных последовательностей входят выходной регистр 1, блок 2 моделирования неустойчивости, второй генератор 3 псевдослучайных кодов, блок 4 форми рования испытательных последовательностей, блок 5 памяти, первый гене- раТор 6 псевдослучайных кодов, блок 7 управления и блок 8 ввода-вывода.

Разрядность N выходного регистра, блока формирования испытательных последовательностей (и всех узлов, входящих в него), блока моделирования неустойчивости и блока памяти определяется необходимым числом одновременно генерируемых двоичных разрядов,

Q

5 Q 5 Q

Q

5

каждый из которых соответствует одному выводу объекта диагностирования.

Блок 2 моделирования неустойчивости ((Ъиг.2) в совокупности с вторьнч генератором 3 псевдослучайных кодов предназначены для задания на строби- рующие входы выходного регистра сигналов записи. Блок 2 содержит группы первых 9 и вторых 10 коммутаторов, группу регистров 11 и триггер 12. На выходы первых коммутаторов 9 проходит один из сигналов, поступающих от устройства управления, в зависимости от сигналов на адресных входах этих коммутаторов, поступающих с выходов вторых коммутаторов 10. На входы вторых коммутаторов поступают или Ликси- рованные сигналы с регистров 11 или псевдослучайные с второго генератора 3 псевдослучайных кодов. Задание адреса на соответствующие входы вторых коммутаторов 10 осуществляет триггер 12. На фиг.3 показан пример выполнения генератора псевдослучайных кодов, в котором используется сдвиговый регистр 13 и сумматор J4 по модулю 2. На фиг.4 представлен пример выполнения блока формирования испытательных последовательностей, содержащий промежуточный регистр 15, необходимый для временного хранения данных, поступающих затем на входы выходного регистра 1, первую группу элементов И 16, которая выполняет функцию поразрядного разрешения записи в промежуточный регистр, регистр 17 маски, разрешающий или запрещающий прием информации в промежуточный регистр, регистр-накопитель 18, служащий для запоминания результата операции арифметико-логического устройства 19 (АЛУ) - информация этого регистра является также одним из операндов АЛУ, АЛУ 19, служащее для преобразования данных и представляющее собой универсальное АЛУ, с полным набором логических (и арифметических) двухместных операций, группу мультиплексоров 20, необходимую для выбора источника информации, служащей вторым операндом АЛУ, вторую группу элементов И 21, которая служит для выполнения коньюнкиии данных из блока 5 памяти и псевдослучайного ко- (да с первого генератора 6 псевдослучайных кодов,однонаправленный буфер 22 данных, предназначенный для выдачи данных из регистра-накопителя на внутреннюю магистраль данных генератора.

5

Блок 5 памяти представляет собой ЗУ с произвольным доступом, совмещенными входами-выходами с тремя состояниями и предназначен для хранения . кодов, необходимых для формирования опорных циклических последовательностей или детерминированных тестов, непосредственно подаваемых на входы объекта диагностирования. Первый генератор 6 псевдослучайных кодов предназначен для формирования последовательностей N-разрядных псевдослучайных кодов, необходимых для Лормирова- ния испытательных последовательное-- тей, и выполнен аналогично генератору 3 (фиг.З). Блок 7 управления (Лиг. 5), предназначенный для подачи управляюих и стробирующих. сигналов на остальные блоки генератора испытательных последовательностей, содержит (в общем случае) блок 23 памяти микрокоманд и связанные с ним счетчик 24 и регистр 25 микрокоманд, регистр 26 адресов блока 5 памяти, Формирователь 27 стробирующих сигналов, поступающих на остальные блоки генератора и на внутренние узлы блока управления, тактовый генератор 28, счетчик 29 тактов, предназначенный для отсчета общей длины испытательной последовательности, триггер 30, который служит для пуска и остановки генератора испытательных последовательностей. Формирователь 27 представляет собой набор элементов задержки, каждый из которых позволяет сдвигать фронт поступающего от тактового генератора сигнала, тем самым определяя временную диаграмму работы блока, выходы элеентов задержки поступают на входы схем И, на другие входы которых подается информация с выходов регистра икрокоманд, определяющая блоки, на которые в данном такте должны поступить стробирующие сигналы. Блок 8 , ввода-вывода данных предназначен для загрузки в генератор инфо рмтции, необходимой для формирования испытательных последовательностей, и вывода некоторых промежуточных результаов (в простейшем варианте этот блок одержит набор переключателей, с поощью которых обеспечивается ручной вод исходных данных, и набор индикаоров для вывода информации, в других ариантах этот блок может содержать стройство считывания данных с машин433966

ных носителей или ЗУ и устройства вывода или печати).

Генератор работает следующим образом.

Перед началом генерации производится загрузка данных, необходимых для формирования испытательных последовательностей, с помощью блока 8 Ю ввода-вывода. Данные грузятся в блок 5 памяти, при этом адреса загружаемых ячеек блока 5 памяти предварительно принимаются в регистр 26. В блок 23 памяти микрокоманд загружается 15 микропрограмма, определяющая последовательность операций генератора в каждом такте, при этом для задания адресов блока 23 памяти используется счетчик 24. В счетчик 29 тактов за20 гружается общая длина (в тактах) испытательной последовательности, в счетчик 24 - начальный адрес микропрограммы в блоке 23 памяти. После завершения ввода устанавливается

25 триггер 30, который включает тактовый генератор 28. В процессе генерации происходит выборка микрокоманд из блока 23 памяти. Прочитанная команда принимается в регистр 25 микрокоманд,

0 часть команды (адрес ячейки блока 5 памяти, к которой будет происходить обращение в данном такте) принимается в регистр 26. В счетчике 24 в это время формируется адрес следующей

5 микрокоманды. Каждая микрокоманда содержит поле адреса блока 5 памяти, поле кода операции АЛУ 19, поле, содержащее управляющие разряды мультиплексором 20 (выбор источника информа0 ции Для АЛУ), режимом блока 5 памяти (чтение, запись), буфером 22 данных, поле, содержащее разряды, разрешающие выдачу стробирующих сигналов на остальные блоки генератора, и поле пе5 реходов, содержащее адрес микроко- ; манды, на которую необходимо осуществить переход, и признак перехода. Стробирующие сигналы вырабатываются формирователем 27 под действием им0 пульсов тактового генератора 28. При выполнении переходов новое значение счетчика 24 формируется путем передачи в него адреса из регистра 25 (при естественном следовании микрокоманд

5 адрес следующей команды формируется увеличением содержимого счетчика 24 на единицу). В каждом такте происходит уменьшение на единицу содержимого счетчика 29 тактов и по достижении им нулевого значения, т.е. по окончании формирования испытательной последовательности заданной длины, счетчик 29 выдает сигнал, сбрасывают ций триггер 30, который блокирует тактовый генератор 28, и, следовательно, останавливает весь генератор испытательных последовательностей. Сброс триггера 30 возможен до оконча- ния формирования всей последовательности сигналом от блока 8 ввода-вывода.

Собственно генерация испытательных последовательностей происходит в бло- ке 4 формирования испытательных последовательностей путем многократного циклического исполнения микропрограммы в блоке 7 управления. Для формирования псевдослучайного кода с задан- ными вероятностями единиц или нулей в каждом i-м разряде в течение S тактов происходит последовательное обращение к ячейкам блока 5 памяти, формирование очередного псевдослучайного кода в генераторе 6 псевдослучайных кодов и накопление в регистре-накопителе 18 дизъюнкции, получаемой на АЛУ 19, их логических произведений, получаемых с помощью второй группы элементов И 21. При этом вероятность сохранения нулевого значения в регистре 18 равна Р , где Р в 0,5 - вероятность появления нуля в псевдослучайной последовательности; kЈS - количество единиц в последовательности из блока 5 памяти. Для получения значений вероятностей, равных 1-Рк, в (S+O-м такте выполняется сложение по модулю 2 содержимого регистра J8 с еди- минными значениями соответствующих последовательностей из блока 5 памя- ти. Затем в регистр J7 маски записывается содержимое одной из ячеек блока 5 памяти (маска псевдослучайного кода), определяя я какие разряды промежуточного регистра J5 будет записан полученный псеадосяуйайный код, который в следующем такте с выходов регистра-накопителя J8 через буфер 22 поступает на входы регистра Л5. Во время вычисления псевдослучайного кода в течение S тактов возможна запись информации из блока 5 памяти в регистр 1-5, что дает возможность выда- вать различные S-тактиые детерминированные сигналы (между тактами выдачи псевдослучайных сигналов). Для этого в регистр 17 маски перед вычислением

псевдослучайного кода заносится из блока 5 памяти соответствующая маска, определяющая те разряды промежуточного регистра 15, в которые будет производиться запись детерминированных сигналов из блока 5 памяти.

Запись формируемой испытательной последовательности в выходной регистр 1 может производиться двумя способами. При первом, применяемом непосредственно для контроля цифровых блоков, перед началом работы с помощью блока 8 ввода-вывода триггер I2 устанавливается таким образом, чтобы на выходы вторых коммутаторов 10 поступала информация с выходов регистров 1I, в которые загружаются коды, соответствующие номеру стробирующего сигнала, поступающего от блока 7 управления на информационные входы первых коммутаторов 9. Таким образом, во время работы запись в выходной регистр 1 будет производиться в каждом цикле в один и тот же момент времени. При втором способе, применяемом в процессе подготовки данных для проверки блоков, триггер 12 устанавливается так, чтобы на выходы вторых коммутаторов 10 поступали псевдослучайные коды от второго генератора 3 псевдослучайных кодов. Так как эти коды являются адресной информацией для первых коммутаторов 9,и, изменяясь, изменяют номера стробирующих сигналов, поступающих на выходы первых коммутаторов 9, запись в разные разряды выходного регистра 1 будет производиться в каждом цикле в различные моменты времени {определяемые положением соответствующих стробирующих сигналов на временной оси).

Таким образом, при подготовке данных для проверки блоков (карт проверок) предлагаемый генератор испытательных последовательностей позволяет при наличии одного блока (блок необходим для снятия с него эталонных реакций) проверить устойчивость его работы в течение нескольких запусков (устойчивость определяется совпадением от запуска к запуску вьосодных реакций блока), при этом второй генератор 3 псевдослучайных кодов перед каждым запуском не устанавливается в начальное состояние последовательности на его выходах и, следовательно, распределение моментов изменения выходных сигналов выходного регистра

1 не повторяются), т.е. происходит как бы моделирование различных реальных блоков и соединительных устройств, которые необходимы для подсоединения блока к генератору испытательных последовательное ЭЙ .

Формула изобретения

1. Генератор испытательных последовательностей, содержащий выходной регистр, блок сформирования испытательных последовательностей, блок памяти, первый генератор псевдослучайных кодов, блок управления и блок ввода-вывода данных, причем выход данных блока ввода-вывода подключен к информационному входу блока управления, к входу данных блока памяти и блока Лормирования испытательных последовательностей, информационные входы первой группы которого подключены к выходам первого генератора псевдослучайных кодов, управляющие входы и входы синхронизации блока формирования испытательных последовательностей, вход синхронизации первого генератора псевдослучайных кодов, адресные входы и вход управления записью блока памяти подключены к соответствующим выходам управляющих, адресных и стробирующих сигналов блока управления, управляющие входы которого соединены с управляющими выходами блока формирования испытательных последовательностей, выход выходного регистра является выходом генератора, отличающий с я тем, что, с иелъю повышения быстродействия, в него введены блок моделирования неустойчивости и второй генератор псевдослучайных кодов, причем выходы второго генератора псевдослучайных кодов подключены

к информационным входам первой группы блока моделирования неустойчивости, информационные входы второй группы которого подключены.к выходу данных блока ввода-вывода, выходы блока моделирования неустойчивости подклю- . чены к стробирующим входам всех разрядов выходного регистра, входы данных выходного регистра подключены к информационным выходам блока формирования испытательных последовательностей, входы стробирования блока моделирования неустойчивости и .второго

генератора псевдослучайных кодов соединены с соответствующими выходами стробирующих сигналов блока управления.

2. Генератор по п.), отличающийся тем, что блок моделирования неустойчивости содержит группу первых и группу вторых коммутаторов, группу регистров и триггер,

причем выходы первой группы коммутаторов подключены к выходу блока, ин-- : формационные входы первой группы коммутаторов объединены между собой и являются группой стробирующих входов

блока, управляющие входы первой группы коммутаторов подключены к выходам соответствующих коммутаторов второй группы, информационные входы первой группы которых составляют первую

группу информационных входов блока, информационные входы второй группы коммутаторов подключены к выходам соответствующих регистров, входы которых объединены между собой и являются

второй группой информационных входов блока, выход триггера соединен с управ ляклцими входами коммутаторов второй, группы, вход управления коммутацией блока подключен к входу триггеРаОтв

{

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

Изобретение относится к средствам автоматического контроля и диагностики цифровых объектов при их производстве и техническом обслуживании. Цель изобретения - повышение быстродействия генератора. Генератор содержит выходной регистр 1, блок 2 моделирования неустойчивости, второй 3 и первый 6 генераторы псевдослучайных кодов, блок 4 формирования испытательных последовательностей, блок 5 памяти, блок 7 управления и блок 8 ввода-вывода. В состав блока 2 входят группа первых и группа вторых коммутаторов, группа регистров и триггер. Испытательная последовательность, сформированная в блоке 4 из данных блока 5 и псевдослучайных кодов генератора 6, под управлением сигналов, формируемых блоком 7, поступает на информационные входы регистра 1, на стробирующие входы которого могут поступать импульсы от блока 2 в каждом цикле в один и тот же или в различные моменты времени, определяемые генератором 3. Загрузка генератора и установка режимов происходит через блок 8. Поставленная цель достигается за счет введения блока моделирования неустойчивости и второго генератора псевдослучайных кодов. 1 з.п.ф-лы, 6 ил.

Фиг.1

от7

фиг.З

96KVSI

| Генератор псевдослучайных кодов | 1978 |

|

SU767743A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

Авторы

Даты

1990-02-15—Публикация

1987-07-28—Подача