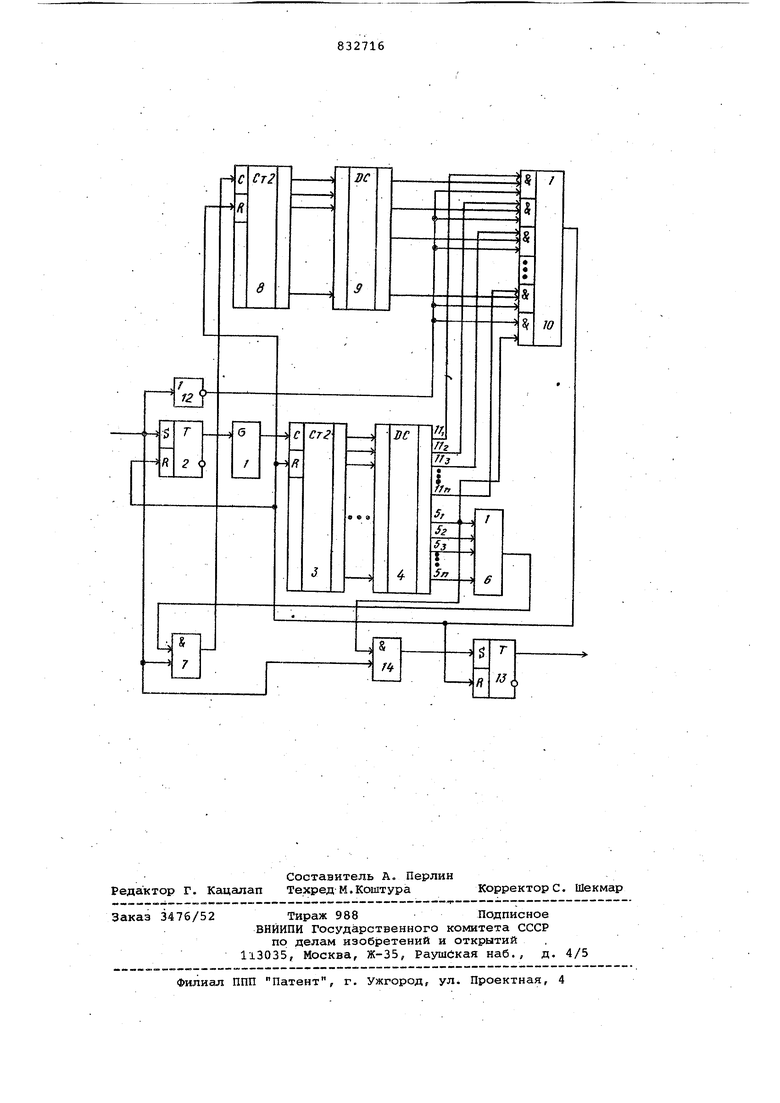

Изобретение относится к импульсной технике и может быть использова но в устройствах передачи сигнала по проводным линиям.связи на больши расстояния. По основному авт. св. 702503 известно устройство, содержащее упр ляемый генератор, вход которого сое динен с выходом управляемого триггер а выход соединен со счетным входом первого дешифратора, первая группа выходов которого через элемент ИЛИ подключена к входу элемента И, к др гому входу этого элемента И подключен вход устройства, а выход соединен со счетным входом второго счетчика, выходы которого соединены с входами второго дешифратора, выходы второго дешифратора соединены с пер выми входами схемы коммутации, на вторые.входы схемы коммутации заведена вторая группа выходов первого дешифратора, на третьи входы схемы коммутации заведен выход элемента Н вход которого соединен с входом уЬт ройства. Выход схемы коммутации заведен на установочные входы обоих счетчиков и на сброс управляющего триггера и триггера памяти, на единичный вход управляющего триггера заведен вход устройства, а на единичный вход триггера памяти - выходу первого дешифратора, выход триггера памяти является выходом устройства 1. Однако известное устройство не защищено от помех, меньших по длительности половины наименьшего квантованного сигнала, так как.триггер памяти устанавливается даже в том случае, когда на входе устройства входной сигнал отсутствует. Цель изобретения - увеличение помехоустойчивости устройства. Поставленная цель достигается тем, что в устройство, содержащее управляемый генератор, вход которого соединен с выходом управлякяцего триггера, а выход - со счетным входом первого счетчика импульсов, выходы которого подключены к входам первого деши.фратора, первая группа выходов которого через элемент ИЛИ соединена с входом элемента И, к другому входу которого подключен вход устройства, а выход соединен со счетным входом второго счетчика импульсов, выходы которого соединены с входами второго дешифратора, выходы . которого соединены с первыми входами схемы коммутации, на вторые входы схемы коммутации заведена вторая группа выходов первого дешифратора, на третьи входы схемы коммутации заведен выход элемента НЕ, вход которого соединен с входом устройства, выход схемы коммутации заведен на установочные входы обоих счетчиков и на сброс управляющего триггера и триггера памяти, единичный вход управляющего триггера соединен с входом устройства, выход триггера памяти является выходом устройства, содержит второй эле- мент И, один вход которого подключен к входу устройст-эа, другой соединен с одним из выходов первого дешифратора и входом схемы коммутации, а выход подключен к единичному входу триггера памяти. На чертеже приведена структурная электрическая схема устройства. Устройство содержит управляемый генератор 1, вход которого соеди«ен с выходом управляющего триггера 2, а выход соединен со счетным входом пер вого счетчика 3 импульсов, входы которого соединены с входами дешифратора 4, одна группа выходов 5 -5, ко торого через элементы 6 ИЛИ подключена к входу элемента 7 И, к другому входу элемента 7 И подключен вход устройства , а выход соединен со счет ным входом второго счетчика 8 импульсов, выходы которого соединены с входами дешифратора 9. Выходы дешифратора 9 соединены с первыми входами схемы 10 коммутации. К вторым входам схемы 10 коммутации подключена вторая группа выходов дешифрато ра 4. К третьим входам схемы 10 коммутации подключен выход элемента 12 НЕ, вход которого подключен к вхо ду устройства. Выход схемы 10 коммутации подключен к установочным входа обоих счетчиков 3 и 8 и на сброс управляющего триггера 2 и триггера 13 памяти. На единичный вход управляющего триггера 2 заведен вход устройства, а на единичный вход триггера памяти 13 - выход элемента 14 И, оди вход которого соединен с выходом 5 дешифратора 4, второй - с входом уст ройства. Выход триггера 13 памяти является выходом устройства. Устройство работает следующим образом. В случае подачи на-вход устройств сигналов длительностью t nnut,, tj, отличающихся от номинальных значений на величину it за счет искажения в линии связи, входной сигнал своим передним фронтом переводит управляющий триггер 2 в единичное состояние и потенциалом с выхода этого триггера запускается генератор 1. Импульсы с генератора 1 запускают счетчик ..3 по счетному входу, состояние счетчика депшфрируется дешифрато ом 4, на выходах которого формирутся сигнал5;, задержанный по отноению к переднему фронту входного сигнала на величину л- t сигнал 52, задержанный по отношению к переднему фронту входного сигнала на величину Т ( сигнал БЗ, задержанный по Отношению к переднему фронту входного сигнала на величину i сигнал 11 , задержанный по отношению , к сигналу 5 на величину ц ; сигнал 112/ задержанный по отношению к сигналу 5,f на величину t, сигнал 11, задержанный по отношению к сигналу 5 на величину t. Перечисленные сигналы располагаются во времени так, ,1то н,е .накрывают возможные поля допуска отклонения длительности вход-, ного сигнала. . . .. Если на вход устройства поступает . сигнал длительностью t, - ц + + 2 через элемент 7 ,И за время длительности входного сигнала проходит только один сигнал с элемента б ИЛИ и счетчик 8 переводится в состояние 1. Дешифратор 9 дешифрирует состояние счетчика 8, и потенциал с его первого выхода подготавливает схему 10 коммутации к прохождению сигналов 11 с дешифратора 4, после окончания входного сигнала потенциал со схемы 12 НЕ открывает схему 10 коммутации и сигнал с ее выхода сбрасывает в О счетчики 3 и 8, управлявэщий триггер 2 и триггер 13 памяти. Триггер .13 памяти устанавливается в 1 сигналом с выхода 5 дешифратора 4 через элемент 14 и, и на выходе формируется сигнал длительНОСТЬЮ t;| . Если на выход устройства поступает сигнал длительностью + 6 t tg ТО за время действия входного сигнала через элемент 7 И проходят два импульса с элемента б ИЛИ и счетчик 8 устанавливается в состояние 2, потенциал с дешифратора 9 подготавливает схему 10 коммутации к прохождению сигнала с выхода lljj дешифратора 4, после окончания входного сигнала потенциал с элемента 12 НЕ разрешает работу схемы 10 коммутации, которая выходным сигнсшом возвргццает устройство в исходное состояние и формирует на триггере 13 памяти сигнал длительностью Если на вход устройства поступает сигнал дли ельностью t,- tj+i . At то счетчик 8 импульсами с элемента 7 И устанавливается в состояние 3, дешифратор 9 потенциалом со своего третьего выхода подготавли|Вает схему 10 коммутации к прохомщению сигнала с выхода 11 дешифратора 4, который после окончания входного сигнала проходит через схему 10 коммутации, возвращает устройство в исходное состояние и сбросом триггера 13 памяти через t после его установки в 1 формирует на его выходе сигнал длительностью 1э.

Если на вход устройства поступает сигнал помехи длительностью t -s ,

то за время действия входного, сигнала через элемент 7 И не проходит ни одного импульса, счетчик 8 остается в состоянии О и ни на одном выходе дешифратора 9 нет подготавливающего потенциала. Сигнал с выхода 5 дешифратора 4 не проходит за время действия входного сигнала-(сигнала помехи через элемент 14 И на вход триггера 13 памяти, и триггер остается в состоянии О, После окончания входного сигнала потенциал с выхода элемента 12 НЕ открывает схему 10 коммутации и сигнал с выхода 5 дешифратора 4 проходит через схему 10 коммутации и сбрасывает в О управляющий триггер 2 и счетчики 3 и 8, подтверждая состояние О триггера 13 памяти.

Таким образом, в предлагаемом устройстве исключается формирование восстановленного сигнала при поступлении на вход кратковременной помехи за счет установки триггера памяти в 1 только при совпадении входного сигнала и сдвинутого импульса с дешифратора, что приводит к увеличению помехоустойчивости устройства.

Формула изобретения

Устройство для воспроизведения прямоугольных импульсов по авт, св. №702503, отличающееся тем, что, с целью увеличения помехоустойчивости, в него введен дополнительный логический элемент И, первый вход которого соединен с входной шиной устройства, второй вход - с одним из выходов первой группы первого дешифратора, а выход дополнительного логического элемента И соединен с единичным входом триггера памяти.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 702503, кл. Н 03 К 5/20, 07.03.78.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство воспроизведения прямоугольных импульсов | 1977 |

|

SU702503A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Распределитель импульсов | 1986 |

|

SU1405105A1 |

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Многопостовое устройство для контроля параметров электронных схем | 1983 |

|

SU1108374A1 |

| Устройство воспроизведения прямоугольных импульсов | 1978 |

|

SU790234A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство задержки импульсов | 1981 |

|

SU999147A1 |

| Многоканальное устройство для идентификации моделей | 1984 |

|

SU1238100A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

Авторы

Даты

1981-05-23—Публикация

1978-06-08—Подача