1

Изобретение относится к запоминающим устройствам (ЗУ) и предназначено для использования в системах памяти, в том числе выполненных на интегральных схемах с большой степенью интеграции.

Известно ЗУ с автоматическим восстановлением работоспособности, в котором устранение неисправности осуществляется путем подключения резервного оборудования 1.

Недостаток устройства - большие аппаратурные затраты.

Наиболее близким к предлагаемому является ЗУ с автоматическим вое-становлением работоспособности, содержащее блок выборки адресов, основные одноразрядные блоки памяти, входные шины и шины управления по числу разрядов хранимой информации, входной и выходные коммутаторы причем соответствующие входные шины соединены со входами основных входов памяти и информационными входами входного коммутатора, а выходы основных блоков памяти - с информационными входами соответствующих выходных коммутаторов. При отказе в этом ЗУ одного из основных блоков

памяти автоматически подключается резервный 2 .

Недостаток этого устройства - его значительная аппаратурная избыточность в связи с тем, что при отказе даже одной ячейки памяти в основном блоке заменяется весь блок памяти с неисправностью на резервный такой же информационной емкости.

Цель изобретения - упрощение устройства пут.ем уменьшения аппаратурной избыточности.

Поставленная цель достигается

тем, что в запоминающее устройство с автоматическим восстановлением работоспособности, содержащее адресный блок, группы основных накопителей, резервный накопитель, входной

и выходные коммутаторы, причем выход входного коммутатора подключен X одному из входов резервного накопителя., выход которого соединен с одним MS информационных входов выходных коммутаторов, другие информационные входы которых подключены к выходам основных накопителей, информационные входы которых подключены к родним из входов входного коммутатора

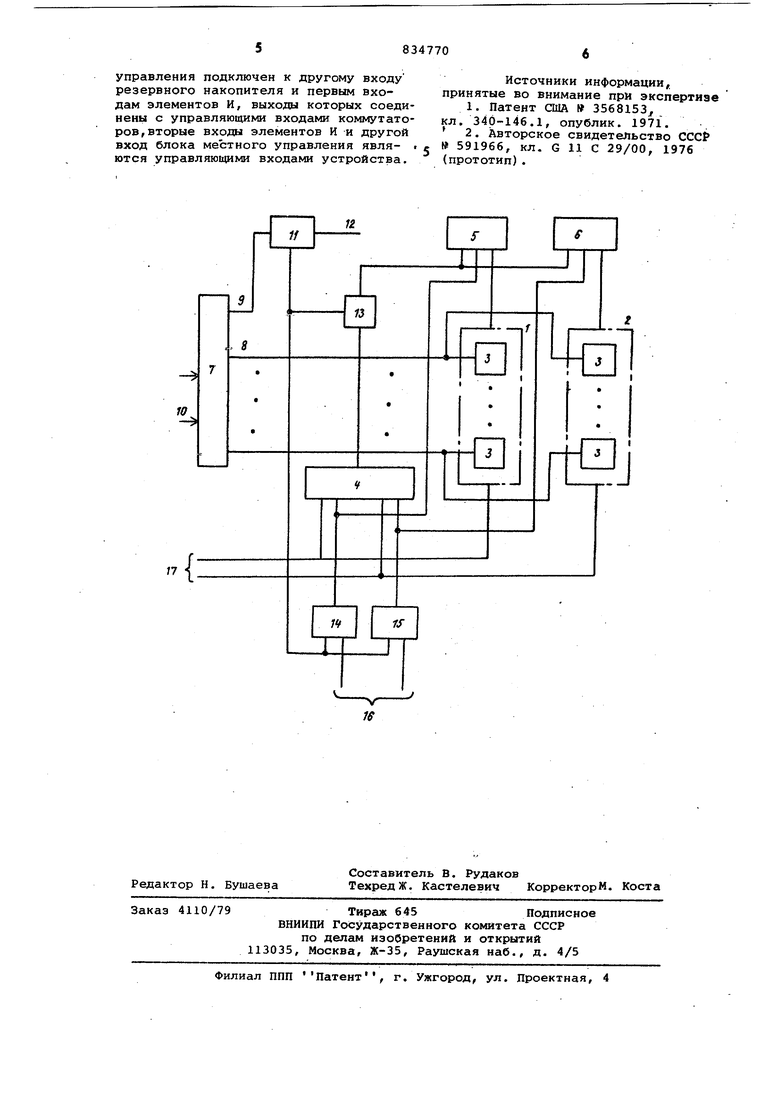

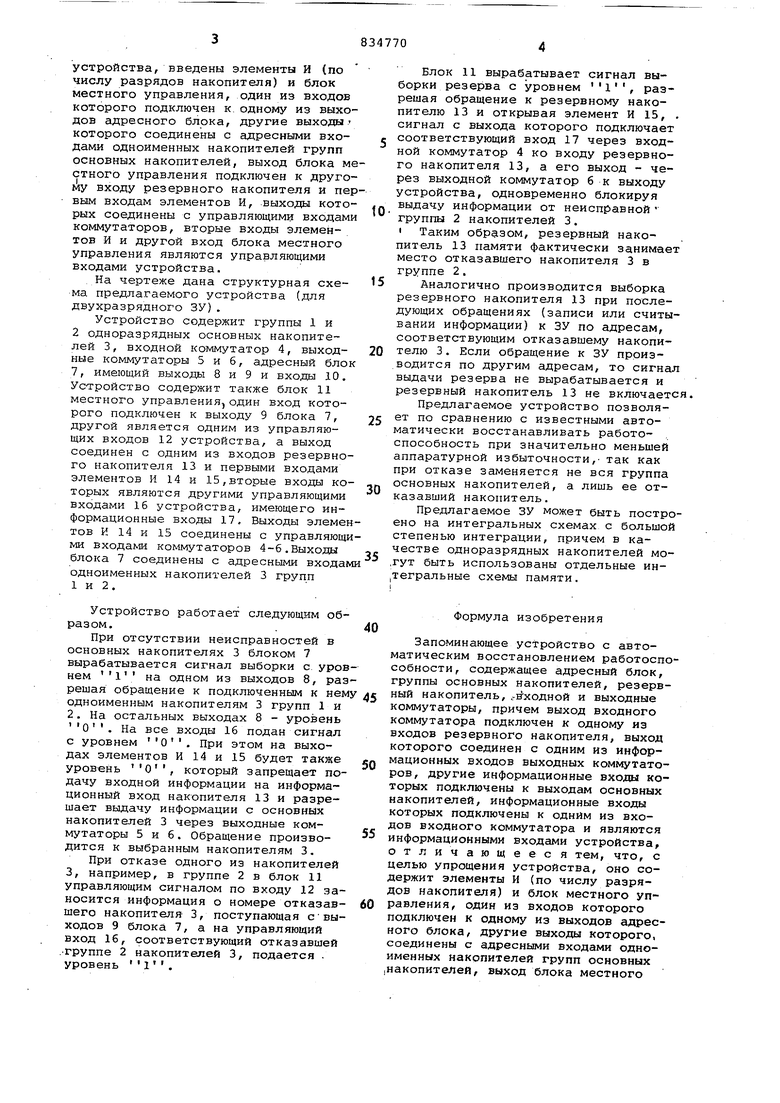

ял являются информационными входами устройства, введены элементы И (по числу разрядов накопителя) и блок местного управления, один из входов которого подключен к одному из выходов адресного блока, другие выходыкоторого соединены с адресными входами одноименных накопителей групп основных накопителей, выход блока ме стного управления подключен к другоiviy входу резервного накопителя и пер вым входам элементов И, выходы которых соединены с управляющими входами коммутаторов, вторые входы элементов И и другой вход блока местного управления являются управляющими входами устройства. На чертеже дана структурная схема предлагаемого устройства (для двухразрядного ЗУ). Устройство содержит группы 1 и 2 одноразрядных основных накопителей 3, входной коммутатор 4, выходные коммутаторы 5 и б, адресный бло 7, имеющий выходы 8 и 9 и входы 10. Устройство содержит также блок 11 местного управления, один вход которого подключен к выходу 9 блока 7, другой является одним из управляющих входов 12 устройства, а выход соединен с одним из входов резервно го накопителя 13 и первыми входами элементов И 14 и 15,вторые входы ко торых являются другими управляющими входами 16 устройства, имеющего информационные входы 17, Выходы элеме тов И 14 и 15 соединены с управляющ ми входами коммутаторов 4-6.Выходы блока 7 соединены с адресными входа одноименных накопителей 3 групп 1 и 2. Устройство работает следующим образом,. При отсутствии неисправностей в основных накопителях 3 блоком 7 вырабатывается сигнал выборки с уров нем I на одном из выходов 8, раз решая обращение к подключенным к нем одноименным накопителям 3 групп 1 и 2,На остальных выходах 8 - уровень О. На все входы 16 подан сигнал с уровнем О. При этом на выходах элементов И 14 и 15 будет также уровень О, который запрещает подачу входной информации на информационный вход накопителя 13 и разрешает выдачу информации с основных накопителей 3 через выходные коммутаторы 5 и 6. Обращение производится к выбранным накопителям 3. При отказе одного из накопителей 3,например, в группе 2 в блок 11 управляющим сигналом по входу 12 заносится информация о номере отказавшего накопителя 3, поступающая свыходов 9 блока 7, а на управляющий вход 16, соответствующий отказавшей .группе 2 накопителей 3, подается уровень . Блок 11 вырабатывает сигнал выборки резерва с уровнем , разрешая обращение к резервному накопителю 13 и открывая элемент И 15, , сигнал с выхода которого подключает соответствующий вход 17 через входной коммутатор 4 ко входу резервного накопителя 13, а его выход - через выходной коммутатор 6 к выходу устройства, одновременно блокируя выдачу информации от неисправной группы 2 накопителей 3. Таким образом, резервный накопитель 13 памяти фактически занимает место отказавшего накопителя 3 в группе 2. Аналогично производится выборка резервного накопителя 13 при последующих обращениях (записи или считывании информации) к ЗУ по адресам, соответствующим отказавшему накопителю 3, Если обращение к ЗУ производится по другим адресам, то сигнал выдачи резерва не вырабатывается и резервный накопитель 13 не включается. Предлагаемое устройство позволяет по сравнению с известными автоматически восстанавливать работоспособность при значительно меньшей аппаратурной избыточности,- так как при отказе заменяется не вся группа основных накопителей, а лишь ее отказавший накопитель. Предлагаемое ЗУ может быть построено на интегральных схемах с большой степенью интеграции, причем в качестве одноразрядных накопителей мо,гут быть использованы отдельные ин|Тегральные схемы памяти. Формула изобретения Запоминающее устройство с автоматическим восстановлением работоспособности, содержащее адресный блок, группы основных накопителей, резервный накопитель, .г -ходной и выходные коммутаторы, причем выход входного коммутатора подключен к одному из входов резервного накопителя, выход которого соединен с одним из информационных входов выходных коммутаторов, другие информационные входы которых подключены к выходам основных накопителей, информационные входы которых подключены к одним из входов входного коммутатора и являются информационными входами устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит элементы И (по числу разрядов накопителя) и блок местного управления, один из входов которого подключен к одному из выходов адресного блока, другие выходы которого, соединены с адресными входами одноименных накопителей групп основных ,накопитеЛей, выход блока местного

управления подключен к другому входу резервного накопителя и nepBtJM входам элементов И, выходы которых соединены с управляющими входами коммутаторов, вторые входы элементов И и другой вход блока местного управления явля- с ются управляющими входами устройства.

Источники информации, принятые во внимание при экспертиэе

1.Патент США № 3568153 кл. 340-146.1, опублик. 1971,

2.Авторское свидетельство СССР № 591966, кл. G 11 С 29/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1981 |

|

SU1018152A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1981 |

|

SU972599A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1144153A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство | 1980 |

|

SU903973A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| ЗАПОМИНАНМЦЕЕ УСТРОЙСТВО С БЛОШРОВКОЙ НЕИСПРАВНЫХ ЯЧЕЕК ПАМЯТИ | 1979 |

|

SU826425A1 |

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| Многоканальный резервированный коммутатор | 1989 |

|

SU1737723A1 |

Авторы

Даты

1981-05-30—Публикация

1979-09-17—Подача