Изобретение относится к вычислительной технике, в частности к области запоминающих устройств.

Цель изобретения - повышение надежности устройства.

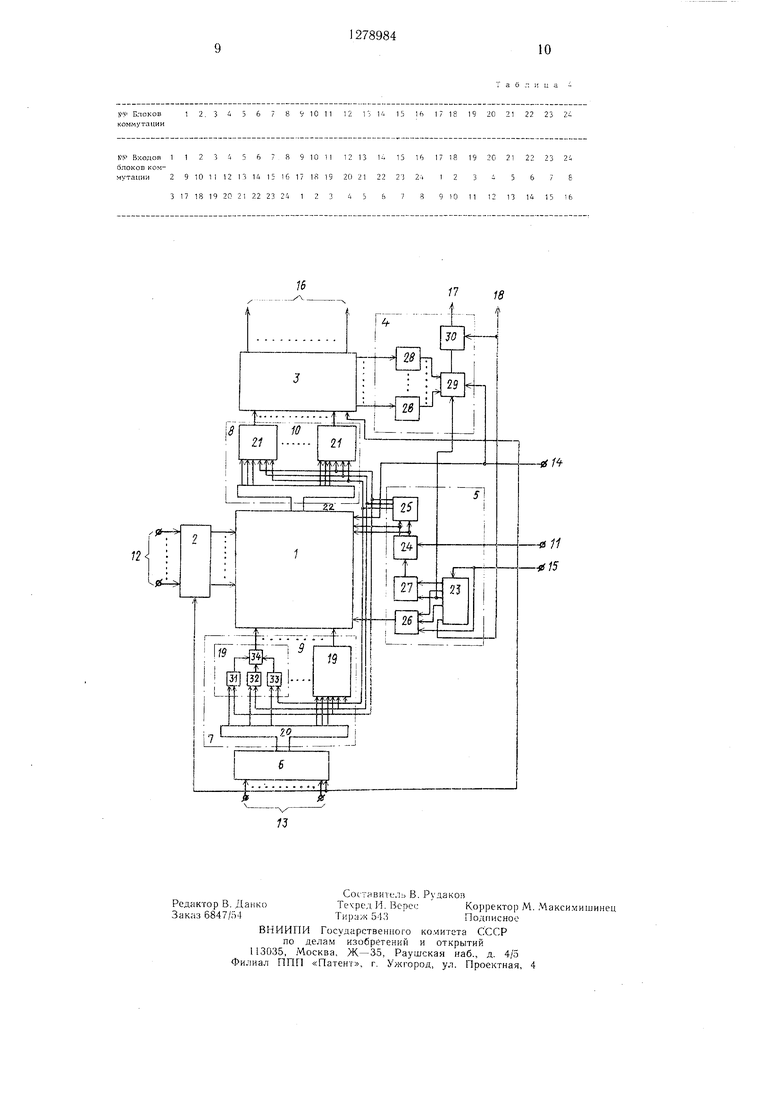

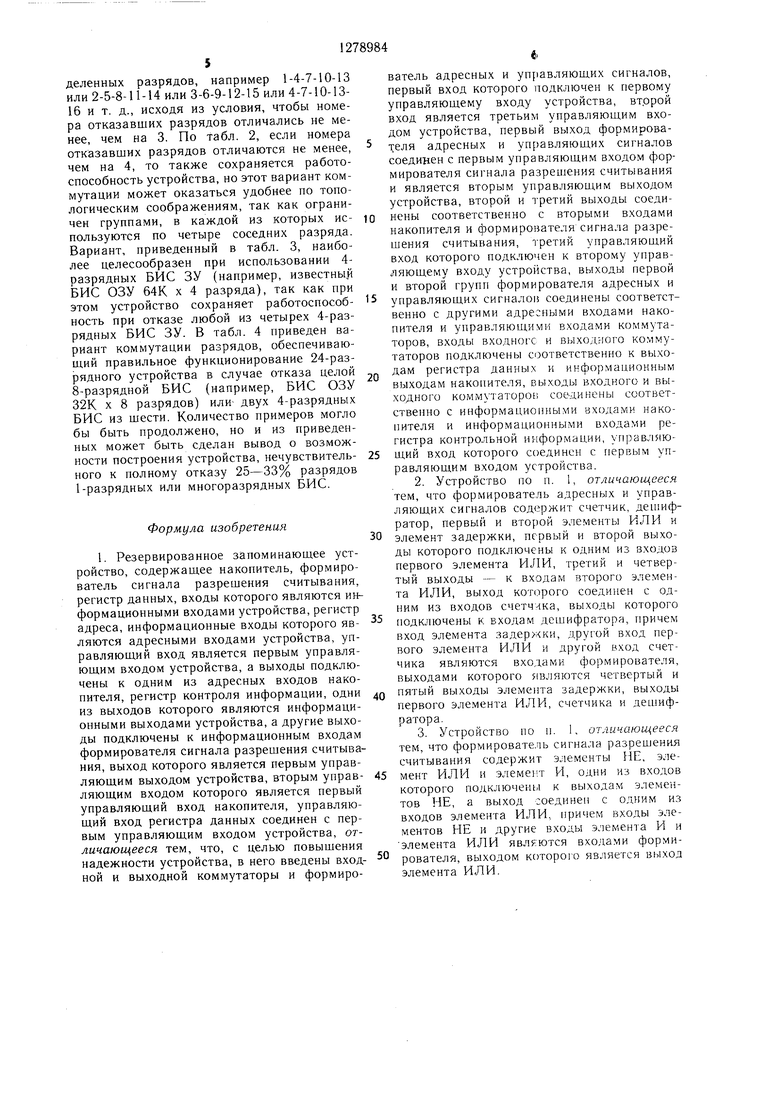

На чертеже изображена структурная схема устройства.

Устройство содержит накопитель 1, имеющий информационную емкость, в четыре раза превыщающую требуемую для решения задач, регистр 2 адреса, регистр 3 контро- ля информации, формирователь 4 сигнала разрешения считывания, формирователь 5 адресных и управляющих сигналов, регистр 6 данных, входной 7 и выходной 8 коммутаторы, выходы 9 и 10 которых подключены соответственно к информационным входам накопителя 1 и регистра 3.

Устройство имеет первый управляющий вход 11, адресные 12 и информационные 13 входы, второй 14 и третий 15 управляю- щие входы, информационные выходы 16, первый 17 и второй 18 управляющие выходы.

Входной коммутатор 7 содержит k блоков 19 коммутации входных данных и щину 20 входных данных (где k - разрядность данных).

Выходной коммутатор 8 содержит k блоков 21 коммутации выходных данных, идентичных блокам 19, и шину 22 выходных данных.

Формирователь 5 содержит элемент 23 задержки, счетчик 24, дешифратор 25, первый 26 и второй 27 элементы ИЛИ.

Формирователь 4 содержит элементы НЕ 28, элемент И 29 и элемент ИЛИ 30.

Каждый из блоков 19 и 21 содержит первый 31, второй 32 и третий 33 элементы И и элемент ИЛИ 34.

Устройство работает следующим образом.

При каждом обращении к устройству сигналом начальной установки с входа 11 происходит установка в исходное состояние регистров 2, 3 и 6 и счетчика 24, после чего происходит запись в регистры 2 и 6 соответственно кодов адреса и входных данных с входов 12 и 13. После установления на адресных входах каждой БИС ЗУ (не показаны) накопителя 1 кода адреса с выходов регистра 2 и счетчика 24, признака записи или считывания с вхоДа 14 арифметическое устройство (не показано) вырабатывает управляющий сигнал, который с входа 15 через первый элемент ИЛИ 26 поступает на вход выбора кристалла каждой БИС ЗУ накопителя 1. При этом производится запись информации в соответствующий адрес первой четверти накопителя 1 или считывание информации из соответствующего адреса. По истечении времени, равного вре- мени цикла обращения к накопителю 1, произойдет обращение к одноименному адресу второй четверти накопителя, так как задер

о

5

g

5

0

жанный на элементе 23 задержки управляющий сигнал через элемент ИЛИ 27 переключит счетчик 24 в следующее состояние, после чего через элемент ИЛИ 26 поступит на входы выбора кристалла всех БИС ЗУ накопителя 1. По истечении ещ одного времени цикла накопителя 1 произойдет обращение к одноименному адресу третьей четверти накопителя, так как задержанный на элементе 23 задержки управляющий сигнал переведет счетчик 24 в очередное состояние и затем поступит на вход выбора кристалла каждой БИС ЗУ накопителя 1. По истечении третьего цикла обращения к накопителю 1, определяемого еще одной задержкой управляющего сигнала на элементе 23 задержки, на выходе 18 устройства установится сигнал готовности устройства к последую- UWM обращениям.

Таким образом, за время одного обращения к устройству со стороны арифметического устройства произойдет три обращения к накопителю 1, в результате которых одни и те же входные данные окажутся занесенными в три одноименных адреса трех четвертей накопителя или будет считана информация из трех одноименных адресов, относящихся к разным трем четвертям накопителя.

Рассмотрим особенности преобразования данных перед их записью в адреса накопителя 1.

Записываемая в накопитель 1 информация из регистра 6 через шину 20 входных данных поступает на входы блоков 19 коммутации входных данных. При этом, каждый разряд 1-k шины 20 входных данных соединен с первым входом одного из блоков 19 коммутации, вторым входом другого и третьим входом какого-либо из оставшихся блоков 19 коммутации.

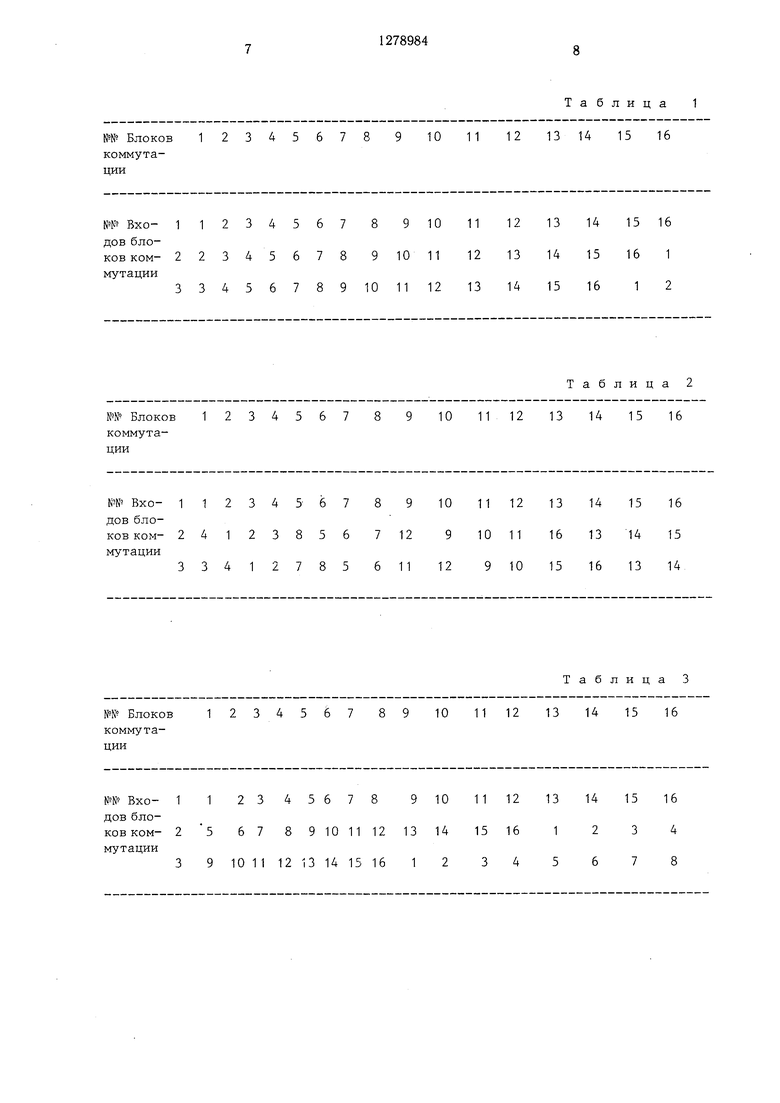

В результате к первому, второму и третьему входам каждого из блоков 19 коммутации оказываются подключенными три разноименных разряда шины 20. Имеется больщое число возможных вариантов коммутации разрядов входных данных. Некоторые из этих вариантов в качестве примера приведены в табл. 1-4, где номера блоков коммутации поставлены в соответствие с номерами разрядов накопителя, входных и выходных данных, а номера входов блоков коммутации оказываются соответствующими первой, второй или третьей четвертям накопителя. Это соответствие задается сигналами с выходов дешифратора 25, управляемого счетчиком 24. При обра цении к первой четверти накопителя дешифрированный сигнал с выхода дешифратора 25 поступает на первые управляюн ие входы каждого из блоков 19 коммутации данных, разреп ая прохождение входных данных с шины 20 на входы накопителя 1 через элементы И 31 и элементы ИЛИ 34. При обращении к второй

четверти накопителя на входы накопителя поступают входные данные по цепи: шина 20, элементы -И 32, элементы ИЛИ 34 и т. д. Поскольку в режиме записи на вход накопителя 1 подан признак «Запись (низкий уровень) с входа 14, произойдет за- пись информации в три четверти накопителя 1. Вследствие того, что к первым трем входам каждого блока 19 коммутации входных данных подключены три разноименных разряда входных данных, в каждом разряде накопителя 1 по трем его четвертям окажется записанной информация, соответствующая информационному содержанию трех разноименных разрядов входных данных, а информация, содержащаяся в каждом разряде данных, окажется записанной в трех четвертях накопителя 1 по трем разноименным его разрядам.

При считывании информации на вход1 1 .устройства будут поданы те же сигналы от арифметического устройства, но на вход 14, а следовательно, и на вход накопителя 1 поступит считывания (высокий уровень). По каждому коду адреса на входах 12 произойдет считывание информации последовательно из трех четвертей накопителя, что определяется рассмотренным алгоритмом работы блока управления. Считанная из накопителя 1 информация через шину 22 выходных данных поступает на первый, второй и третий входы каждого блока 21 коммутации выходных данных, на управляющие входы каждого из которых поступают управляющие сигналы от дешифратора 25, аналогично тому, как это было описано при объяснении принципа действия блоков 19 коммутации входных данных. Подсоединение входов блока 21 коммутации выходных данных к шине 22 йыходных дан- ных также полностью идентично рассмотрен,- ному для блоков 19 коммутации входных данных. Поэтому при считывании информации из одноименных адресов первой, второй и. третьей четвертей накопителя 1 на каждый вход регистра 3 поступает из трех разноименных разрядов накопителя 1 та же информация, что и ранее поданная на соответствующие входы регистра 6 в режиме записи по те.м же адресам.

В процессе счипывания из первой четверти накопителя 1 информация записывается в регистре 3, каждый разряд которого представляет собой 2-разрядный счетчик. В зависимости от содержания считанной информации, первый разряд каждого 2-разрядного счетчика переключается или не переключается. В процессе считывания из второй четверти накопителя возможны два варианта функционирования устройства:

1. Информация при первом и втором считывании совпадает. Тогда на младцшх разрядах каждого из 2-разрядных счетчиков регистра 3 устаь явливается сигнал логического нуля. Этот сигнал от всех разрядов

5

5

0

n

0

0

5

0

5

регистра 3 поступает на входы формирователя 44 и через элементы НЕ 28 на один из входов элемента И 29, на другой вход которого подан признак считывания. По истечении времени, превышающего время выборки информации из накопителя 1 при втором обращении, на вход элемента И 29 от элемента 23 поступит сигнал, который вызовет срабатывание элемента И 29 и следом за ним элемента ИЛИ 30. На выходе 17 устройства появится сигнал «разрешение считывания информации, которая устанавлива- гтся после второго обращения на старших разрядах 2-разрядных счетчиков регистра 3, соединенных с информационными выходами 16 устройства. Поскольку эта информация, проверенная сравнением при считывании из двух четвертей накопителя, признается истинной, она может быть использована процессором. Сигнал «Готовность к последующему обращению будет сформирован элементом 23 задержки и появится на выходе 18 устройства после третьего считывания из накопителя 1, результаты которого в этом случае не оказывают влияния на считанную ранее информацию, а сигнал «Разрешение считывания на выходе 17 подтверждается сигналом «Готовность через элемент ИЛИ 30.

2. Информация при первом и втором обращениях не совпадает в одном или нескольких информационных разрядах, что является признаком неисправности накопителя 1. При этом после второго считывания на выходах младших разрядов соответствующих 2-разрядных счетчиков регистра 3 установится логическая единица. Инверсия этого сигнала на одном или нескольких элементах НЕ 28 приводит к тому, что после завершения второго считывания сигнал с элемента задержки 23 не приведет к срабатыванию элемента И 29 и на выходе 17 устройства сигнал «Разрешение считывания не появится. После третьего считывания произойдет подтверждение информации, полученной при первом или втором считывании, на старших разрядах всех 2-разрядных счетчиков регистра 3 и выходах 16 устройства установится информация, соответствующая истинной по мажоритарному принципу. После завершения третьего считывания на выходах 17 и 18 устройства одновременно появятся соответственно сигналы «Разрешение считывания и «Готовность.

Из рассмотрения изложенного принципа действия предлагаемого устройства следует, что устройство становится нечувствительным к отказу целого разряда накопителя (разряд многоразрядной БИС ЗУ, целая 1-разрядная БИС ЗУ). В зависимости от способов коммутации этот эффект может быть значительно усилен. Так, коммутация в соответствии с табл. 1 обеспечивает сохранение работоспособности устройства при полном отказе нескольких, но вполне определенных разрядов, например 1-4-7-10-13 или 2-5-8-11-14 или 3-6-9-12-15 или 4-7-10-13- 16 и т. д., исходя из условия, чтобы номера отказавших разрядов отличались не менее, чем на 3. По табл. 2, если номера отказавших разрядов отличаются не менее, чем на 4, то также сохраняется работоспособность устройства, но этот вариант коммутации может оказаться удобнее по топологическим соображениям, так как ограничен группами, в каждой из которых ис- пользуются по четыре соседних разряда. Вариант, приведенный в табл. 3, наиболее целесообразен при использовании 4- разрядных БИС ЗУ (например, известный БИС ОЗУ 64К X 4 разряда), так как при этом устройство сохраняет работоспособ- ность при отказе любой из четырех 4-разрядных БИС ЗУ. В табл. 4 приведен вариант коммутации разрядов, обеспечиваю- ший правильное функционирование 24-разрядного устройства в случае отказа целой 8-разрядной БИС {например, БИС ОЗУ 32К X 8 разрядов) или- двух 4-разрядных БИС из шести. Количество примеров могло бы быть продолжено, но и из приведенных может быть сделан вывод о возможности построения устройства, нечувствитель- ного к полному отказу 25-33% разрядов 1-разрядных или многоразрядных БИС.

Формула изобретения

1. Резервированное запоминающее устройство, содержащее накопитель, формирователь сигнала разрешения считывания, регистр данных, входы которого являются информационными входами устройства,регистр

30

2. Устройство по п. 1, отличающееся тем, что формирователь адресных и управляющих сигналов содержит счетчик, дешиф ратор, первый и второй элементы ИЛИ и элемент задержки, первый и второй выходы которого подключены к одним из входов первого элемента ИЛИ, третий и четвертый выходы - к входам второго элемента ИЛИ, выход которого соединен с одним из входов счетчдка, выходы которого

адреса, информационные входы которого яв- подключены к входам дешифратора, причем

ляются адресными входами устройства, управляющий вход является первым управляющим входом устройства, а выходы подключены к одним из адресных входов накопителя, регистр контроля информации, одни из выходов которого являются информационными выходами устройства, а другие выходы подключены к информационным входам формирователя сигнала разрещения считывания, выход которого является первым управляющим выходом устройства, вторым управ- ляющим входом которого является первый управляющий вход накопителя, управляющий вход регистра данных соединен с первым управляющим входом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены вход- ной и выходной коммутаторы и формироп 5

0

ватель адресных и управляющих сигналов, первый вход которого подключен к первому управляющему входу устройства, второй вход является третьим управляющим входом устройства, первый выход формирователя адресных и управляющих сигналов соединен с первым управляющим входом формирователя сигнала разрешения считывания и является вторым управляющим выходом устройства, второй и третий выходы соединены соответственно с вторыми входами накопителя и формирователя сигнала разрешения считывания, третий управляющий вход которого подключен к второму управляющему входу устройства, выходы первой и второй групп формирователя адресных и управляющих сигналов соединены соответственно с другими адресными входами накопителя и управляюп;ими входами коммутаторов, входы входногс и выходного коммутаторов подключены соответственно к выходам регистра данных и информационным выходам накопителя, выходы входного и выходного коммутаторОЕ соединены соответственно с информационными входами накопителя и информационными входами регистра контрольной информации, управляющий вход которого соединен с первым управляющим входом устройства.

2. Устройство по п. 1, отличающееся тем, что формирователь адресных и управляющих сигналов содержит счетчик, дешифратор, первый и второй элементы ИЛИ и элемент задержки, первый и второй выходы которого подключены к одним из входов первого элемента ИЛИ, третий и четвертый выходы - к входам второго элемента ИЛИ, выход которого соединен с одним из входов счетчдка, выходы которого

- подключены к входам дешифратора, причем

вход элемента задержки, другой вход первого элемента ИЛИ и другой вход счетчика являются входами формирователя, выходами которого являются четвертый и пятый выходы элемента задержки, выходы первого элемента ИЛИ, счетчика и дешифратора.

3. Устройство по п. 1, отличающееся тем, что формирователь сигнала разрешения считывания содержит элементы НЕ, элемент ИЛИ и элеме1гг И, одни из входов которого подключены к выходам элементов НЕ, а выход соединен с одним из входов элемента ИЛИ, причем входы элементов НЕ и другие входы элемента И и элемента ИЛИ являются входами формирователя, выходом которого является выход элемента ИЛИ.

№№ Блоков 12345678 9 10 11 12 13 14 15 16 коммутации

№ Вхо- 11234567 8 910 11 12 13 14 1516 дов блоков ком- 22345678 91011 12 13 14 15 16 1 мутации

3 3 4 5 6 7 8 9 10 11 12 13 14 15 161 2

Таблица 2

№№ Блоков 1234567 8 9 10 1112 13 14 15 16 коммутации

т Вхо- 112345-67 8 9 10 11 12 13 14 15 16 дов блоков ком- 24123856 7 12 9 10 11 16 13 14 15 мутации

33412785 6 11 12 9 10 15 16 13 14

т Блоков 1234567 89 10 11 12 13 14 15 16 коммутации

№№ Вхо- 1 1 2345678 910 11 12 13 14 15 16 дов блоков ком- 2 5 67891011121314 15 1612 3 4 мутации

3 9 10 1 1 12 13 14 15 16 1 2 3 4 5 6 7 8

Таблица 1

Таблица 3

S V БлоковI 2.3 4 5 6 7 8 VIOIl 12 )

коммутации

1 1 2 3 4 5 6 7 8 9 10 11 12 П li 15 И) 17 18 19 20 21 22 23 2i 2 9 10 1 1 12 1 3 14 15 16 17 18 19 20 21 22 23 2- i I 2 3

i 5 6 7 8 7 8 910 11 12 13 14 13 16

3 17 18 19 20 2 I 22 23 24 1 2

15 16 17 18 19 20 21 22

15 И) 17 18 19 20 21 22 23 2i 3 2- i I 2 3

i 5 6 7 8 7 8 910 11 12 13 14 13 16

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1522292A1 |

Изобретение относится к вычислительной технике, в частности к заноминаюшим ycTpoftcTBajM. Цель изобретения - повышение надежности устройства. Резервированное запоминающее устройство содержит накопитель, регистр адреса, регистр данны.х, входной и выходной коммутаторы, регистр контрольной информации, формирователь сигнала разрешения считывания и формирователь адресных и управляюш.их сигналов. Надежность устройства повышается за счет введения коммутации разрядов входных и вы ходных данных накопителя в трех его четвертях, запись и считывание в которых производятся последовательно в трех тактах при одном обращении к устройству от арифметического устройства, что обеспечивает обнаружение и исправление ошибок, возникающих вследствие отказа отдельных ячеек, строк, столбцов, целого разряда или целой БИС ЗУ накопителя. 2 з.п. ф-лы, 1 ил., 4 табл. ю 00 со 00 4

| Запоминающее устройство с самоконтролем | 1980 |

|

SU951406A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-05—Подача