Изобретение относится к вычислительной технике, в частности к запоминающим устройствам с последовательной выборкой информации (накопители на магнитных лентах, магнитных дисках, магнитных барабанах, цилиндрических магнитных доменах (ЦМД) и приборах с зарядовой связью).

Известно резервированное запоминающее устройство, содержащее основные и резервные накопители и блок управления 1.

Недостатками этого устройства являются больщая аппаратурная избыточность (100%) и невозможность защиты информации при отказе второго (резервного) накопителя.

Наиболее близким по технической сущности к изобретению является резервированное запоминающее устройство, содержащее основные и один резервный накопители, формирователь четности, блок управления, сумматор по модулю два, входы формирователя четности соединены с входом резервного накопителя, входы сумматора по модулю два соединены с выходами основных и резервного накопителей, а его выход является выходом устройства, входами которого являются входы основных накопителей 2.

Недостатком известного устройства является низкая надежность, так как в нем не обеспечена защита информации при отказе двух накопителей одновременно.

Цель изобретения - повыщение надежности устройства.

Поставленная цель достигается тем, что в резервированное запоминающее устройство, содержащее основные и первый резервный накопители данных, первый формирователь сигналов четности и блок управления, введены блок восстановления информации, накопители контрольной информации, преобразователь кодов, блок местного управления, второй формирователь сигналов четности, коммутаторы, формирователь сигналов нечетности, второй резервный накопитель данных, элементы ИЛИ, элемент И, элемент НЕ и элемент ЗАПРЕТ, причем одни из входов и выходов первого коммутатора являются входами и выходами устройства, а другие входы и выходы соединены соответственно с одними из выходов и входов блока управления и с одними из выходов и входов блока местного управления, другие входы и выходы которого подключены к выходам и входам основных и резервных накопителей данных, другие входы и выходы блока управления соединены с одними из выходов и входов блока восстановления информации, другие выход и вход которого подключены соответственно к первому входу второго коммутатора и к выходу третьего коммутатора, управляющие выходы блока восстановления информации соединены соответственно с входами первой группы и с управляющим входом третьего коммутатора, с адресными и с управляющими входами накопителей контрольной информации, с управляющими входами преобразователя кодов и с управляющими входами второго коммутатора, выходы которого подключены к информационным входам накопителей контрольной информации, одни из выходов которых соединены с входами второй группы третьего коммутатора, одними из входов первого формирователя сигналов четности и одними из входов преобразователя кодов, другие выходы накопителей контрольной информации подключены соответственно к первому входу третьего коммутатора и другому входу первого формирователя сигналов четности, к второму входу третьего коммутатора, к третьему входу третьего коммутатора, первому входу элемента И и первому входу элемента ЗАПРЕТ, второй вход которого соединен с выходом первого формирователя сигналов четности и входом элемента НЕ, выход которого подключен к второму входу элемента И, выход которого соединен с первым входом первого -элемента ИЛИ, второй вход которого подключен к выходу элемента ЗАПРЕТ, а выход - ко второму входу второго коммутатора и другому входу преобразователя кодов, одни

d из выходов которого соединены с входами второго формирователя сигналов четности, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с третьим входом второго коммутатора, а второй вход - с выходом формирователя сигналов нечетности, входы которого и группа входов второго коммутатора подключены к другим выходам преобразователя кодов.

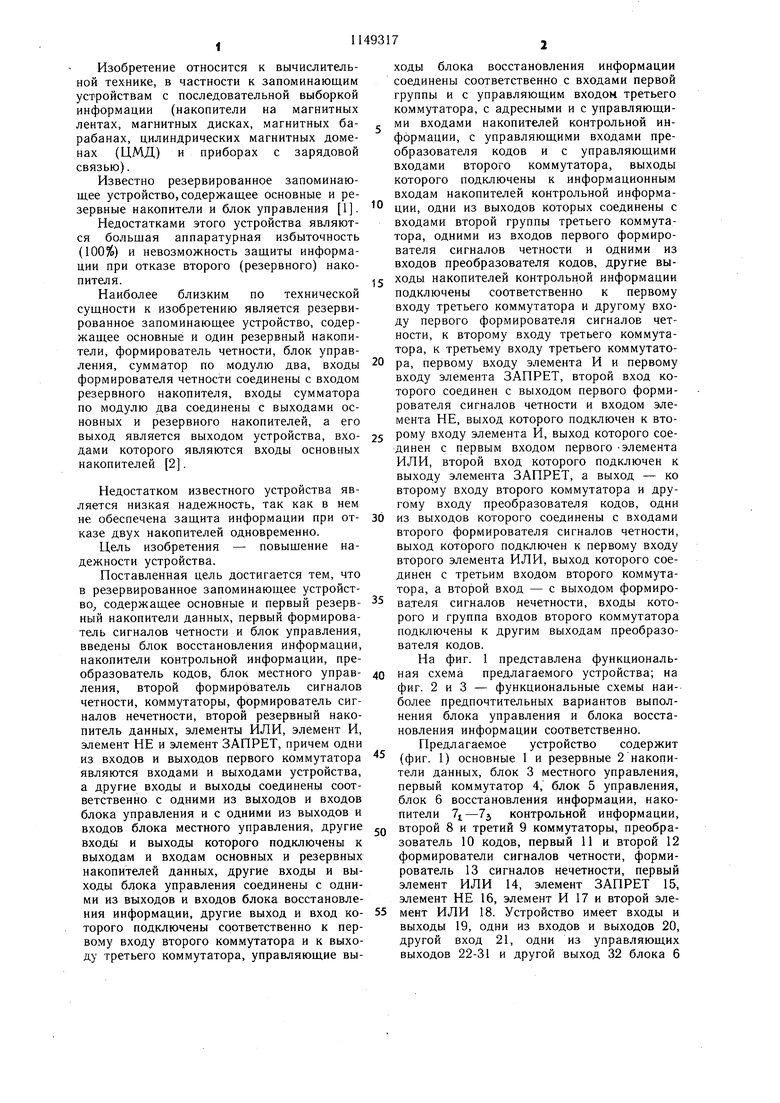

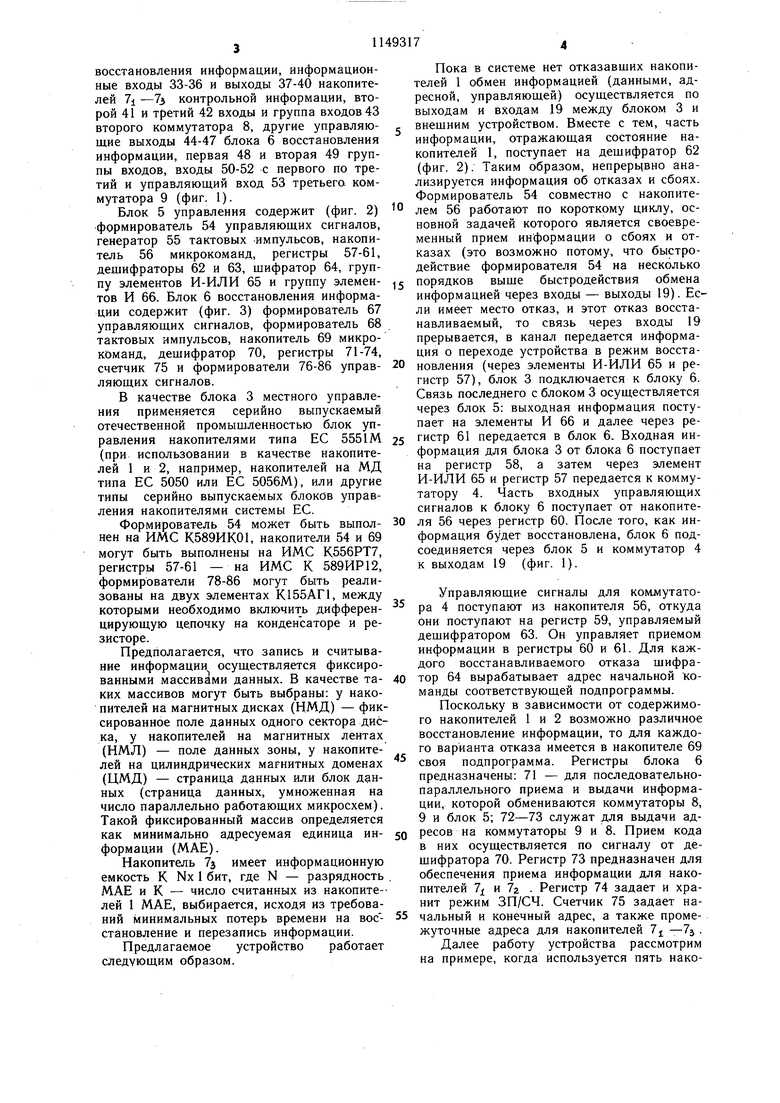

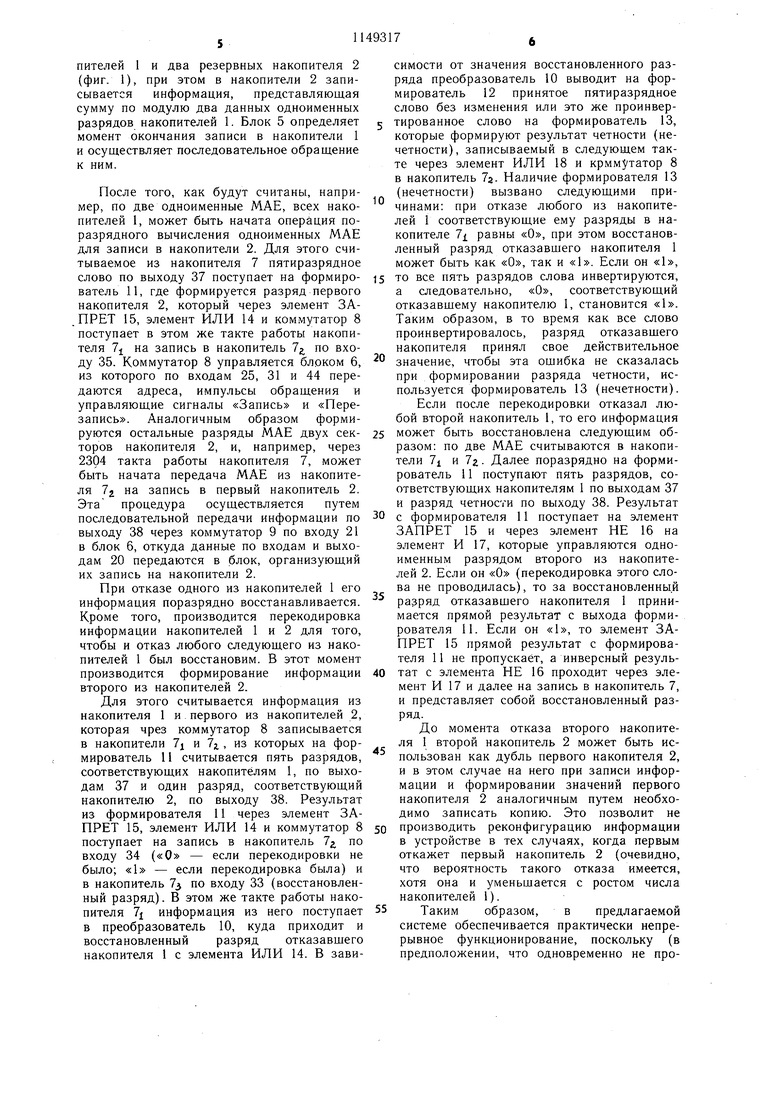

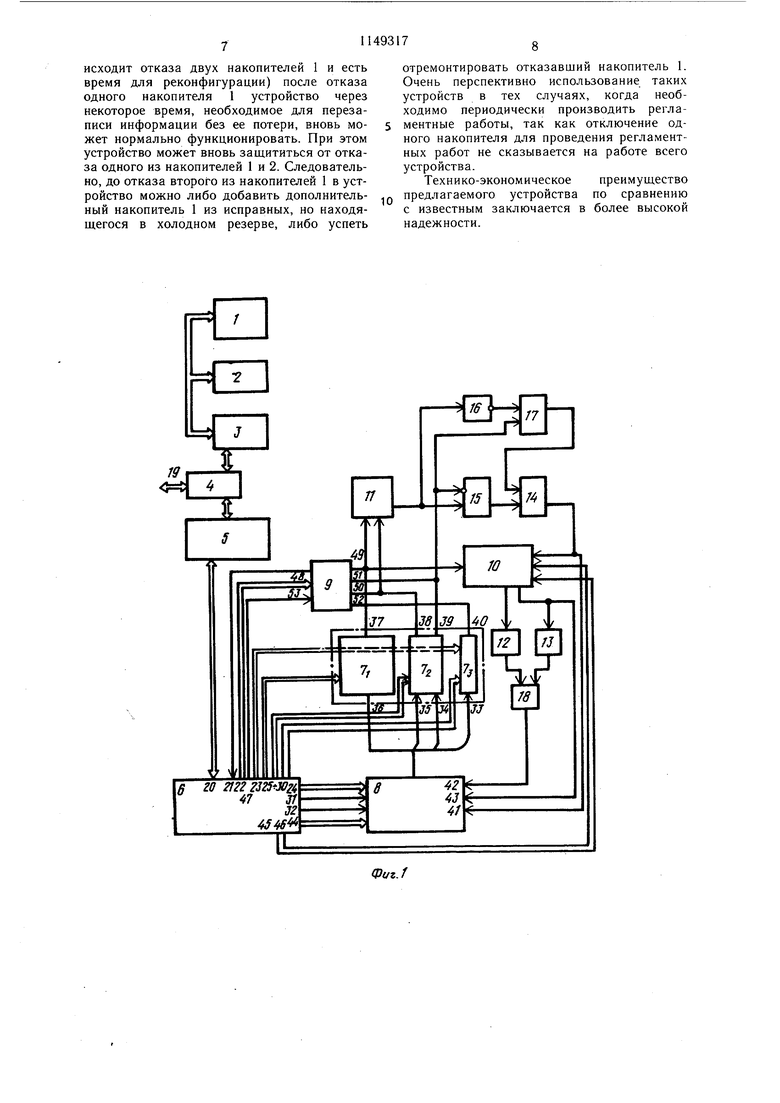

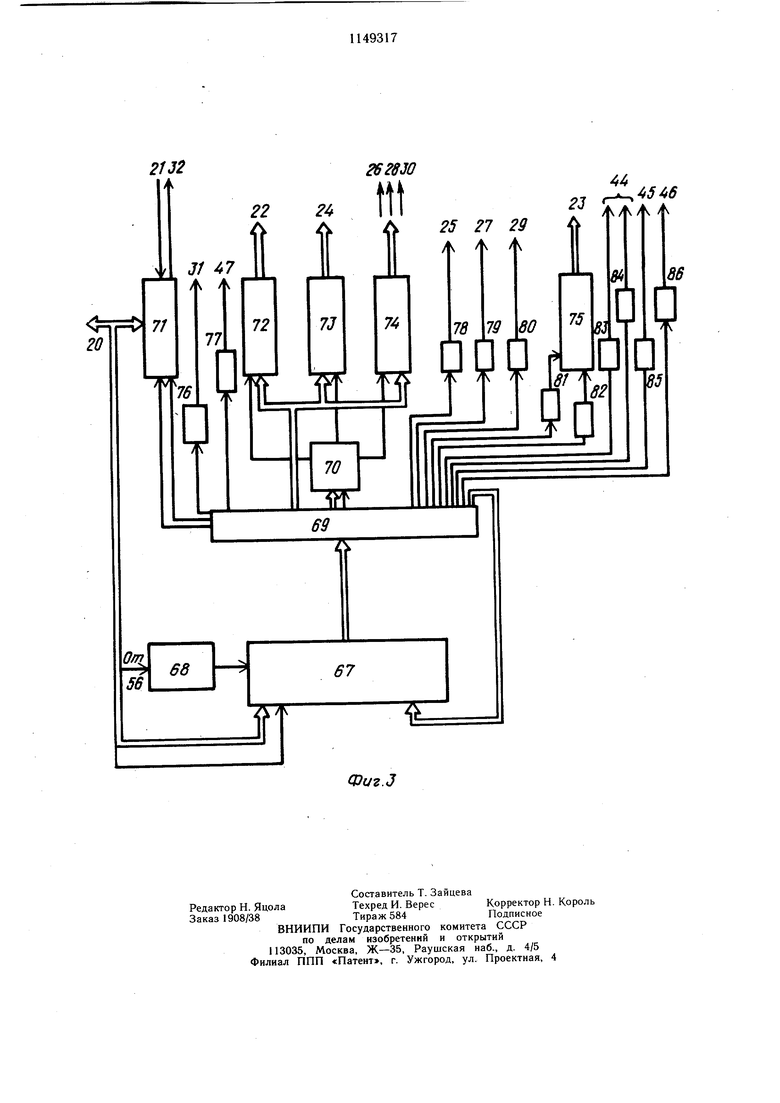

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 и 3 - функциональные схемы наиболее предпочтительных вариантов выполнения блока управления и блока восстановления информации соответственно.

Предлагаемое устройство содержит

(фиг. 1) основные 1 и резервные 2 накопители данных, блок 3 местного управления, первый коммутатор 4, блок 5 управления, блок 6 восстановления информации, накопители 7i-7з контрольной информации,

0 второй 8 и третий 9 коммутаторы, преобразователь 10 кодов, первый 11 и второй 12 формирователи сигналов четности, формирователь 13 сигналов нечетности, первый элемент ИЛИ 14, элемент ЗАПРЕТ 15, элемент НЕ 16, элемент И 17 и второй элемент ИЛИ 18. Устройство имеет входы и выходы 19, одни из входов и выходов 20, другой вход 21, одни из управляющих выходов 22-31 и другой выход 32 блока 6

восстановления информации, информационные входы 33-36 и выходы 37-40 накопителей 7i -7з контрольной информации, второй 41 и третий 42 входы и группа входов 43 второго коммутатора 8, другие управляющие выходы 44-47 блока 6 восстановления информации, первая 48 и вторая 49 группы входов, входы 50-52 с первого по третий и управляющий вход 53 третьего коммутатора 9 (фиг. 1).

Блок 5 управления содержит (фиг. 2) формирователь 54 управляющих сигналов, генератор 55 тактовых импульсов, накопитель 56 микрокоманд, регистры 57-61, дешифраторы 62 и 63, шифратор 64, группу элементов И-ИЛИ 65 и группу элементов И 66. Блок 6 восстановления информации содержит (фиг. 3) формирователь 67 управляющих сигналов, формирователь 68 тактовых импульсов, накопитель 69 микрокоманд, дешифратор 70, регистры 71-74, счетчик 75 и формирователи 76-86 управляющих сигналов.

В качестве блока 3 местного управления применяется серийно выпускаемый отечественной промышленностью блок управления накопителями типа ЕС 5551М (при использовании в качестве накопителей 1 и 2, например, накопителей на МД типа ЕС 5050 или ЕС 5056М), или другие типы серийно выпускаемых блоков управления накопителями системы ЕС.

Формирователь 54 может быть выполнен на ИМС К589ИК01, накопители 54 и 69 могут быть выполнены на ИМС К556РТ7, регистры 57-61 - на ИМС К 589ИР12, формирователи 78-86 могут быть реализованы на двух элементах К155АГ1, между которыми необходимо включить дифференцирующую цепочку на конденсаторе и резисторе.

Предполагается, что запись и считывание информации осуществляется фиксированными массивами данных. В качестве таких массивов могут быть выбраны: у накопителей на магнитных дисках (НМД) - фиксированное поле данных одного сектора диска, у накопителей на магнитных лентах (НМЛ) - поле данных зоны, у накопителей на цилиндрических магнитных доменах (ЦМД) - страница данных или блок данных (страница данных, умноженная на число параллельно работающих микросхем). Такой фиксированный массив определяется как минимально адресуемая единица информации (МАЕ).

Накопитель 7з имеет информационную емкость К NX 1 бит, где N - разрядность МАЕ и К - число считанных из накопителей 1 МАЕ, выбирается, исходя из требований минимальных потерь времени на воестановление и перезапись информации.

Предлагаемое устройство работает следующим образом.

Пока в системе нет отказавших накопителей 1 обмен информацией (данными, адресной, управляющей) осуществляется по выходам и входам 19 между блоком 3 и внешним устройством. Вместе с тем, часть информации, отражающая состояние накопителей 1, поступает на дешифратор 62 (фиг. 2). Таким образом, непрерывно анализируется информация об отказах и сбоях. Формирователь 54 совместно с накопителем 56 работают по короткому циклу, основной задачей которого является своевременный прием информации о сбоях и отказах (это возможно потому, что быстродействие формирователя 54 на несколько порядков выше быстродействия обмена информацией через входы - выходы 19). Если имеет место отказ, и этот отказ восстанавливаемый, то связь через входы 19 прерывается, в канал передается информация о переходе устройства в режим восстановления (через элементы И-ИЛИ 65 и регистр 57), блок 3 подключается к блоку 6. Связь последнего с блоком 3 осуществляется через блок 5: выходная информация поступает на элементы И 66 и далее через регистр 61 передается в блок 6. Входная информация для блока 3 от блока 6 поступает на регистр 58, а затем через элемент И-ИЛИ 65 и регистр 57 передается к коммутатору 4. Часть входных управляющих сигналов к блоку 6 поступает от накопителя 56 через регистр 60. После того, как информация будет восстановлена, блок 6 подсоединяется через блок 5 и коммутатор 4 к выходам 19 (фиг. 1).

Управляющие сигналы для коммутатора 4 поступают из накопителя 56, откуда они поступают на регистр 59, управляемый дещифратором 63. Он управляет приемом информации в регистры 60 и 61. Для каждого восстанавливаемого отказа шифратор 64 вырабатывает адрес начальной команды соответствующей подпрограммы.

Поскольку в зависимости от содержимого накопителей 1 и 2 возможно различное восстановление информации, то для каждого варианта отказа имеется в накопителе 69 своя подпрограмма. Регистры блока 6 предназначены: 71 - для последовательнопараллельного приема и выдачи информации, которой обмениваются коммутаторы 8, 9 и блок 5; 72-73 служат для выдачи адресов на коммутаторы 9 и 8. Прием кода в них осуществляется по сигналу от дешифратора 70. Регистр 73 предназначен для обеспечения приема информации для накопителей 7 и 7г . Регистр 74 задает и хранит режим ЗП/СЧ. Счетчик 75 задает начальный и конечный адрес, а также промежуточные адреса для накопителей 7 7з .

Далее работу устройства рассмотрим на примере, когда используется пять накопителей 1 и два резервных накопителя 2 (фиг. 1), при этом в накопители 2 записывается информация, представляющая сумму по модулю два данных одноименных разрядов накопителей 1. Блок 5 определяет момент окончания записи в накопители 1 и осуществляет последовательное обращение к ним.

После того, как будут считаны, например, по две одноименные МАЕ, всех накопителей 1, может быть начата операция поразрядного вычисления одноименных МАЕ для записи в накопители 2. Для этого считываемое из накопителя 7 пятиразрядное слово по выходу 37 поступает на формирователь 11, где формируется разряд первого накопителя 2, который через элемент ЗА. ПРЕТ 15, элемент ИЛИ 14 и коммутатор 8 поступает в этом же такте работы накопителя 7i на запись в накопитель 7 по входу 35. Коммутатор 8 управляется блоком 6, из которого по входам 25, 31 и 44 передаются адреса, импульсы обращения и управляющие сигналы «Запись и «Перезапись. Аналогичным образом формируются остальные разряды МАЕ двух секторов накопителя 2, и, например, через 2304 такта работы накопителя 7, может быть начата передача МАЕ из накопителя 7 на запись в первый накопитель 2. Эта процедура осуществляется путем последовательной передачи информации по выходу 38 через коммутатор 9 по входу 21 в блок 6, откуда данные по входам и выходам 20 передаются в блок, организующий их запись на накопители 2.

При отказе одного из накопителей 1 его информация поразрядно восстанавливается. Кроме того, производится перекодировка информации накопителей 1 и 2 для того, чтобы и отказ любого следующего из накопителей 1 был восстановим. В этот момент производится формирование информации второго из накопителей 2.

Для этого считывается информация из накопителя 1 и первого из накопителей 2, которая чрез коммутатор 8 записывается в накопители 7 и 7j,, из которых на формирователь 11 считывается пять разрядов, соответствующих накопителям 1, по выходам 37 и один разряд, соответствующий накопителю 2, по выходу 38. Результат из формирователя 11 через элемент ЗАПРЕТ 15, элемент ИЛИ 14 и коммутатор 8 поступает на запись в накопитель 7д по входу 34 («О - если перекодировки не было; «1 - если перекодировка была) и в накопитель 7 по входу 33 (восстановленный разряд). В этом же такте работы накопителя 7| информация из него поступает в преобразователь 10, куда приходит и восстановленный разряд отказавщего накопителя 1 с элемента ИЛИ 14. В зависимости от значения восстановленного разряда преобразователь 10 выводит на формирователь 12 принятое пятиразрядное слово без изменения или это же проинвертированное слово на формирователь 13, которые формируют результат четности (нечетности), записываемый в следующем такте через элемент ИЛИ 18 и крммутатор 8 в накопитель 7а. Наличие формирователя 13 (нечетности) вызвано следующими причинами: при отказе любого из накопителей 1 соответствующие ему разряды в накопителе TI равны «О, при этом восстановленный разряд отказавщего накопителя 1 может быть как «О, так и «1. Если он «1,

5 то все пять разрядов слова инвертируются, а следовательно, «О, соответствующий отказавщему накопителю 1, становится «1. Таким образом, в то время как все слово проинвертировалось, разряд отказавщего накопителя принял свое действительное

значение, чтобы эта ощибка не сказалась при формировании разряда четности, используется формирователь 13 (нечетности). Если после перекодировки отказал любой второй накопитель 1, то его информация

может быть восстановлена следующим образом: по две МАЕ считываются в накопители 7i и 72. Далее поразрядно на формирователь 11 поступают пять разрядов, соответствующих накопителям 1 по выходам 37 и разряд четности по выходу 38. Результат

0 с формирователя 11 поступает на элемент ЗАПРЕТ 15 и через элемент НЕ 16 на элемент И 17, которые управляются одноименным разрядом второго из накопителей 2. Если он «О (перекодировка этого слова не проводилась), то за восстановленный разряд отказавщего накопителя 1 принимается прямой результат с выхода формирователя 11. Если он «1, то элемент ЗАПРЕТ 15 прямой результат с формирователя 11 не пропускает, а инверсный результат с элемента НЕ 16 проходит через элемент И 17 и далее на запись в накопитель 7, и представляет собой восстановленный разряд.

До момента отказа второго накопителя 1 второй накопитель 2 может быть использован как дубль первого накопителя 2, и в этом случае на него при записи информации и формировании значений первого накопителя 2 аналогичным путем необходимо записать копию. Это позволит не

0 производить реконфигурацию информации в устройстве в тех случаях, когда первым откажет первый накопитель 2 (очевидно, что вероятность такого отказа имеется, хотя она и уменьщается с ростом числа накопителей 1).

5 Таким образом, в предлагаемой системе обеспечивается практически непрерывное функционирование, поскольку (в предположении, что одновременно не происходит отказа двух накопителей 1 и есть время для реконфигурации) после отказа одного накопителя 1 устройство через некоторое время, необходимое для перезаписи информации без ее потери, вновь может нормально функционировать. При этом устройство может вновь защититься от отказа одного из накопителей 1 и 2. Следовательно, до отказа второго из накопителей 1 в устройство можно либо добавить дополнительный накопитель 1 из исправных, но находящегося в холодном резерве, либо успеть

отремонтировать отказавший накопитель 1. Очень перспективно использование таких устройств в тех случаях, когда необходимо периодически производить регламентные работы, так как отключение одного накопителя для проведения регламентных работ не сказывается на работе всего устройства.

Технико-экономическое преимущество предлагаемого устройства по сравнению с известным заключается в более высокой надежности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1983 |

|

SU1149319A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU972601A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Запоминающее устройство с восстановлением информации | 1980 |

|

SU907581A1 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее основные и первый резервный накопители данных, первый формирователь сигналов четности и блок управления, отличающееся тем, что, с целью повышения надежности устройства, в него введены блок восстановления информации, накопители контрольной информации, преобразователь кодов, блок местного управления, второй формирователь сигналов четности, коммутаторы, формирователь сигналов нечетности, второй резервный накопитель данных, элементы ИЛИ, элемент И, элемент НЕ и элемент ЗАПРЕТ причем один из входов и выходов первого коммутатора являются входами и выхддами устройства, а другие входы и выходы соединены соответственно с одними из выходов и входов блока управления и с одними из выходов и входов блока местного управления, другие входы и выходы, которого подключены к выходам и входам основных и резервных накопителей данных, другие входы и выходы блока управления соединены с одними из выходов и входов блока восстановления информации, другие выход и вход которого подключены соответственно к первому входу второго коммутатора и к выходу третьего коммутатора. управляющие выходы блока восстановления информации соединены соответственно с входами первой группы и с управляющим входом третьего коммутатора, с адресными и с управляющими входами накопителей контрольной информации, с управляющими входами преобразователя кодов и с управляющими входами второго коммутатора, выходы которого подключены к информационным входам накопителей контрольной информации, одни из выходов которых соединены с входами второй группы третьего коммутатора, одними из входов первого формирователя сигналов четности и одними из входов преобразователя кодов, другие выходы накопителей контрольной информации подключены соответственно к i первому входу третьего коммутатора и другому входу первого формирователя сигна(Л лов четности, к второму входу третьего коммутатора, к третьему входу третьего коммутатора, первому входу элемента И и к первому входу элемента ЗАПРЕТ, второй вход которого соединен с выходом первого формирователя сигналов четности и входом элемента НЕ, выход которого подключен к второму входу элемента И, выход торого соединен с первым входом первого :о со элемента ИЛИ, второй вход которого подключен к выходу элемента ЗАПРЕТ, а выход - к второму входу второго коммутатора и другому входу преобразователя кодов, одни из выходов которого соединены с входами второго формирователя сигналов четности, выход, которого подключен к первому входу второго элемента ИЛИ, выход которого соединен, с третьим входом второго коммутатора, а второй вход - с выходом формирователя сигналов нечетности, входы которого и группа входов второго коммутатора подключены к другим выходам преобразователя кодов.

Л

/Г4

59

58

е

57

65

К

J/

6А

GO

6Г

I

/Ti

-1 -V

Ш

/г

f

54

3fT

Фиг. 2

21J2

t k

22 24

71

20

4

76

0m 56

68

67

I

i

44 4546

23

VАЛ /t

95

II

Фuz.J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Журавлев Ю | |||

| П., Котелюк А | |||

| П | |||

| и др | |||

| Надежность и контроль ЭВМ | |||

| М., «Советское радио, 1978, с | |||

| Телефонно-осведомительный аппарат | 1921 |

|

SU306A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3876978, кл | |||

| Поливное приспособление для паровозов | 1922 |

|

SU390A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

Авторы

Даты

1985-04-07—Публикация

1983-12-29—Подача