Изобретение относится к импульсной технике и может быть использовано в автоматике, вычислительной технике, технике связи и других областях, связанных с обработкой и преобразованием цифровой информации.

Известен делитель частоты, который содержит последовательный счетчик . со счетным триггером, триггером управления и схемой И-ИЕ в каждом разряде. Отдельные разряды соединены последовательно.один с другим таким образом, что счетные триггер образуют счетчик входных импульсов, а логические схеьды и управляющие триггеры - устройство управления. Схема обеспечивает возможность изменения коэффициента счета путем воздействия на входы управления кода управления коэффициентом счета l.

Недостатком известного устройства является его узкая специализация.

Известен также делитель частрты, содерЖЕШШй счетчик и элемент И, первый вход и ыход которого соединены соответственно с управляющим входом

делителя частоты и управляющим входом счетчика, .счетный вход которого

соединен с информационным входом делителя частоты р.

Недостатком этого делите.пя частоты являются ограниченные функциональные возможности.

Цель изобретения - расширение функциональных возможносте ч.

Поставленная цель достигается тем, что в делитель частоты, содержаoщий счетчик и элемент И, первый вход и выход которого соединены соответственно с управляющим входом делителя частоты и управляющим входом счетчика, счетный вход которого соединен 5 с информационным входом делителя частоты, введен блок памяти с произвольной выооркой, информационные входы которого соединены с выходами счетчика, входы записи данных блока памяти с произвольной выборкой соединены с установочными входами делителя частоты, а первый выход блока памяти с произвольной выборкой соединен с вторым входом элемента И.

5

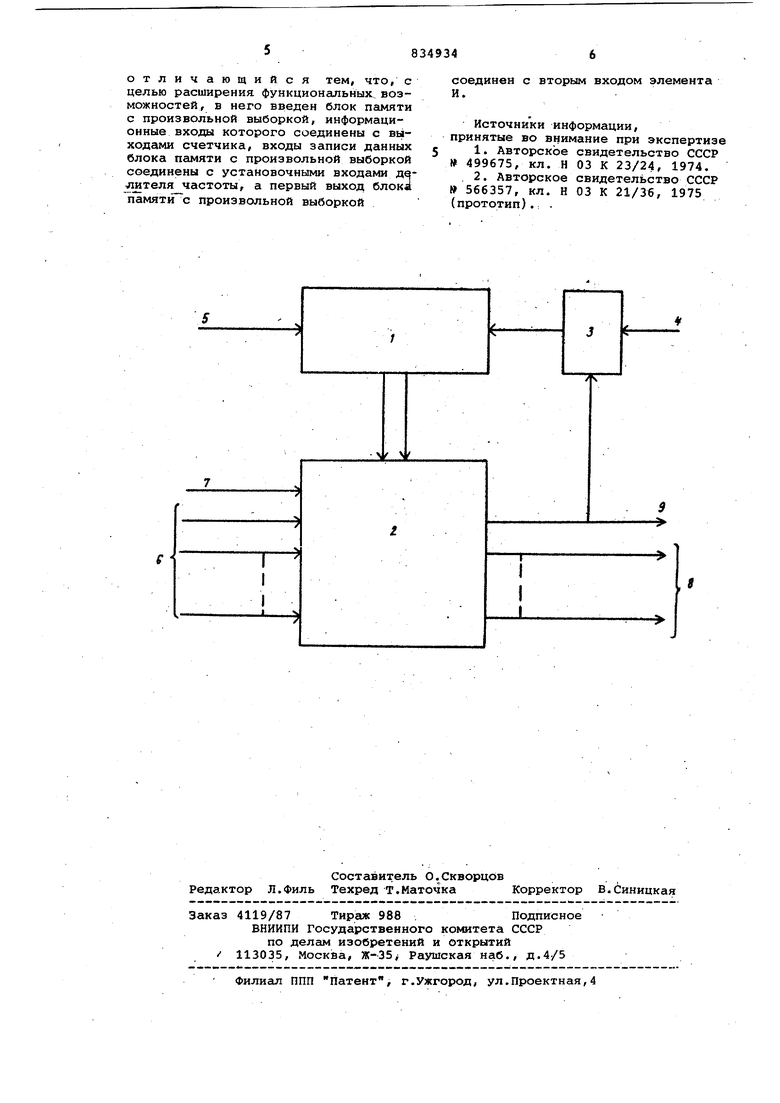

На чертеже показана структурная схема делителя частоты.

Делитель частоты содержит счетчик 1, блок 2 памяти с произвольной выборкой и элемент И 3, первый вход

0 и выход которого соединены соответственно с управляющим входом 4 делителя частоты и управляющим входом счетчика 1, счетный вход которого соединен с информационным входом 5 делителя частоты,информационные входы 6 блока 2 памяти с произвольной выборкой соединены с выходами счетчика, входы записи данных блока 2 памяти с произвольной выборкой соеинены с установочными входами 6. елителя частоты, а первый выход блока 2 памяти с произвольной выборкой соединен с вторым входом элемента И.

Делитель частоты реализует сле-f ующие основные функции: счетчика импульсов с любым целочисленным коэффициентом счета, линии задержки с юбым целочисленным значением величины задержки информации-и датчика последовательности с заданным распреелением импульсов в периоде.

Перед началом работы производится программирование устройства для еализации заданной функции.

Программирование устройства для реализации счетчика с заданным коэффициентом счета осуществляется следуквдим образом.

На вход счетчика 1 подается тактовая частота, на вход 7 управления записью-считыванием подается уровень напряжения, соответствующий режиму записи, и в момент накопления счетиком 1 числа импульсов, равного заанному коэффициенту счета, на инормационный вход б первого разряда блока 2 памяти подается логическая единица. На этом программирование заканчивается.

В работе блок 2 памяти по входу 7 управления записью-считыванием ус анавливается в режим считывания и каждый раз при накоплении счетчиком 1 числа, равного коэффициенту счета, на выходе блока 2 памяти появляется сигнал, приводящий счетчик 1 в начальное состояние при наличии разрешающего уровня напряжения на входе 4 устройства. Частота появления сигналов на выходе блока 2 памяти составляет F f/k, гдef- частота повторения импульсов на входе 5; k - коэффициент схета.

Программирование схемы для реализации линии задержки производится аналогично, при этом коэффициент счета выбирается равныЕМ заданной величине задержки информации. По окончании программирования на вход 6 второго разряда блока 2 памяти ; подается информационная последовательность, первый знак которой будет иметь место на выходе блока 2 памяти через время, определяемое выражением

t T-k, ,

где Т - период частоты следования импульсов на входе 5 делителя, k - коэс фициент счета.

На вход 7 управления записьюсчитыванием в работе подается последовательность, тождественная последовательности на входе 5 делителя. Згщержке могут подвергаться (n-l) последовательностей, где п т число разрядов блока 2 памяти.

Программирование схемы для реализации датчика последовательности с заданным распределением импульсов в периоде производится аналогично программированию счетчика, при этом коэффициент счета выбирается равным периоду повторения последовательности. Кроме того, в процессе nporpciMмирования во второй разряд блока 2 памяти по входу б записывается один период последовательности заданного вида.

В работе производится считывание последовательности, записанной во второй разряд блока 2 памяти, и на выходе 8 устройства рмеет место непрерывная последовательность заданного периода с заданным распределением импульсов. Устройство позволяет реализовать датчик (п-1)последовательностей, где п - число разрядов блока 2 памяти, а также датчик кода разрядности (п-1) и т.д

Помимо указанных функций, устройство может применяться для контроля узлов обработки цифровой информации. Например, с его помощью можно контролировать наличие недопустимог го числа подряд следующих единиц в последовательности. Для этого при программировании коэффициент счета выбирается равным недопустимому .числу подряд следующих единиц. В работе на вход 5 делителя подается тактовая частота, а на вход 4 - контролируемая последовательность. При появлении каждого нуля в контролируемой последовательности происходит сброс делителя в начальное состояние.

Импульс на выходе 9 имеет место лишь в том случае, когда в контролируемой, последовательности число подряд следующих единиц достигнет величины, недопустимой для данного кода. Устройство может применяться также для контроля .целостности электричесг ких цепей связи (определяются неисправности типа обрыв и другие, приводящие к эффекту длительного отсутствия сигналов сброса делителя), цепей тактовых частот и т.п.

Формула изобретения

Делитель частоты, содержащий счетчик и элемент И, первый вход и выход которого соединены соответственно с управляняцим входом делителя частоты и управляющим входом счетчика, счетный вход которого соединен с информационным входом делителя частоты.

отличающийся тем, что, с целью расширения функциональных возможностей, в него введен блок памяти с произвольной выборкой, информационные входы которого соединены с выходами счетчика, входы записи данных блока памяти с произвольной выборкой соединены с установочными входами делителя частоты, а первый выход блока памяти с произвольной выборкой

соединен с вторым входом элемента И.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР I 499675, кл. Н 03 К 23/24, 1974.

2.Авторское свидетельство СССР 566357, кл. Н 03 К 21/36, 1975 (прототип).; .

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный преобразователь | 1986 |

|

SU1401479A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| Способ селективной записи импульсных процессов и устройство для его осуществления | 1988 |

|

SU1636800A1 |

| Устройство синтеза испытательного сигнала измерителей фазочастотных характеристик | 1990 |

|

SU1795415A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для программного регулирования | 1986 |

|

SU1437833A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1990 |

|

SU1785034A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

Авторы

Даты

1981-05-30—Публикация

1979-11-13—Подача