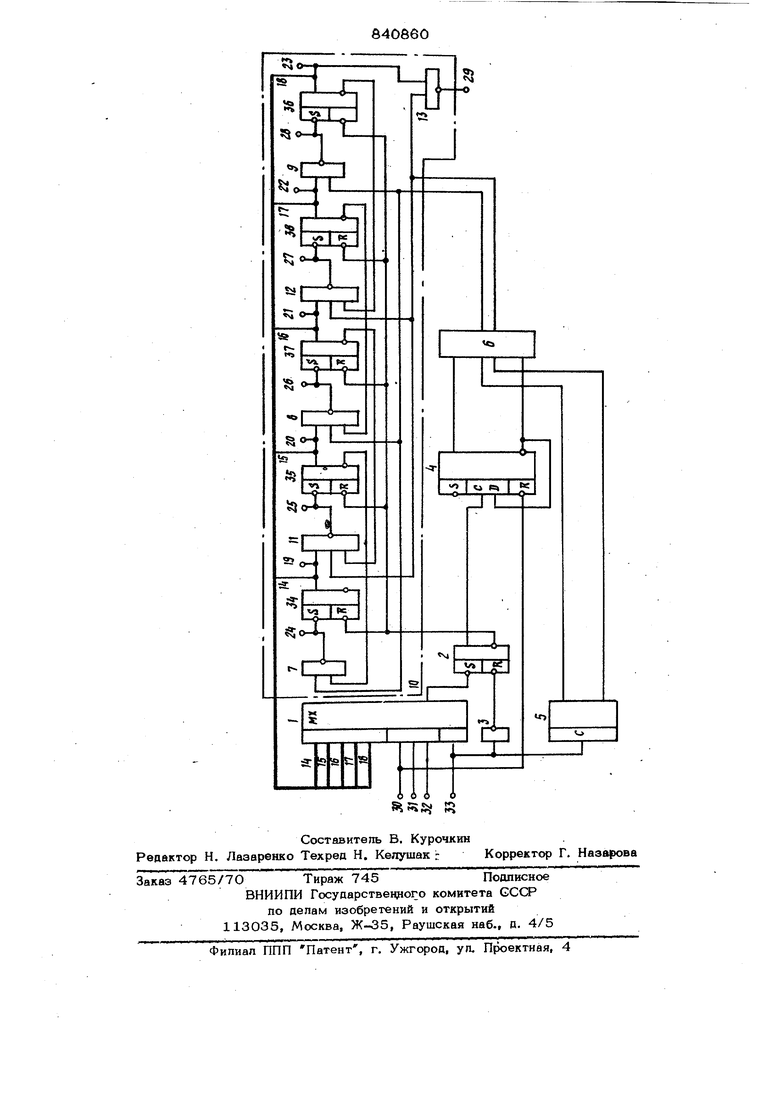

Изобретение относится к автоматике и вычислительной технике. Известен датчик тактов, содержащий N-разрядный регистр, каждый разряд которого состоит из двух триггеров, причем единичные входы первых триггеров каждого разряда соединены с нулевыми выходами вторых триггеров того же разряда, а единичные выходы со входами тактовой частоты устройства 11. Недостатком такого датчика является периодический пропуск входных тактов. Причем число пропущенных тактов тем больше, чем меньшее число каналов Q работе. Наиболее близким к предлагаемому по технической сущности является распределитель импульсов в котором датчик тактов содержит дополнительный триггер и элемент НЕ, что позволяет управлять чис лом каналов распределения импульсов при отсутствии неиспользуемых тактов. Однако при управлении таким распреде лителем имлульсов возникает существенный недостаток, заключающийся в том, что первый тактовый импульс, в з виси.мости от коэффициента пересчета, появляется на разных выходах устройства, что не позволяет применить известный распределитель импульсов в схемах с переменной структурой управления от микропроцессоров или ЭВМ, поскольку нарушается временная последовательность выполнения необходимых операций. Цель изобретения - расширение области применения устройства, за счет привязки первого тактового импульса к первому выходу устройства при любом коэффициенте пересчета. Указанная цель достигается тем, что каждый разряд регистра содержит элемент И-НЕ и триггер, выход которого соединен с первым входом элемента И-НЕ Предыдущего разряда, выход триггера каждого раоряда соедине со вторым входом элемента И-НЕ последующего разряда единичные выходы, (п - разрядного регистра соейинены с соответствующими входами му1ть384типпексора, выход которого соединен с единичным входом триггера установки в О т -разрядного регистра, единичный выход которого соединен со счетным входом триггера относительности, а нулевой выход соединен с нулевыми установочными входами m -разрядного регистру,при этом единичный и нулевой выходы триггера относительности соединены с управлякядими входами коммутатора, информациOHHbte входы которого соединены с выхо- .дами формирователя двух серий импульсов, при этом один вывод коммутатора соединен с третьими входами элементов И-НЕ всех нечетных разрядов регистра, а другой выход - с третьими входами элементов И-НЕ всех четных разрядов ре гистра, тактовый вход мупьтинлексора соединен с входом формирователя двух серий импульсов и через элемент НЕ сое-г динен с нулевым входом триггера установки в О иг -разрядного регистра а нулевой вход триггера относительности соединен с младшими разрядами управля ющего входа мультиплексора. На чертеже приведена схема распределителя импульсов. Уп{ авляемый распределитель ймпуль .срв содержит мультиплексор 1, выход ко- .торого соединен с единичным входом триггера установки в О регвсгра - тактовый вход мупьтиплексора 1 элемент ЙЕ 3 соединен с liyлевым входом тригге ра установки в О регистра 2, единич ный выход триггера установки в О регистра 2 соединен со входом триггера 4 относительностИз а нупевой нход его соединен с управляющим входом младшего разряпа мультиплексора 1, пы (Ьопмиооватепя 5 двух серий импульсов ды ijjutJMHputsai Ji «Djyv tj соединены с тактовым входом мупьтиппекоора 1, а выходы соединены с управляю щими входами коммутатора 6, при этом один выход коммутатора 6 соединен со входами элементов И-НЕ 7-9, всех нечет ных разрядов регистра 10, а другой выход - со входами схем И-НЕ 11-13 всех .четных разрядов, кроме того, единичные выходы регистра Ю соединены соответсг венно со входами И-НЕ старших разрядов а нулевые выходы - соответственно со входами схем И-НЕ младших разрядов, единичные выходы 14-18 регистра 10 соединены с соответствующими входами мультиплексора 1. В исходном состоянии на выходе триг г-ера установки в О регистра 2 вырабатывается О, который устанавливает ре 04 гистр 10 в О. При этом на выходах 19-23 устанавпивается О , а на выходах 24-29 -it На выходные шины 3032 приходит управпякхцая команда в параллельном коде с весами соответствейно 1-2-4. На шины-30 и 32 приходит 1 на шнну 31 - О ., что соответствует коэффидиенту пересчета пять и соответственно пяти каналам распределения импульсов. С приходом тактовых импульсов (ТИ) на шину 33 триггер установки в О регистра 2 вырабатывает , которая разрешает работу регистра 10, выполненного на триггерах 34-38. Одновременно формироватепь 5 двух серий импульсов вырабатывает две серии импульсов, сдвинутых друг относительно друга на 180° ТИ1 и ТИ2, ТИ1 и ТИ2 поступают на входы коммута-гора 6 импульсов управления, на другие входы поступают потенциальные сигналы с выхода триггера 4 относительнести, который включен по схеме со счетмым входом и перебрасывается по сигна- дам единичного выхода триггера устано ки в О регистра 2. . 1 -1 Допустим, что в исходном состоянии на единичном выходе триггера относительности присутствует логическая 1, а на нулевом выходе - логический О. , Тог обьединяюшую элемен д поступает серия по ТИ1. В. другую шину, объединяющую элементы ИНЕ 11-13 псступает серия по ТИ2. При этом на выходе 18 элемента И-НН 7 появляется первый отрицательный импульс, а на выходе 19 триггера 34 появляется положительный импульс, который подготавга вает элемент И-НЕ 8 к работе. Одно- временно мультиплексор 1 анализирует единичный ВЫХОД триггера 34 ПО законууправпяющих сигналов на шинах ЗО-32. С приходом импупьса по ТИ2 на выходе 25 схемы И-НЕ 11 появляется .второй отрицательный импульс, сдвинутый на 18О дю отношению к отриаатепьному импульсу на выходе 24, а на выходе .20 триггера 35 появляется положительный импупьс, который подготавливает элемент И-НЕ 8 к работе. Одновременно мультиплексор 1 единичный выход триггера 35 по закону управляющих сигналов на шинах ЗО-32. Кроме того, нулевой выход триггера 35 запрещает работу элемента И-НЕ 7. Аналогично работают остальные разряды регистра, причем по другому импульсу ТИ1 появляется третий отрицатель- импупьс на выходе 26, и по другому импульсу ТИ2 появляется четвертый от5ft4риивтельный импупьс на выходе 27. С приходом третьего импульса по ТЙ1 появ пяется пятый отрицательный импульс на выходе 28. . В качестве мультиплексора выбрана стандартная микросхема 155КП1. Единичный выход триггера 36 дешифри руется мультиплексором 1 и по заднему онту ТИ перебрасывает схему установки в О регистра2. Нулевой выход схемы установки в О регистра 2 устанавливает регистр 1О в исходное состояние, а единичный выход триггера установки в О регистра2 перебрасывают триггер относительности 4. При этом на единич иом выходе триггера 4 относительности появляется логический О, а на нулевом выходе - логическая . Коммутатор 6 импульсов управления перебрасывает фазы импульсов в общих шинах регистра 10. Цикл окончен, схема готова к повторному циклу. Для изменения числа каналов распределения необходимо изменить управляющую команду на шинах . При этом следует учитывать правило, что число раз 1 рядов регистра w должно бытьт 2, где и. - число разрядов управляющей команды. Коммутатор 6 импульсов управления работает в о&дем случае по закону ти1 Л Q V ТИ2 ла ТИ1 Л Q V ТИ2Ла , где Q - единичный выход триггера 4 относительности, а Q - нулевой. Применение управляемого распределителя импульсов целесоо.бразно в блоках с переменной структурой управления от микропроцессоров или ЭВМ. Эффективность изобретения получается за счет привязки первого тактового импульса к первому выходу устройства при любом коэффициенте пересчета. Вцелом повышенная гибкость предлагаемого ства позволяет сократить затраты на по- строение блоков с переменной структурой по сравнению с известным, не менее 1,1 (г) раз.. O Формула изобретения Управляемый распредепитепь импупьсов, содержащий т - разрядный регистр, отличающийся тем, что, с целью расщирения области применения устройства за счет привязки первого тактового импульса к первому выходу устройства при любом коэффициенте пересчета, каждый разряд регистра содержит элемент И-НЕ и триггер, выход которого соединен с первым входом .элемента И-НЕ предыдущего разряда, выход триггера каждого разряда соединен со вторым входом элемента И-НЕ последующего разряда, единичные выходы -разрядного регистра соединены с соответствующими входами мультиплексора, вы ход которого соединен с единичным- входом триггера установки в О и -разрядного регистра, единичный выход которого соединен со счетным входом триггера относительности, а нулевой выход соединен с нулевыми установочными входами wt -разрядного регистра, при этом единичный и нулевой выходы триггера относите льнсюти соединены с управляющими входами коммутатора, информационные входы которого соединены с выходами формирователя двух серий импульсов, при этом один выход коммутатора соединен с третьими входами элементов И-НЕ всех нечетных разрядов регистра, а другой выход - с третьими входами, элементов ИНЕ всех четных разрядов регистра, тактовый вход мультиплексора соединен с входом формирователя двух серий импульсов и через элемент НЕ соединен с нуле- . вым входом триггера установки в О п - разрядного регистра, а нулевой вход триггера относительности соединен с младшим разрядом управляющего входамультиплексора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 456269, кл. G 06 F 1/О4, 11.О1.73. 2. Авторское свидетельство СССР № 61547О, кл. G 06 F 1/04, 23.08.76.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программно-логических матриц | 1987 |

|

SU1469504A1 |

| Процессор матричной вычислительной системы | 1987 |

|

SU1603395A1 |

| Устройство для ввода информации от датчиков | 1990 |

|

SU1691828A1 |

| Устройство для определения локальных экстремумов | 1983 |

|

SU1164694A1 |

| Устройство для индикации | 1989 |

|

SU1649602A1 |

| Регистр сдвига | 1976 |

|

SU682950A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Буферное запоминающее устройство | 1976 |

|

SU750565A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

Авторы

Даты

1981-06-23—Публикация

1979-09-03—Подача