1

Изобретение относится к вычислительной технике, служит для преобразрвания прямого кода в дополнитЪльный и может быть использовано в арифметических устройствах и других устройствах обработки цифровой информации.

Известны преобразователи прямого кода в дополнительный, построенные на триггерных регистрах t11.

Однако известные преобразователи обладают недостаточной надежностью работы.

Наиболее близким к пpeдлг гaeмoмy является преобразователь прямого кода в дополнительный, построенный на логических элементах и сумматоре 2.

Однако схема такого преобразователя достаточнр сложна.

Цель изобретения - упрощение устройства.

Цель достигается тем, что в преобразователе прямого кода в дополнительный, содержащем при преобразовании (п+1)- разрядного коДа п элементов И-НЕ и п-разрядный сумматор, ишна каждого i-ro разряда входного кода (.) соединена со входом (1-1)-го элемента И-НЕ и со входом

i-ro разряда сумматора, с другим, входом которого соединен выход i-ro элемента И-НЕ, вход п-го элемента И-НЕ подключен к шине управляющей константы, выход первого элемента И-НЕ и шина первого разряда входного кода подключены ко входам первого разряда сумматора, шина знака входного кода подключена ко входам всех элементов И-НЕ.

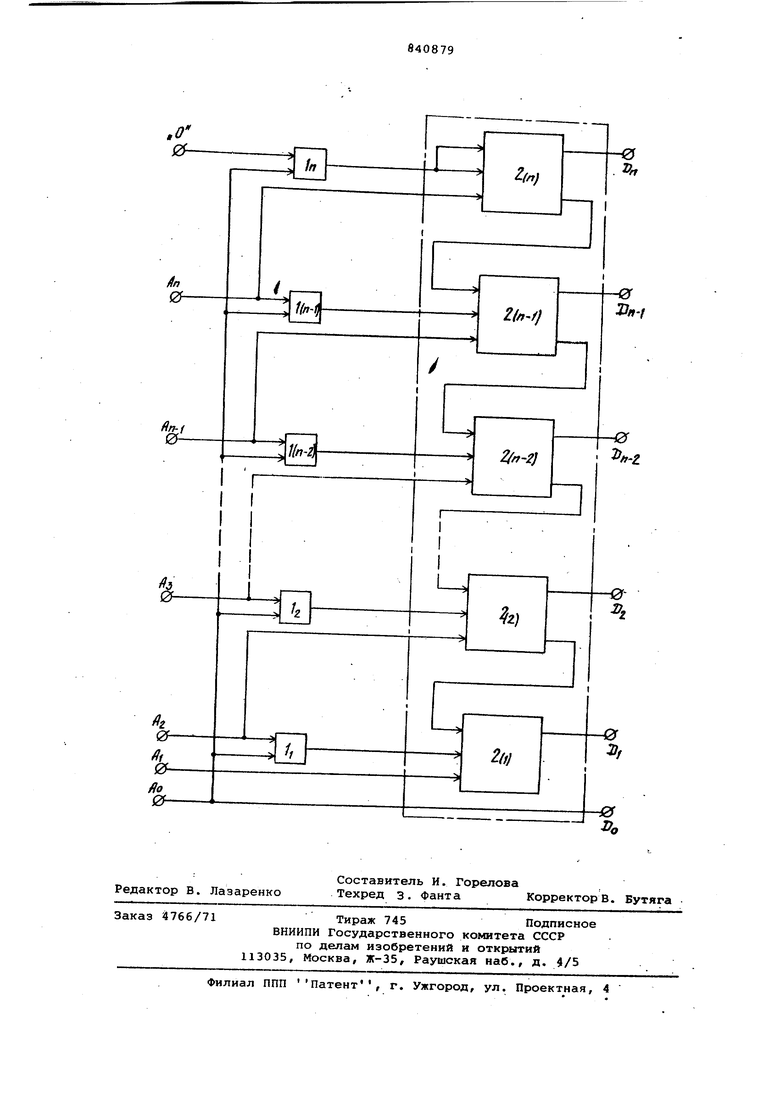

. На чертеже представлена функциональная блок-схема преобразователя прямого кода в дополнительный.

Устройство содержит п элементов 1-1 г 1-п И-НЕ и п-разрядный сумматор 2 (2-1 7 2-п). Первая шина знак Ад входного кода соединена со входами всех элементов 1-1 т 1-п ИНЕ. Вторая шина первого разряда А входного кода подключена ко входу первого разряда сумматора 2-1, i-ая .шина каждого -последующего разряда входного кода Ai(2«i) подключена ко входу ( элемента И-НЕ и ко входу 1-го разряда сумматора 2. Один вход п-го элемента И-НЕ подключен к (п-И)-ой шине управляющей кона выход п-го элемента

станты

И-НБ подключен дополнительно ко входу переноса п-го разряда сумматора.

Преобразователь работает следующим обраэом.

Входной разрядный код , в прямом коде поступает на пернме входы соответствующих разрядов сумматора 2 и со сдвигом влево на один разряДнНа первые входы элементов И-НЕ. Пви поступлении положительного числа esro знаковый разряд ) блокирует элементы И-НЕ, что при подключении выхода п-го элемента и-ПЕ ко входу переноса п-го разряда сумматора эквивалентно подаче на вторые входы всех разрядов сумматра 2 сигналов 0, при этом иа выходах сумматора выдается входной разрядный код без преобразования т,е .

При поступлении отрицательного числа знаковый разряд его кода () разрешает работу всем элементам И-НЕ, и на входы сумматора поступают входное число в прямом коде и удвоенное (за счет сдвига влево на один разряд) Число в инверсном коде с выходов элементов И-НЕ, причем с выхода младшего (п-го) элемента И-НЕ сигнал i подается на второй вход и на вход переноса младшего (п-го) разряда сумматора 2, Сумматор 2 в этом случае выдает выходное число в дополнительном коде, так как

D А-2А -Д.

При необходимости преобразования информации, представленной в обратном коде, на вход п-го элемента И-НЕ постоянно подаетсСсигнал Ч (вмеО) .

сто сигнала

Предлагаемая схема проооразователя проста и позволяет ум«;яьшить объем оборудования и потребляемую им мощность.

Формула изобретлз«{гя

Преобразователь прямого кода в дополнительный, содержащий при преоразовании (п+1)-разрядного кода п элемвнтсш И-НЕ и п-раэрядный сумматор,, о т л к ч а ю .щ и и с ятем, что, с целью упрощения устройства, шина каждого i-ro разряда входного кода () соединена со входом (1-1)-го элемента И-НЕ и со входом i-ro разряда сумматора, с другим входом которого соединен вход элемента И-НЕ, вход п-го элемента И-НЕ подключен к шине управляющей константы, выход первого элемента И-НЕ и шина первого разряда входного кода подключены входам первого разряда сумматора, шина знака входного кода подключена ко входам всех элементов И-НЕ.

Источники информации, принятые во внимание при экспертиз

1.Авторское свидетельство СССР 259472, кл. G Об F 5/02.

2.Папернов А.А. логические осно цифровой вычислительной техники. М.

Советское радио, 1972, с. 163, рис. 18 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для суммирования двоичных чисел | 1983 |

|

SU1103223A2 |

| Устройство для сложения чисел | 1982 |

|

SU1035599A1 |

| Вычислительное устройство | 1985 |

|

SU1278840A1 |

| Устройство для суммирования п-разрядных двоичных чисел | 1976 |

|

SU634275A1 |

| Устройство для умножения двоичных чисел в дополнительном коде | 1983 |

|

SU1191907A1 |

| Вычислительный преобразователь информации | 1985 |

|

SU1330642A1 |

| Преобразователь двоичного кода вдОпОлНиТЕльНый | 1979 |

|

SU851395A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

Авторы

Даты

1981-06-23—Публикация

1978-01-25—Подача