Изобретение относится к вычислительной технике и foжeт быть использовано в составе универсальных или специализированных машин и устройств для быстрого выполнения операций деления и извлечения квадратного корня над операндами с фиксированной запятой.

Цель изобретения - расширение

Одновибратор 10 предназначе формирования импульсов заданно тельности и может быть реализо в частности, по известной схем вход запуска соответствует вхо ноБибратора 10, а вход сброса нен с входом логической 1.

Одновибраторы 27 предназнач соответственно для запуска пр

функциональных возможностей устройст- ключении на их входах О в 1

ва за счет реализации операции извлечения квадратно.Го .корня.

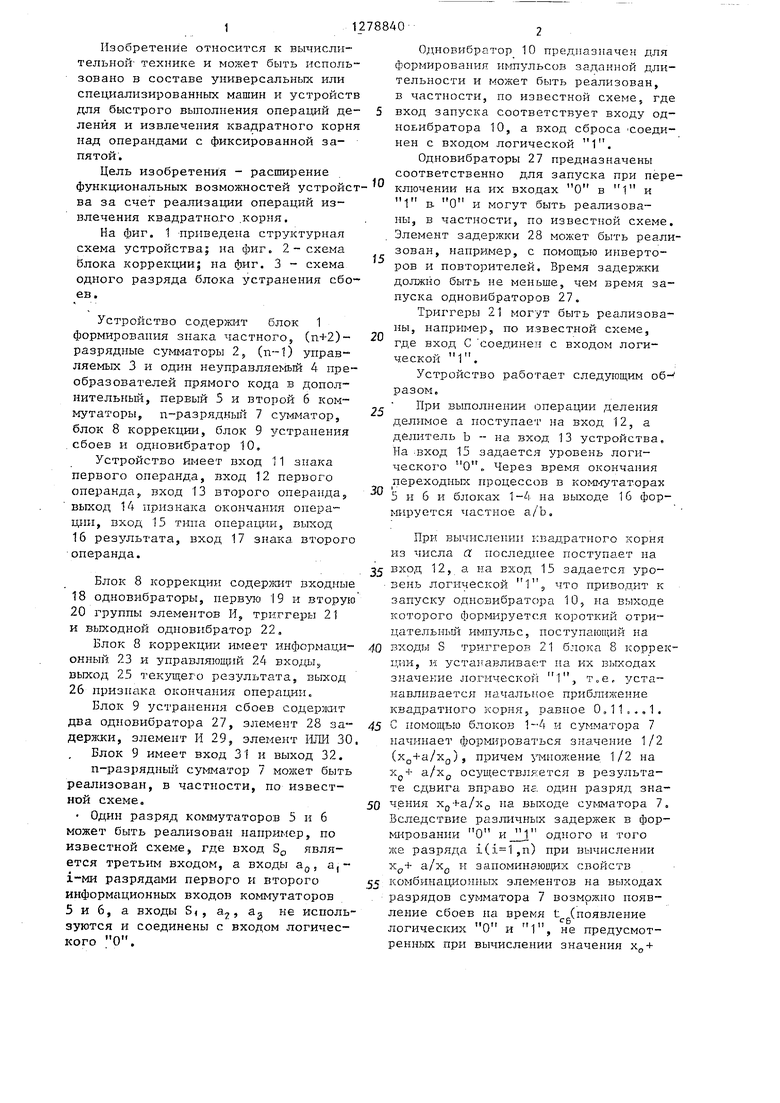

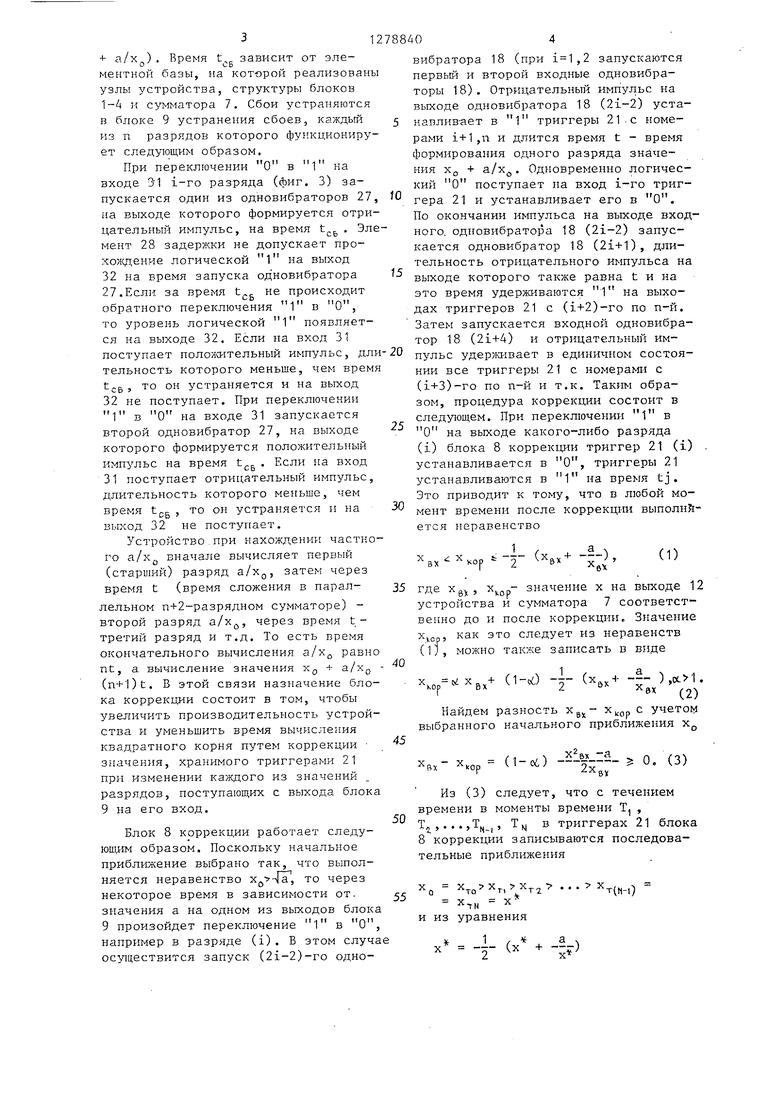

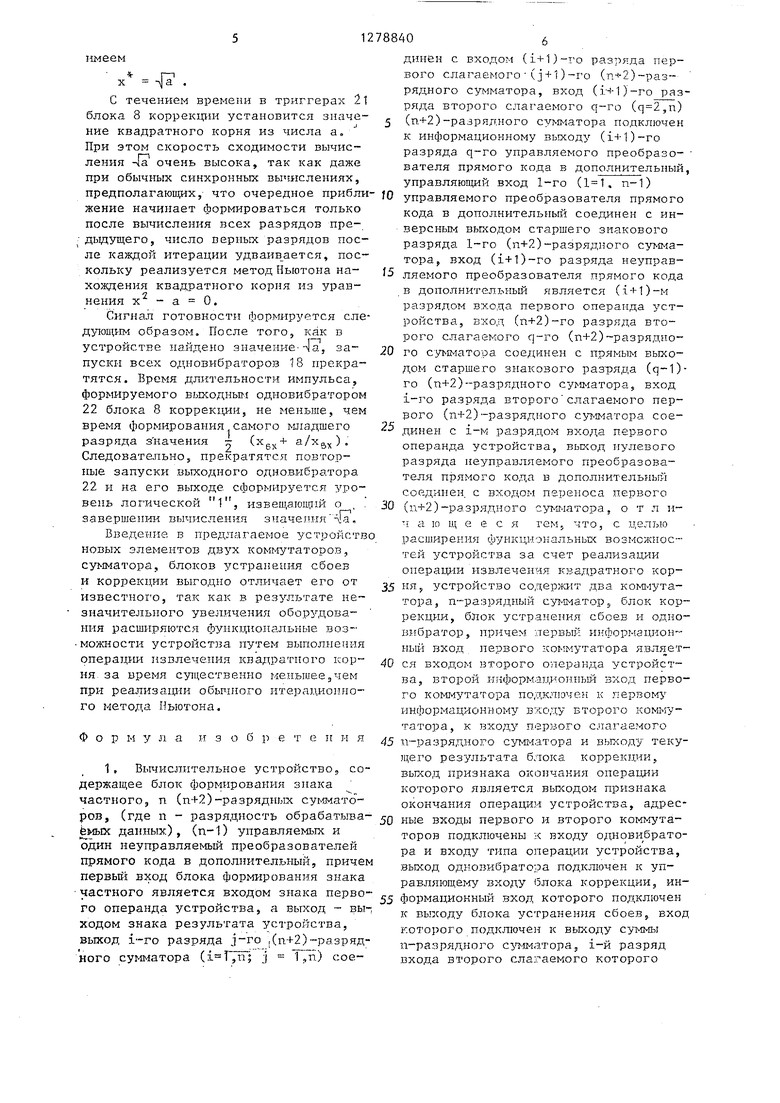

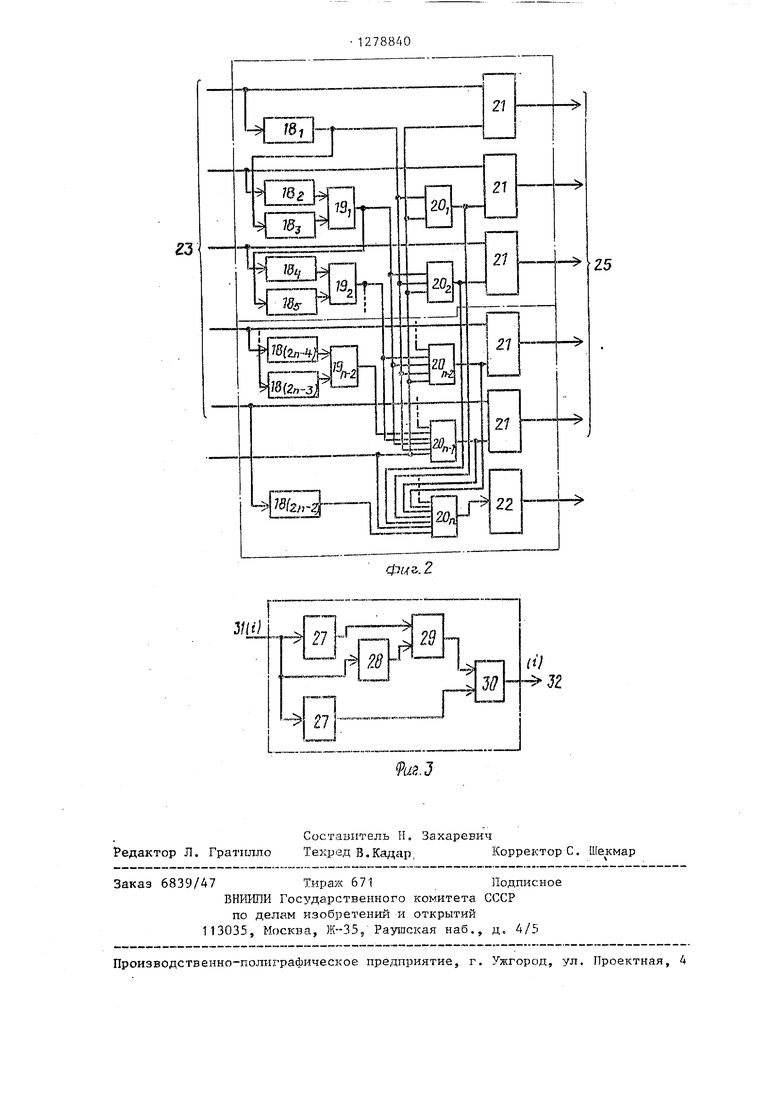

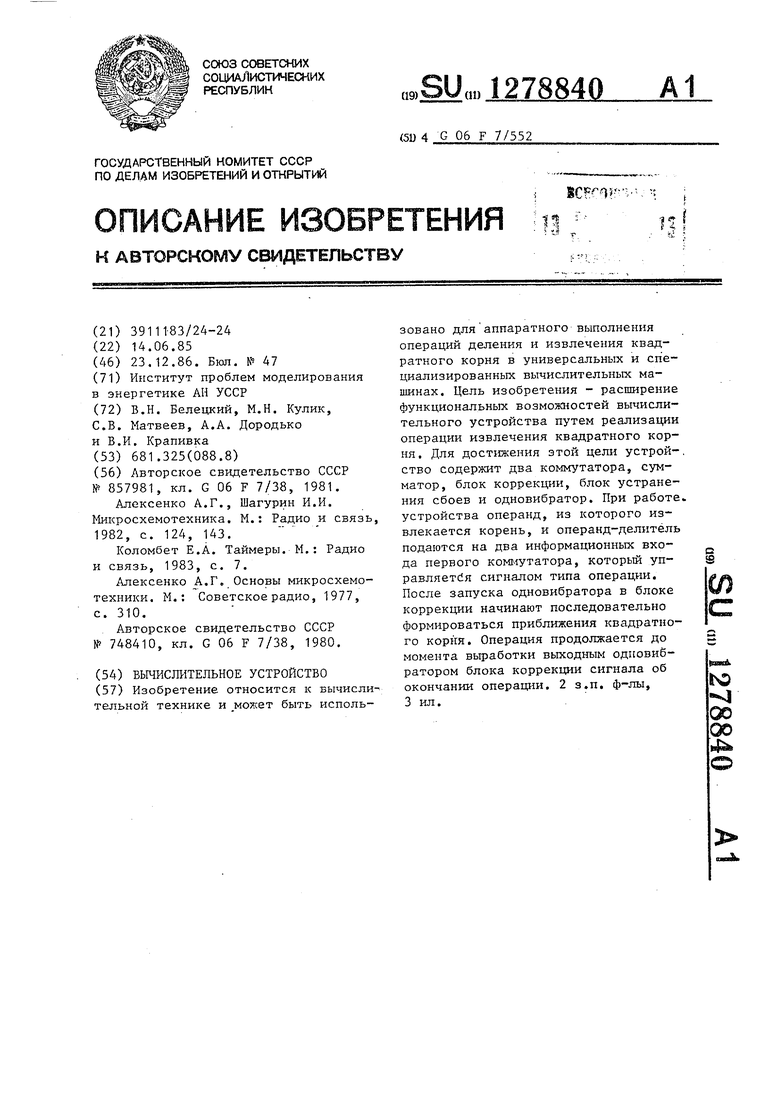

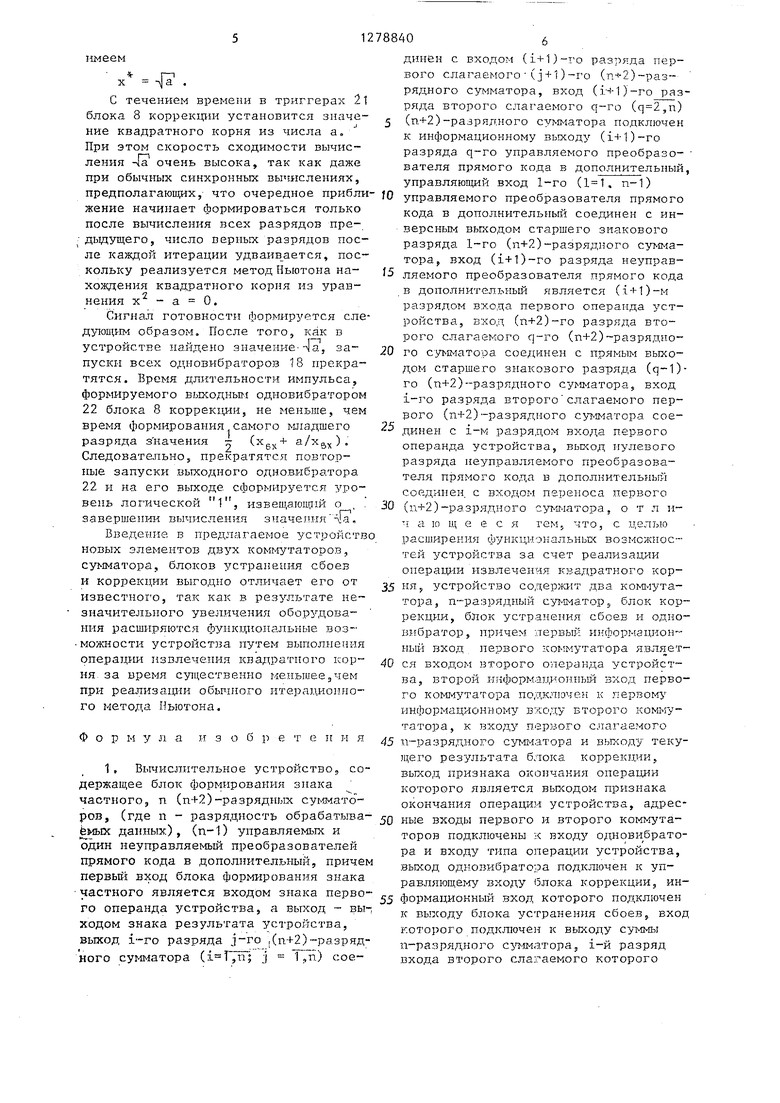

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - схема блока коррекции; на фиг. 3 - схема одного разряда блока устранения сбоев.

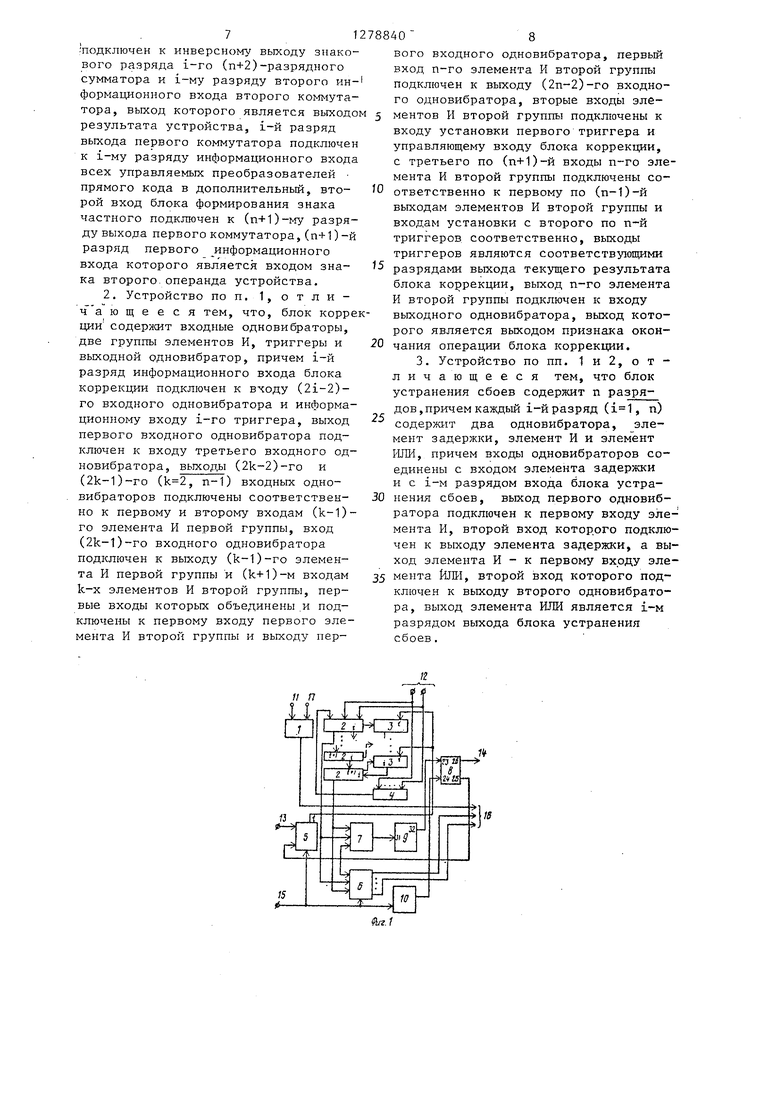

Устройство содержит блок 1 формирования знака частного, (п+2)- разрядные сумматоры 2, (n-t) управляемых 3 и один неуправляемый 4 преобразователей прямого кода в дополнительный, первый 5 и второй 6 коммутаторы, п-разрядный 7 сумматор, блок 8 коррекции, блок 9 устранения .сбоев и Одновибратор 10,

Устройство имеет вход 11 знака первого операнда, вход 12 первого операнда,, вход 13 второго операнда, выход 14 признака окончания операции, вход 15 типа операции, выход 16 результата, вход 17 знака второго операнда.

Блок 8 коррекции содерлсит входные 18 Одновибраторы, первую 19 и вторую 20 группы элементов И, триггеры 21 и выходной Одновибратор 22,

Блок 8 коррекции имеет ннформаци- 40 входы S триггеров 21 блока 8 корреконный 23 и з правляющий 24 входы, выход 25 текущего результата, выход 26 признака окончания операции.

Блок 9 устранения сбоев содерлит

два одновибратора 27, элемент 28 за- 45 С помощью блоков 1-4 и сумматора 7

деряски, элемент И 29, элемент I-fflH 30.

Блок 9 имеет вход 31 и выход 32.

п-разрядньй сумматор 7 может быть реализован, в частности, по известной схеме,

Один разряд коммутаторов 5 и б может быть реализован например, по известной схеме, где вход S является третьим входом, а входы а, а,- i-ми разрядами первого и второго информационных входов коммутаторов 5 и 6, а входы S, а,,, ад не используются и соединены с входом логичес- кого О,

Одновибратор 10 предназначен для формирования импульсов заданной длительности и может быть реализован, в частности, по известной схеме, где вход запуска соответствует входу од- ноБибратора 10, а вход сброса Соеди- нен с входом логической 1.

Одновибраторы 27 предназначены соответственно для запуска при переключении на их входах О в 1

и

5

0

5

0

1 в. О и могут быть реализованы, в частности, по известной схеме. Элемент задержки 28 может быть реализован, например, с помощью инверторов и повторителей. Время задержки должно быть не меньше, чем время запуска одновибраторов 27.

Триггеры 21 могут быть реализованы, например, по известной схеме, где вход С соединен с входом логической 1.

Устройство работает следующим об- разом.

При выпол 1ении операции делимое а поступает на вход 12, а делитель Ь - на вход 13 устройства. На вход 15 задается уровень логического Через время окончания переходньк процессов в ког-л-гутаторах 5 и б и блоках 1-4 на выходе 16 формируется частное а/Ь.

При вычислении квадратного корня из числа а послед.нее поступает на 35 вход 12, а на вход 15 задается уровень логической I, что приводит к запуску одновибратора 10, на выходе которого формируется короткий отри- цательньп импульс, поступающий на

1, и устар авливае .т на их выходах II t It

1

и,ии,

значение логической 1, т„е, устанавливается начальное приближение квадратного корня, равное 0,11.„1.

начинает формироваться значение 1/2 (Хд+а/Хд), причем умиолсение 1/2 на X + а/Хц осуществляется в результате сдвига вправо на один разряд значения Хд+а/Хд на выходе сумматора 7. Вследствие различных задержек в формировании О и одного и того же разряда i(,п) при вычислении ХР+ а/Хд и заполминэюищх свойств

комбинацио.ниых элементов на выходах разрядов сумматора 7 возможно появление сбоев на время t (появление логических О и 1,

не предусмот - а/Хд) . Время t зависит от элементной базы, на которой реализованы узлы устройства, структуры блоков 1-4 и сумматора 7. Сбои устраняются в блоке 9 устранения сбоев, каждый из п разрядов которого функционирует следующим образом.

При переключении О в 1 на входе Э1 i-ro разряда (фиг. 3) запускается один из одновибраторов 27, на выходе которого формируется отрицательный импульс, на время t . Элемент 28 задержки не допускает прохождение логической 1 на выход 32 на время запуска одновибратора 27.Если за время t., не происходит обратного переключения 1 в О, то уровень логической 1 появляется на выходе 32. Если на вход 31 поступает полоядательный импульс, дли тельность которого меньше, чем время tjg, то он устраняется и на выход 32 не поступает. При переключении 1 в О на входе 31 запускается второй одновибратор 27, на выходе которого формируется положительный импульс на время t . Если на вход 31 поступает отрицательный импульс, длительность которого меньше, чем время tgg, то он устраняется и на выход 32 не поступает.

Устройство.при нахождении частного а/Хд вначале вычисляет первый (старший) разряд а/х, затем через время t (время сложения в парал-

лельном n+2-разрядном сумматоре) - второй разряд а/х, через время t- третий разряд и т.д. То есть время окончательного вычисления а/х равно nt, а вычисление значения х + а/х., (n+1)t. В этой связи назначение блока коррекции состоит в том, чтобы увеличить производительность устройства и уменьшить время вычисления квадратного корня путем коррекции значения, хранимого триггерами 21 при изменении каждого из значений разрядов, поступающих с выхода блока

9 на его вход.

Блок 8 коррекции работает следующим образом. Поскольку начальное приближение выбрано так, что выполняется неравенство , то через некоторое время в зависимости от. значения а на одном из выходов блока 9 произойдет переключение 1 в О, например в разряде (i). В этом случа осу1цествится запуск (2i-2)-ro одновибратора 18 (при ,2 запускаются первый и второй входные одновибра- торы 18). Отрицательный импульс на выходе одновибратора 18 (21-2) уста- наплив-ает в 1 триггеры 21-с номерами i+1,n и длится время t - время формирования одного разряда значения XQ + а/-к. Одновременно логический О поступает на вход i-ro триггера 21 и устанавливает его в О. По окончании импульса на выходе входного, одновибратора 18 (21-2) запускается одновибратор 18 (21+1), длительность отрицательного импульса на выходе которого также равна t и на это время удерживаются 1 на выходах триггеров 21 с (1+2)-го по п-й. Затем запускается входной одновибратор 18 (21+4) и отрицательный импульс удерживает в единичном состоянии все триггеры 21 с номерами с (1+3)-го по п-й и т.к. Таким образом, процедура коррекции состоит в следующем. При переключении 1 в О на выходе какого-либо разряда (1) блока 8 коррекции триггер 21 (1) устанавливается в О, триггеры 21 устанавливаются в 1 на время tj. Это приводит к тому, что в любой момент времени после коррекции выполнй ется неравенство

-Г вх+ ™), (1)

где Xgy , значение х на выходе 1 устройства и сумматора 7 соответственно до и после коррекция. Значение , как это следует из неравенств (и, можно также записать в виде

(1-) -Г - Гв,)- Найдем разность с учетом выбранного начального приближения х

wp (1-oi)

2хГ

0. (3)

вх

Из (3) следует, что с течением времени в моменты времени Т,, Т„ ,. .. ,, TM в триггерах 21 блока 8 коррекции записываются последовательные приближения

Г2 ... X v лг

тн уравнения

1- (х + -5-) 2

т(н-0

имеем

X .

С течением времени в триггерах 21 блока 8 коррекц51И установится значение квадратного корня из числа а. При этом скорость сходимости вычисления Ча очень высока, так ка.к даже при обычных синхронных вычислениях,

динен с входом (i+1)-ro разряда первого слагаемого (J+ 1)-го ()раз- ря/дного сумматора, вход (г+1)-го раз ряда второго слагаемого q-ro (,n) (n+2)-разрядного сумматора подключен к информационному выходу (i+1)-ro разряда q-ro управляемого преобразо- вателя прямого кода в дополнительный управляющий вход 1-го (. п-1)

предполагающих, что очередное прибли- JO управляемого преобразователя прямого жение начинает формироваться только после вычисления всех разрядов предыдущего, число верньЕХ разрядов после каждой итерации удваив ается, поскода в дополнительный соединен с инверсным выходом старшего знакового разряда 1-го (п+2)-разрядного сумматора вход (i+l)-ro разряда неуправкольку реализуется метод Ньютона нахождения квадратного корня из уравнения X - а 0.

Сигна,п готовности формируется следующим образом. После того, как в устройстве найдено значение--4а , запуски всех одновнбраторов 18 прекратятся. Время длительности импульса, формируемого вг псодным одновибратором 22 блока В коррекции, не меньше, чем время формирования самого младшего разряда значения (ех Следовательно, прекратятся повторные запуски вь хо7-1,ного одновибратора 22 и на его выходе сформируется уровень логической 1, извещаюнгпй о . завершенш- вычисления значе1пгя т а.

Введение в предлагаемое устройство новых элементов двух коммутаторов, сумматора, блоков устранения сбоев и коррекции выгодно отличает его от известног о, так как в результате незначительного увеличения оборудования расширяются функщюнальные воз- можности устройства путем выполнения операции извлечения квадратного корня, за время существенно меньшее,чем при реализации обычного итерационного метода Ньютона,

20

25

кода в дополнительный соединен с инверсным выходом старшего знакового разряда 1-го (п+2)-разрядного сумматора вход (i+l)-ro разряда неуправ 5 ляемого преобразователя прямого кода в дополнительный является (i+l)-M разрядом входа, первого операнда устройства, вход (п+2)го разря/1;а второго слагаемого q-ro (п+2)-разрядного сумматора соединен с прямым выходом старшего знакового разряда (q-1)- го (п+2)-разрядного сумматора, вход i-ro разряда второго слагаемого пер- рого (п+2)-разрядного су матора соединен с i-M разрядом входа первого операнда устройства, выход нулевого разряда неуправляемого преобразователя прямого кода в дополнительньгй соединен, с входом переноса первого (п+2)-разрядного сут-и-гатора, о т л и- ч а 10 щ е е с я гем, что, с целью расширения функциональньЕ возможностей устройства за счет реализации онеращш извлечения квадратного кор35 нЯу устройство содержит два .- тора, п-разрядный сумматор, блок коррекции, блок устранения сбоев и одно- вибратор, причем первый инфорнацион- ньй вход первого ко1- мутатора является входом второго операнда устройства, второй информационный вход нерво30

40

Форм у л а и 3 о б р е

н и я

СОГО ком: 1утатора подключе;- к первому информационному входу второго KOMivsy- татора, к входу первого слагаемого 45 п-разрядного сумматора и вькоду текущего результата блока коррекции, выход признака окончания операнди которого является выходом признака окончания операц1 и устройства, адрес- 50 ные входы первого и второго коммутаторов подключены к входу однови брато- ра и входу типа операции устройства, выход одновибратора подключен к управляющему входу блока коррекции, ин- - частного является входом знака перво- формационный вход которого подключен

к вызсоду блока устранения сбоев, вход которого подключен к выходу су1чмы п-разрядного с:у т-шатора, i-й разряд входа второго слагаемого которого

1 , Вычислительное устройство, держащее блок формирования знака частного, п (п+2)-разрядных суьмато - ров, (где п - разрядность обрабатываемых данных), (п-1) управляемых и один неуправляемый преобразователей прямого кода в дополнительный, причем первый вход блока формирования знака

го операнда устройства, а выход - вы-, ходом знака результата устройства, выход i-ro разряда j-ro ,(п+2)-разрядного сумматора ( j 1 ..п) соединен с входом (i+1)-ro разряда первого слагаемого (J+ 1)-го ()раз- ря/дного сумматора, вход (г+1)-го разряда второго слагаемого q-ro (,n) (n+2)-разрядного сумматора подключен к информационному выходу (i+1)-ro разряда q-ro управляемого преобразо- вателя прямого кода в дополнительный, управляющий вход 1-го (. п-1)

управляемого преобразователя прямого

управляемого преобразователя прямого

кода в дополнительный соединен с инверсным выходом старшего знакового разряда 1-го (п+2)-разрядного сумматора вход (i+l)-ro разряда неуправляемого преобразователя прямого кода в дополнительный является (i+l)-M разрядом входа, первого операнда устройства, вход (п+2)го разря/1;а второго слагаемого q-ro (п+2)-разрядного сумматора соединен с прямым выходом старшего знакового разряда (q-1)- го (п+2)-разрядного сумматора, вход i-ro разряда второго слагаемого пер- рого (п+2)-разрядного су матора соединен с i-M разрядом входа первого операнда устройства, выход нулевого разряда неуправляемого преобразователя прямого кода в дополнительньгй соединен, с входом переноса первого (п+2)-разрядного сут-и-гатора, о т л и- ч а 10 щ е е с я гем, что, с целью расширения функциональньЕ возможностей устройства за счет реализации онеращш извлечения квадратного корнЯу устройство содержит два .- тора, п-разрядный сумматор, блок коррекции, блок устранения сбоев и одно- вибратор, причем первый инфорнацион- ньй вход первого ко1- мутатора является входом второго операнда устройства, второй информационный вход нерво

СОво-

о - вайчем ка

: подключен к инверсному выходу знакового разряда i-ro (п+2)-разрядного сумматора и i-му разряду второго информациониого входа второго коммутатора, выход которого является выходо результата устройства, i-й разряд выхода первого коммутатора подключен к i-му разряду информационного входа всех управляемых преобразователей прямого кода в дополнительный, второй вход блока формирования знака частного подключен к (п+1)-му разряду выхода первого коммутатора, (п+1)-й разряд первого информационного входа которого является входом знака второго,операнда устройства.

2, Устройство по п. 1, отли- чГ а ю щ 8 е с я тем, что, блок корреции содернсит входные одновибраторы, две группы элементов И, триггеры и выходной одновибратор, причем i-й разряд информационного входа блока коррекции подключен к входу (2i-2)- го входного одновибратора и информационному входу i-ro триггера, выход первого входного одновибратора подключен к входу третьего входного одновибратора, выходы (2k-2)-ro и (2k-1)-ro (, n-1) входных одно- вибраторов подключены соответственно к первому и второму входам (k-1)- го элемента И первой группы, вход (2k-l)-ro входного одновибратора подключен к выходу (k-l)-ro элемента И первой группы и (k+1)-M входам k-x элементов И второй группы, первые входы которых объединены и подключены к первому входу первого элемента И второй группы и выходу пер1к

15

78840 8

вого входного одновибратора, первый вход п-го элемента И второй группы подключен к выходу (2п-2)-го входного одновибратора, вторые входы эле5 ментов И второй группы подключены к входу установки первого триггера и управляющему входу блока коррекции, с третьего по (п+1)-й входы п-го элемента И второй группы подключены со 0 ответственно к первому по (п-1)-й выходам элементов И второй группы и входам установки с второго по п-й триггеров соответственно, выходы триггеров являются соответствующими разрядами выхода текущего результата блока коррекции, выход п-го элемента И второй группы подключен к входу выходного одновибратора, выход которого является выходом признака окончания операции блока коррекции.

3. Устройство по пп. 1 и 2, о т - личающееся тем, что блок устранения сбоев содержит п разря- дов,причем каждый i-й разряд (, п) содержит два одновибратора, элемент задержки, элемент И и элемент РШИ, причем входы одновибраторов соединены с входом элемента задержки и с i-M разрядом входа блока устра30 нения сбоев, выход первого одновибратора подключен к первому входу элемента И, второй вход которого подключен к выходу элемента задержки, а выход элемента И - к первому входу эле35 мента ИЛИ, второй вход которого подключен к вьпсоду второго одновибратора, выход элемента ИЛИ является i-м разрядом выхода блока устранения сбоев.

20

25

// п

llf

Фмг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1986 |

|

SU1322271A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для извлечения квадратного корня | 1982 |

|

SU1136155A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1160403A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для вычисления квадратного корня | 1985 |

|

SU1283756A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для умножения 12N-разрядных двоичных чисел | 1988 |

|

SU1589271A1 |

| Матричное устройство для извлечения квадратного корня | 1985 |

|

SU1260951A1 |

| Арифметическое устройство | 1979 |

|

SU860065A1 |

Изобретение относится к вычисли- тельной технике и может быть использовано для аппаратного выполнения операций деления и извлечения квадратного корня в универсальных и специализированных вычислительных машинах. Цель изобретения - расширение функциональных возможностей вычислительного устройства путем реализации операции извлечения квадратного корня. Для достижения этой цели устрой-, ство содержит два коммутатора, сумматор, блок коррекции, блок устранения сбоев и одновибратор. При работе, устройства операнд, из которого извлекается корень, и операнд-делитель подаются на два информационных входа первого коммутатора, который уп- равляетйя сигналом типа операции, После запуска одновибратора в блоке коррекции начинают последовательно формироваться приближения квадратного корня. Операция продолжается до момента вьфаботки выходным одиовиб- ратором блока коррекции сигнала об окончании операции. 2 з.п. ф-лы, 3 ил. I С ю 00 00

SUil

27

J(7

{t}

Составитель И, Захаревич Редактор Л. Гратилло Техред В.Кадар, Корректоре. Шекмар

Заказ 6839/47 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж--35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для извлечения квадратного корня | 1979 |

|

SU857981A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Алексенко А.Г., Шагурин И.И | |||

| Микросхемотехника | |||

| М.: Радио и связь, 1982, с | |||

| Аппарат для радиометрической съемки | 1922 |

|

SU124A1 |

| Коломбет Е.А | |||

| Таймеры | |||

| М.: Радио и связь, 1983, с | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Алексенко А.Г | |||

| Основы микросхемотехники | |||

| М.: Советское радио, 1977, с | |||

| Приспособление для съемки жилетно-карманным фотографическим аппаратом со штатива | 1921 |

|

SU310A1 |

| Устройство для деления двоичных чисел | 1978 |

|

SU748410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-23—Публикация

1985-06-14—Подача