(54) УПРАВЛЯЕМЫЙ АРИФМЕТИЧЕСКИЙ МОДУЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1980 |

|

SU903865A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1495782A1 |

| Двоично-десятичное арифметико-логическое устройство накапливающего типа | 1981 |

|

SU1024904A1 |

| Накапливающий сумматор | 1979 |

|

SU920708A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Управляемый арифметический модуль | 1978 |

|

SU802961A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для арифметической и логической обработки двоичных и двоично-десятичных @ -разрядных чисел | 1980 |

|

SU962922A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для арифметической илОгичЕСКОй ОбРАбОТКи дВОичНыХчиСЕл | 1979 |

|

SU842795A1 |

t

Изобретение относится, к вычислительной технике и может использоваться при построении различных узлов и устройств ЭВМ.

Известен управляемый арифметический модуль, содержащий четыре инфор- , мационных входа и шесть управляющих входов, два выхода, триггер и логические элементы И, ИЛИ, НЕ l.

Недостатками данного управляемого арифметического модуля являются ограниченные возможности по реализации математических операций, что ухудшает характеристики конструируемых на его основе узлов и устройств. Кроме того, модуль сложен в управлении.

Наиболее близким к предлагаемому по технической сущности является управляемый арифметический модуль, содержащий триггер, по два элемента И, ИЛИ и РАВНОЗНАЧНОСТЬ, два коммутатора, три информационных входа, . вход переноса, вход разрешения выполнения операции, девять управляющих входов и два выхода, причем управлягацие входы первого коммутатора подключены к управляющим входам модуля, а его информационные входы - к информационным входам модуля, выход первого коммутатора соединен со входом первого элемента равнозначность, второй вход которого является управляющим входом модуля, а выход соединен с управляющим входом второго к,оммутатора, второй управлякхций вход которого соединен с выходом второго элемента равнозначность, первый вход которого является управляющим входом модуля, а второй соединен с выходом триггера, счетный вход которого соединен с выходом первого элемента ИЛИ, первый вход которого соеди.нен со входом переноса.устройства, а второй о выходом второго коммутатора, информационные входы которого подключены к управляющим.входам модуля,а его стробирукхцнй вход соединен со входом разрешения вьшолнения операции, входы первого элемента И соединены со входомпереноса модуля, с выходом второго элемента равнозначность и с первым входом второго.элемента И, второй вход которого соединен с выходом второго элемента равнозначность, третий вход является управляющим входом модуля, а его четвертый вход подключен ко входу разрешения выполнения операции.

выходы элементов И соединены со входами второго элемента ИЛИ, выход которого является выходом переноса устройства, а выход триггера является выходом результата устройства

12

Недостатком данного устройства , является ограниченный набор выполняе.мых математических операций. Это приводит к уменьшению производительности узлов и устройств ЭВМ, конструируемых на основе этого модуля при выполнении ими сложных математических операций.

Цель изобретения - расширение функциональных возможностей путем увеличения набора математических операций, производимых управляемым арифметическим модулем.

Поставленнося цель достигается тем, что управляемый арифметический модуль, содержащий триггер, элемент ИЛИ и два мультиплексора, настроечные входы первого из которых соединены соответственно с управляющими входами, первой группы модуля, а его входы - с информационными входами модуля, выход триггера является выходом результата модуля, а его счетный вход соединен с выходом элемента ИЛИ, первый вход которого соединен со входом переноса модуля, а второй вход - с выходом второго мультиплексора, информационные вхо,да которого соединены соответственно с управляющими входами второй группы Модуля, а его стробирующий вход соединен со входом разрешения выполнения операции модуля, модуль содержит третий мультиплексор, выход которого является выходом переноса модуля, -информационные входы соединены соответственно с управляющими входами третьей группы модуля, а настроечные входы попарно объединены с настроечными входами второго мльтиплексора и подключены соответственно к выходу триггера и первого мультиплексора, стробирующий вход третьего мультиплексора соединен со .входом разрешения выполнения операции модуля.

Схема такого устройства помимо сдвигов хранимой информацииi выполнния логических операций и суммирования реализует также операции одновременного выполнения двух произвольных логических операций со сложением их результатов, т.е. устройство реализует все операции типа S q (А,В) + fj{A,B), где ,В) и fj (А,в) - произвольные логические функции операндов А и В. При этом эти операци могут реализоваться одновременно со сдвигом информации в устройстве.

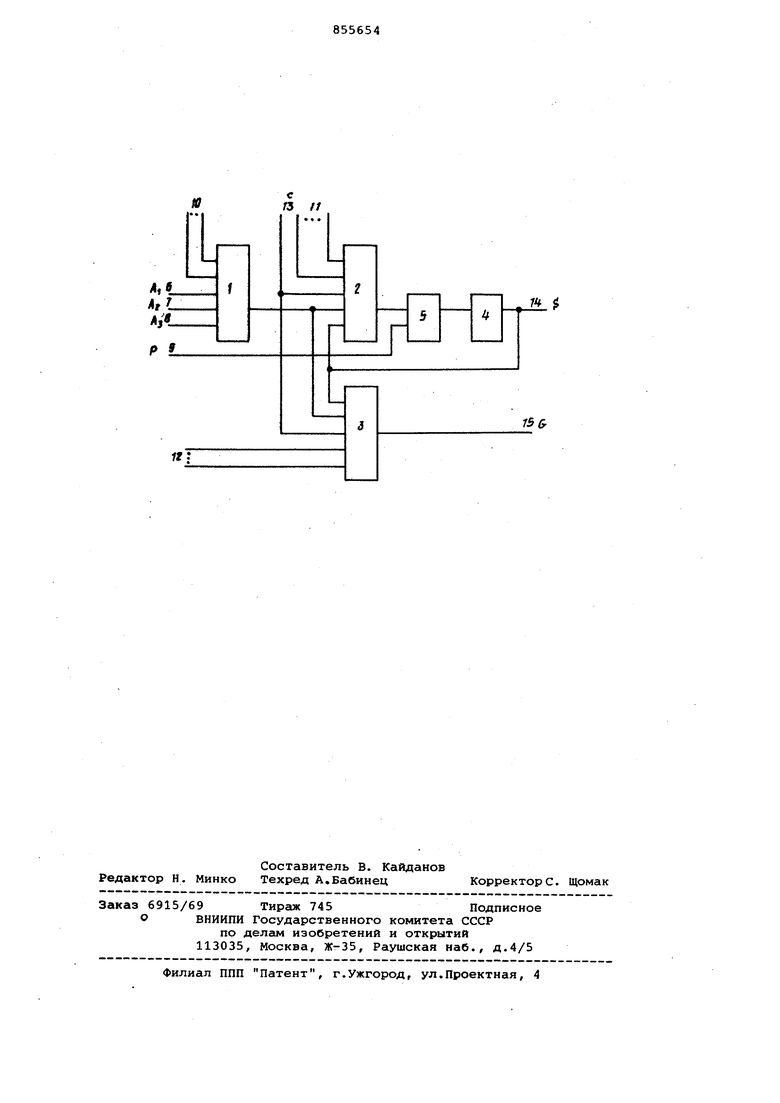

На чертеже представлена схема управляемого арифметического модуля

Устройство содержит мультиплексоры 1-3, триггер 4, элемент ИЛИ 5, информационные входы 6-8, вход 9 переноса, группы управляющих входов 10-12, вход 13 разрешения выполнения операции, выход 14 результата и выход 15 переноса. Управляющие входы коммутатора 1 подключены к управляющим входам 10 устройства, а его ин.формационные входы - к информаци онным входам 6-8 устройства. Выход триггера 4 являетаг информациЪннЕлм выходом устройства, а его счетный вход соединен с выходом элемента ИЛИ 5, один вход которого подключен ко входу 9 переноса устройства, а его второй вход соединен с выходом мультиплексора 2. Выход мультиплексора 3 является выходом 15 переноса устройства, а его управляющие входы попарно объединены с управляющими входами мультиплексора 2 и подключены соответственно к выходу мультиплексора 1 и к выходу триггера 4. Информационные входы мультиплексоров 2 и 3 подключены к группам управляющих входов 11 и 12 устройства соответственно, а их стробирующий вход ко входу 13 разрешения выполнения операции.

Устройство работает следующим образом.

На входы 6-9 устройства подаются соответственно сигналы: вход 6 сигнал А для связи со старшим разрядом в п-разрядном устройстве, вход

7- сигнал А разряда операнда, вход

8- сигнал АЗ для связи с млгщшим разрядом в п-разрядном устройстве, вход 9 - сигнал переноса Р. С информационного выхода 14 модуля снимается сигнал S результата операции, а

с выхода 15 - сигнал Q, который является возникающим сигналом переноса в старший разряд. Группа управляющих входов 10 устройства управляет коммутацией информационных входов 6-8 и подключает один из сигналов А, АЗ. или А 3 ко входу функциональной части модуля.функциональная часть с помощью мультиплексоров 2 и 3, триггера 4 и.элемента 5 путем настройки по группам управляющих входов 11 и 12 реализует любую из математических операций типа S fy (А,в) + f,,-(A,B), где f(A,B) и f (А,В) произвольные логические функции переменных А и В, одна из которых (например,А) снимается с выхода мультиплексора 1, а другая переменная (например, в) перед началом операции заносится в триггер 4. При этом мультиплексор 3 с помощью группы настроечных входов 12 для выполнения устройством некоторой операции настраивается на логическую функцию, соответствующую возникакхаему сигналу переноса О, т.е. на логическую функцию Q Суй ,B), а Cj fj(A,B). Коммутатор 2 с помощью группы управляющих входов 11 настра ивается на реализацию в нем логичес кой функции возбуждения триггера, соответствующей требуемой математической операции. Код настройки муль типлексоров 1 и 2, а также реализуемые ими логические функции легко находятся по таблице истинности тре буемой математической операции, сос тавляемой без учета входного сигнала переноса Р. Сигнал G разрешения выполнения операции является импуль ным и подается одноразово на вход 1 устройства при выполнении любой из операций. Длительность этого сигнала выбирается из условия обеспечени устойчивой работы Т-триггера устройства. При использовании в устрои стве мультиплексоров четырех переменных схема модуля имеет десять управляющих входов. В целом схема управляемого арифметического модуля с учетом работы мультиплексора 1 позволяет реализовать в п-разрядном устройстве следу щий набор математических операций: операции типа 5 )+Л- (А,В) , то же 5 )Л.(В,В) S ffQB,B)+6(B,B), где А - код входного операнда, В - код хранимого в триггере операнда. В число указанных математических операций входят операции сложения двух операндов, логической обработки двух операндов, сдвига операнда одновременной логической обработки двух операндов и сложения полученных результатов, логические и арифметические операций над кодом операнда В и сдвинутыми кодами этого операнда. Всего устройство реализует путем настройки порядка 700 различных операций указанных типов, что значительно расширяет набор математических операций, производимых .управляемым арифметическим модулем. Это позволяет на основе данного устройства конструировать разнообразные устройства обработки цифровой информации,а также повысить производительность конструируемых устройств при выполнении сложных математических операций за счет числа одновременно выполняемых операций. Формула изобретения Управляемый арифметический модуль, содержащий триггер, элемент ИЛИ и два мультиплексора, настроечные вхо- ды первого из которых соединены соответственно с управляющими входами первой группы модуля, а его входы с информационными входами модуля, выход триггера является выходом результата модуля, а его счетный вход соединен с выходом элемента ИЛИ, первый вход которого соединен со входом переноса модуля, а второй вход - с выходом второго мультиплексора, информационные входы которого соединены соответственно с управляющими входами второй группы модуля, а его стробирующий вход соединен со входом разрешения выполнения операции модуля, отличающийся т:&Л( что, с целью расширения функционсшьных возможностей за счет увеличения набора математических операций, производимых управляемым а1Л1фметическим модулем,модуль содержит третий мультиплексор, выход которого является вйход( переноса модуля, инфорМсщионные входа соединены соответ- ственно с управляющими входами третьей группы модуля, а настроечные входы попарно объединены с настроечны- ми входами второго мультиплексора и подключены соответственно к ВЫХОДУ тонггеоа и пеового мультиплексора, стробирующий вход третьего мультиплексора соединен со входом разрешения выполнения .операции модуля. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 4Ъ73в7, кл. G Об F 7/50, 1973. 2.Авторское свидетельство СССР 2682661, кл.а 06 F 7/50, 1У79 (прототип).

Ю

If-.

J±

75 &

Авторы

Даты

1981-08-15—Публикация

1979-11-12—Подача