1

Изобретение относится к вычислительной технике, в частности к устройствам микропрограммного управления цифровых вычислительных устройств.

Известно микропрограммное устройство управления, содержащее два запоминающих блока, два элемента И, два триггера, два коммутатора с соответствующими взаимосвязями 1J.

Недостатком известного устройства является невозможность прерывать ход микропрограммы требованиями внешних пользователей с сохранением адреса возврата на адресном регистре запоминающего блока.

Наиболее близким по технической сущности к предлагаемому является микропрограммное устройство управления, содержащее два запоминающих блока, соединенных с соответствующими регистрами адреса, два блока проверки условий, два элемента И, выход каждого соединен со входом соответствующего запоминающего блока. Устройство также содержит два триггера блокировки, первый вход которого соединен с третьим выходом соответствующего запоминающего блока, выход сое.динен с другим входом соответствующего элемента И Г21 .

Недостаткрм известного устройства является то, что оно не позволяет осуществить динамический режим считывания микрокоманды, а также не предусматривает возможность прерывания хода микропрограммы требованиями внешних пользователей микропрограммных запоминающих блоков с сохранением адреса.возврата на адресном регистре запоминающего блока,не испозуя для этой цели буферный регистр.

Цель изобретения - расширение функ-циональных возможностей за счет обеспечения прерывания микропрограмм с сохранением адреса возврата.

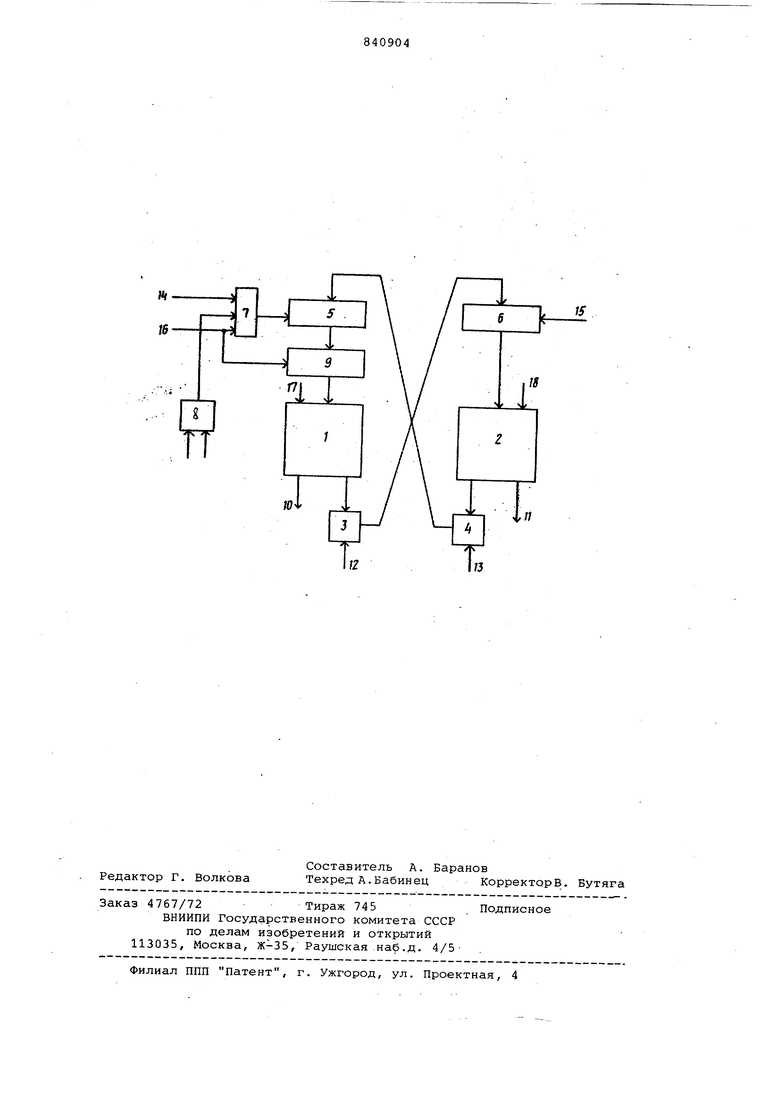

Поставленная цель достигается тем что в устройство, содержащее два регистра адреса, два запоминающих блока, элемент запрета, элемент И, два. блока проверки условий, первые входы которых являются входами условий устройства, вторые входы - соединены соответственно с первыми выходами певого и второго запоминающих блоков, вторые выходы которых являются выходами устройства, первые входы первого и второго регистров адреса соединены соответственно с выходами второго и первого блоков проверки условий, второй вход второго регистра ад;реса является входом записи устройст ва, первые входы первого и второго запоминающих блоков соединены со входами считывания устройства, второй вход второго запоминающего блока соединен с выходом второго регис ра адреса, первый и второй входы эле мента запрета являются установочным входами устройства, выход элемента запрета соединен с первым входом эл мента И, второй вход которого являе ся входом записи устройства, введена группа элементов И, причем управляю щий вход устройства соединен с третьим входом элемента И и с первыми входами, элементов И группы, выходы которых Соединены с вторым входом первого запоминающего блока, вторые входы элементов И группы соединен с выходом первого регистра адреса, а второй вход первого регистра адре са соединен с выходом элемента И. На чертеже схематично представле но прёдлах-аемое устройство, Устройство содержит запоминающие блоки 1 и 2, блоки 3 и 4 проверки условий, регистры 5 и 6 адреса, элемент И 7, элемент 8 запрета, группу элементов И 9, выходы 10 и 11 устройства, входы 12 и 13 условий, входы 14 и 15 35ПИСИ и вход 16 управляю щий, входы 17 и 18 считывания. Работа устройства рассматривается в трех режимах: автоматическом, динамического долбления и режиме приостанова. ( В автоматическом режиме на второй вход элемента И 7 с выхода элемент 8 запрета и на третий вход элемента И 7 по управляющему входу 16 пода ются сигналы, .разрешающие прохождение сигналов записи, поступающих по входу 14 на первый вход элемента И 7, на выход элемента И 7 и на управляющий вход регистра 5. Сигнал записи осуществляет запись кода в первый регистр 5 адреса, сигнал с выхода которого поступает на вход группы элементов И 9. На управляющие входы элементов И группы 9 по управляющему входу 16 поступает сигнал разрешающий прохождение гщреса через группу элементов И 9 на вход первого запоми нающего блока 1, на управляющие входы которого поступают сигналы считываний по входу 17. Считанная в соответстаии с адресом микрокоманда реализует управляющие микрооперации, по выходу 10, а адресная часть микрокоманды выдается на второй вход первого блока 3 проверки условий, на порвый вход которого подается сигнал по входу условий, определяемый логическими условиями ветвления. При tiaличии сигнала записи на входе 15 {)егистра 6, сформированный адрес команды второго запоминающего бл(-.а 2 с выхода первого блока 3 проверки условий записыдается во второй регистр 6 адреса, откуда вьщается на вход второго запоминающего блока. Сигналами, поступающими по входу 18 на управляющий вход второго запоминающего блока 2, производится считывание в соответствии с адресом микрокоманды реализующей управляющие микрооперации по выходу 11, адресная часть микрокоманды, указывающая на адрес следующей микрокоманды первого запоминающего блока 1, выдается на второй вход второго блока 4 проверки условий, на первый вход которого поступает управляющий сигнал по входу 13. С выхода второго блока 4 проверки условий информация выдается на вход регистра 5 адреса. В последующих машинных циклах производится попеременное считывание микрокоманд сигналами двух фаз, то с одного, то с другого запоминающего блока. В режиме динамического долбления ячейки запоминакнцего блока, элемент 8 запрета устанавливается в состояние запрета. До управляющему входу 16 на третий вход элемента И 7 и на управляющий вход группы элементов И 9 подается разрешаквдий сигнал. Сигнал с выхода элемента 8 запрета запрещает прохождение сигналов записи, поступающих по входу 14 записи регистра . 5 на первый вход элемента И 7, на выход элемента И 7, соединенный с управляющим входом первого регистра 5 адреса. Состояние регистра 5 до снятия условий запрета с элемента 8 не изменяется. Сигналы с выхода регистра 5 через группу элементов И 9 поступают на вход запоминающего блока 1, где выбирается микрокоманда, подлежащая считыванию. В каждом машинном цикле с первого запоминающего блока 1 считываётся одна и та же микрокоманда, которая реализует одни и те же управлякадие микрооперации и устанавливает один и тот же адрес микрокоманды, считьгааемой по сигналу на входе 18 со второго запоминающего блока 2. При снятии условий динамического долбления элемент 8 запрета устанавливается в исходное состояние, соответствующее автоматическому режиму работы, в результате этого на второй вход элемента И 7 подается разрешающий сигнал. С выхода второго запоминающего блока 2 через второй блок 4 проверки условий в первый регистр 5 адреса, на управляющий вход которого с выхоа элемента И 7 подается сигнал записи первого регистра 5 адреса, записыается код адреса новой микрооперации, При работе процессора с внешними ользователями возникает необходи- . ость прерывания хода микропрограммы о требованию.внешних пользователей.

Это осуществляется внесением фиксированного адреса на группу элементов И 9,

После записи адреса микрокоманды не первый регистр 5 адреса на вход 16 подается сигнал управления, который, поступая на третий вход элемента И 7, запрещает прохождение импульсов записи, которые подаются на вход 14 условий регистра 5. Кроме того, сигнал, подающийся по управлякхцему входу 16, фиксирует вход группы элементов И 9, связанных с выходом регистра 5 и устанавливает на выходе элементов И группы 9 фиксированный адрес микропрогракпиы обработки требований внешних устройств. Фиксированный адрес подается на входы блока 1 по сигналу, поступающему на вход-17, выбирается микрокоманда, которая реализует микрооперации управления обработки требований внешних устройств по выходу 10 и устанавливает через блок 3 на втором регистре 6 адреса адрес микрооперации, считываемой из второго запоминакицего блока 2 по сигналу на входе IS. Считанная микрокоманда реализует управляющие микрооперации по выходу 11.

Код на первом регистре 5 адреса не изменяется, так как управлякщий вход регистра 5 заблокирован сигиалом поступающим на вход 16. При сняГии сигнала с входа 16 разблокировывается вход группы элементов И 9 и адрес микрокоманды, соответствующий точке выхода из микропрограммы обработки требований внешних устройс из первого регистра 5 адреса через группу элементов И 9 поступает на входы первого запоминающего блока 1. В дальнейшем работа происходит в автоматическом режиме.

Если микропрограмма обработки требований внешних устройств осуществляется более, чем за один машинный цикл, то сигнал по управляющему входу 1.6, блокирующий сигналы записи по входу 14 не снимается, на группе элементов И 9 устанавливается фиксированный адрес следующей ячейки запоминающего блока.

В предлагаемом устройстве возможно осуществление режима ожидания при блокировке сигналов по входам 17 и 18 считывания до прихода сигнала логических условий, определяющих выход из режима ожидания.

Таким образом, предлагаемоеустройство позволяет расширить функциональные возможности микропрограммного устройства управления.

Формула изобретения

Микропрограммное устройство управления, содержёицее два регистра адреса, два запоминающих блока, элемент запрета, элемент И, два блока проверки условий, первые входы которялх являются входг1ми условий устройства, вторые входы - соединены соответственно с первыми выходами первого и второго запоминающих блоков, вторые выходы которых являются выходами устройства, первые входы первого и второго регистров адреса соединены соответственно с выкодг1Ми второго и первого блоков проверки условий, второй вход второго регистра ёщреса является входом записи устройства, первые входы первого и второго запоминащих блоков соединены-с входами считывания устройства, второй вход второго запоминаквдего блока соединен с выходом второго регистра адреса, первый и второй входы элемента запpeta являются установочными входами устройства, выход элемента запрета . соединен с первым входом элемента И, второй вход которого является входом записи устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения прерывания микропрограмьвл с сохранением адреса возврата, в.негр введена группа элементов И, причем управляющий вход устройства соединен с третьим входом элемента И и с первыми входами элементов И группы, выходы которых соединены с вторым входом первого запоминающего блока, вторые входы элементов И группы соединены с выходом первого регистра адреса, а второй вход первого регистра адреса соединен с выходом элемента И.

Источники информации, принятые во внимание при эк.спертизе

1.Авторское свидетельство СССР 451080, кл. G 06 F 9/12, 1972.

2.Авторское свидетельство СССР 437072, кл. С 06 F 9/12, 1973 (прототип).

IS

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Адаптивное микропрограммное устройство управления | 1980 |

|

SU934471A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134936A1 |

Авторы

Даты

1981-06-23—Публикация

1977-06-24—Подача