(54) РЕВЕРСИВНЫЙ БУФЕРНЫЙ РЕГИСТР СДВИГА

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный буферный регистр сдвига | 1978 |

|

SU780045A1 |

| Ячейка памяти для буферногоРЕгиСТРА | 1979 |

|

SU799010A2 |

| Реверсивный регистр сдвига | 1989 |

|

SU1642527A1 |

| Асинхронный последовательный регистр | 1990 |

|

SU1805501A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Реверсивный регистр сдвига | 1990 |

|

SU1721632A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| Реверсивный регистр сдвига | 1980 |

|

SU960955A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037272C1 |

| МОДУЛЬ ДЛЯ ПЕРЕДАЧИ И ВЕЩАНИЯ СООБЩЕНИЙ В МАТРИЧНОМ КОММУТАТОРЕ | 2003 |

|

RU2249848C2 |

t

Изобретение относится к вычислительной технике и может быть использовано для построения магазинной памяти вычислительных устройств.

Известен регистр сдвига, содержащий ячейки памяти, каждая из которых содержит три триггера 1.

Однако увеличение информационной емкости регистра сдвига требует больших аппаратурных затрат.

Наиболее близким к предлагаемому изобретению по технической сущности является реверсивный буферный регистр сдвига, содержащий ячейки памяти, причем входы i-й ячейки памяти соединены с выходами (1-1)-ой, ()-ой, (1-3)-ей, ({ + 1)-ой, (i + 3)-ей ячеек, каждая ячейка которого содержит три элемента И-ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ соединен с первыми входами второго и третьего элементов И-ИЛИ-НЕ, выход второго элемента И-ИЛИ-НЕ соединен с первым входом первого и вторым входом третьего элемента И-ИЛИ-НЕ, выход которого подключен ко вторым входам первого и второго элементов И-ИЛИ-НЕ, третьи входы

элементов И-ИЛИ-НЕ соответственно соединены со входами и выходами ячейки памяти 2.

Недостатком известного реверсивного буферного регистра является избыточное количество оборудования (для хранения m разрядов кода регистр должен содержать п 3 ячеек памяти и, как следствие этого сравнительно низкое быстродействие.

Цель изобретения - увеличение информационной емкости и повыщение его быстродействия.

Поставленная цель достигается тем, что в реверсивном буферном регистре сдвига, содержащем п ячеек памяти (гдеп - число разрядов), причем входы каждой йапример i-ой ячейки памяти, соединены с выходами (1-2)-ой, (1-1)-ой и (1-1)-ой ячеек памяти соответственно, 1ой ячейки памяти подключен к первым входам (1-2)-ойи (/ 1)-ой ячеек памяти, вторые входы которых соединены с выходом (1-3)-ей ячейки памяти, вторые входы i-ой ячейки памяти

соединены с выходами (i -Ь 2) -ой и (i -f + 4)-ой ячеек памяти, третий вход i-ой ячейки памяти подключен к выходу (i + 1)-ой

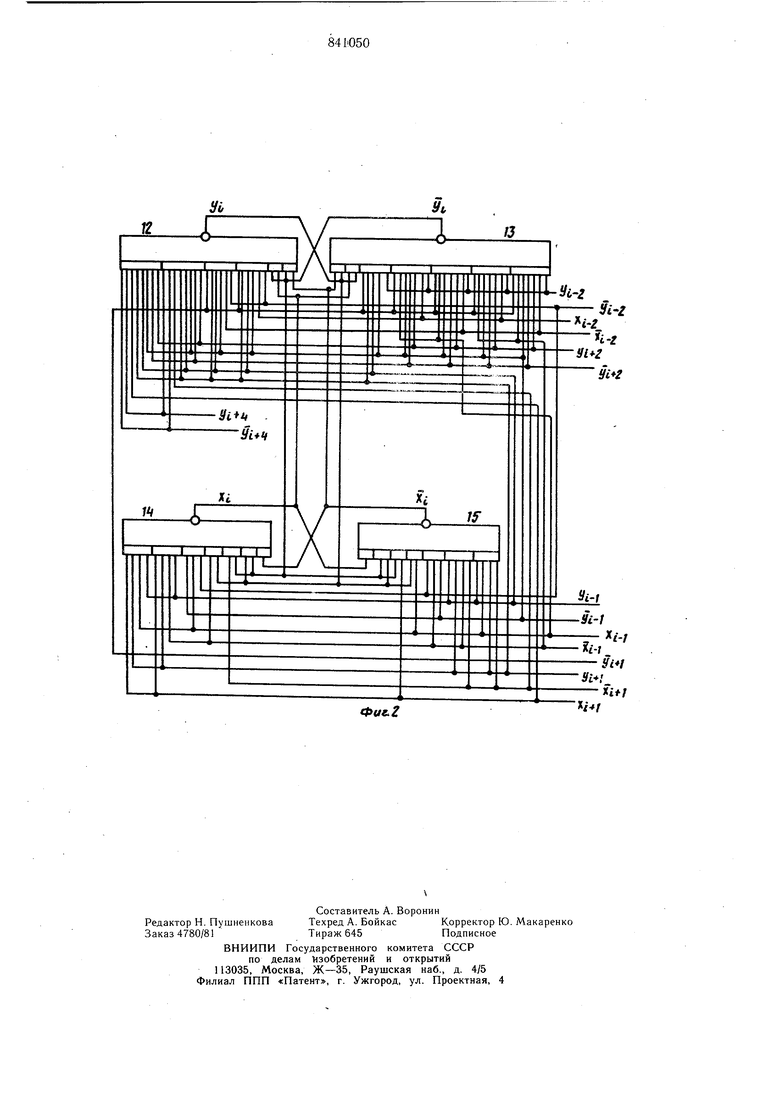

ячейки памяти, выход i-ой ячейки памяти соединен .с первыми входами (i + 1)-ой и (i + 2)-ой ячеек памяти, выход (i + 2)-ой ячейки памяти подсоединен к :первым входам (i + 3) и (i + 4)-ой ячеек памяти, вторые входы (i +2)-ой и (i 4)-ой соединены с выходом (1+6)-ой ячейки памяти, вторые входы (i + 1)-ой и (i + 2)-ой соединены с выходом (i + 3)-ой ячейки памяти. Каждая ячейка памяти содержит четыре элемента И-ИЛИ-НЕ, выход первого из которых соединен с первыми входами второго, третьего и четвертого элементов И-ИЛИНЕ, выход второго элемента И-ИЛИ-НЕ подключен к первому входу первого элемента И-ИЛИ-НЕ и ко вторым входам третьего и четвертого элементов И-ИЛИ-НЕ, вторые входы первого и второго элементов И-ИЛИ-НЕ и третий вход третьего элемента И-ИЛИ-НЕ соединены с выходом четвертого элемента И-ИЛИ-НЕ, третьи входы первого, второго и четвертого элементов И-ИЛИ-НЕ подключены к выходу третьего элемента И-ИЛИ-НЕ.

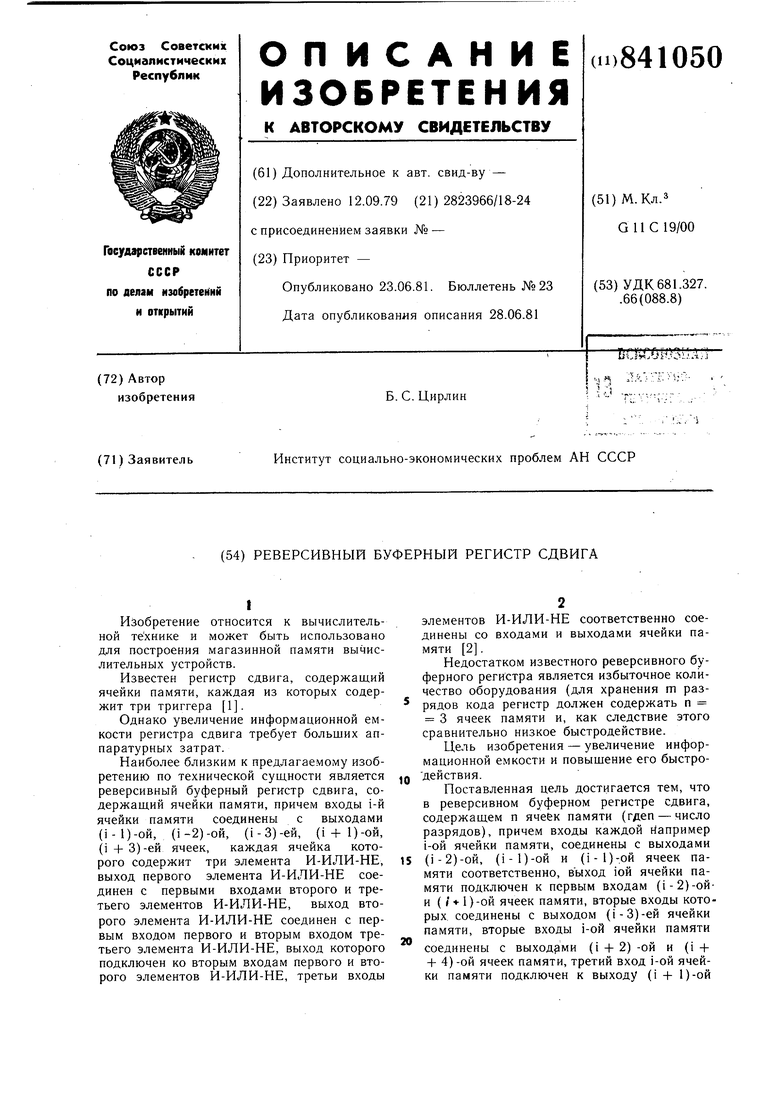

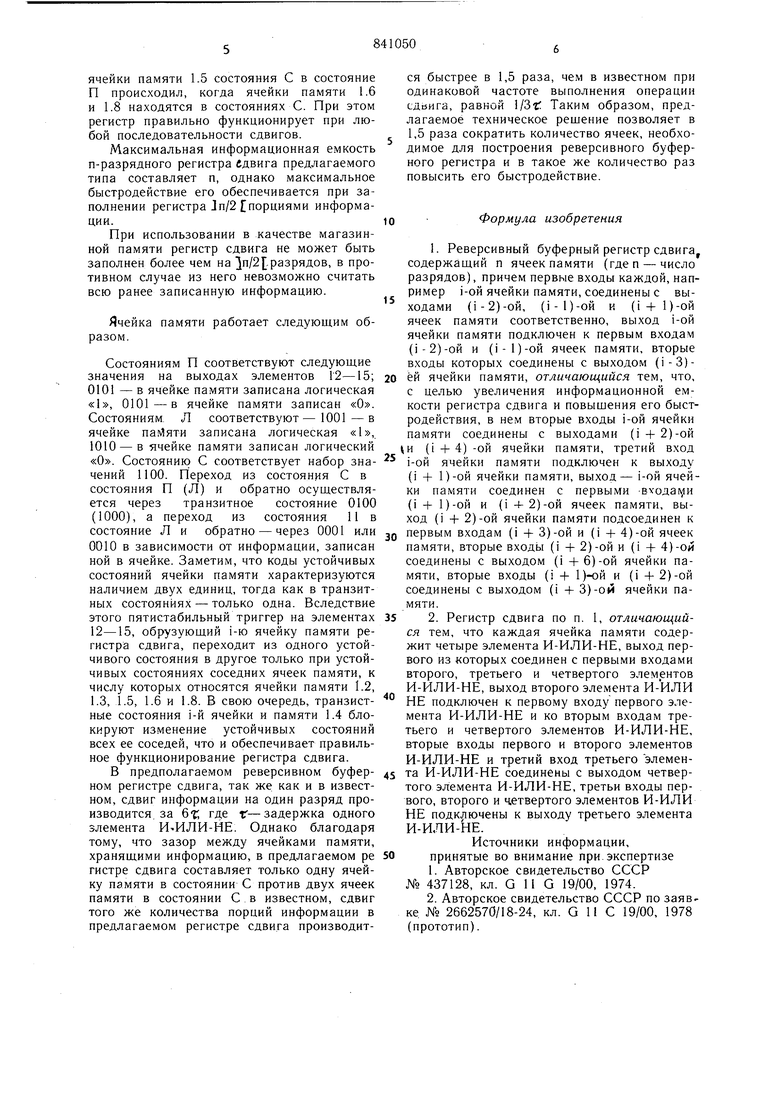

На фиг. 1 изображена функциональная схема реверсивного буферного регистра сдвига; на фиг. 2 - функциональная cxeivia ячейки памяти.

Реверсивный буферный регистр сдвига содержит ячейки памяти 1.1 - l.n, входы 2- 6 i-ой ячейки памяти, например, 1.4, выходы 7-11 соответственно ячеек памяти 1.2- 1.3, 1.5-1.6 и 1.8. Ячейка памяти содержит элементы И-ИЛИ-НЕ 12-15.

Для пояснения работы регистра обозначим два состояния, при которых ячейка памяти может передавать влево записанную в нее информацию (логическую «1 или «О) через Л, два состояния, соответствующие передаче вправо, через П, а состояние, в котором информация в ячейке памяти стерта, через С.

Если в соседних ячейках регистра имеется комбинация состояний вида СЛСЛСЛССС или СПСПСПССС, информация в этих.ячейках не продвигается, и они сохраняют свои состояния. Если же имеется комбинация вида СПСЛСЛССС, происходит последовательнгая смена состояний Л состояниями П: СПСПСЛССС-СПСПСПССС, т.е. переход i-й ячейки памяти 1.4 из состояния Л в состояние П происходит, если ячейки памяти L2, 1.3 и 1.5 находятся в состояниях П,С и С соответственно. Последовательная смена состояний П состояниями Л происходит, когда имеется комбинация вида ЛСПСПСС (ССПСПССС): ЛСЛСПССС-ЛСЛСЛССС т.е. переход i-й ячейки памяти 1.4 из состояния П в состояние Л происходит,если памяти 1.2, 1.3 и 1.5 находятся в состояниях Л (С),. С.С соответственно. В обоих этих случаях продвижения информации также не происходит.

Сдвиг вправо вызывается комбинацией состояния вида ЛПСПСПССС. При этом

последовательно возникают следующие комбинации: ЛПЛПСПССС-ЛСЛПЛПССС- ЛСЛСЛСПЛСС-ЛСЛСЛСЛСС, т.е. переход i-й ячейки памяти 1.4 из состояния С в состояние Л происходит, если ячейки памяти 1.2 и 1.3 находятся в состояниях Л и П соответственно, а переход из П в С - когда ячейки памяти 1.3 и 1.5 находятся в состояниях Л.

Сдвиг влево вызывается комбинацией состояний вида ССЛСЛСЛССС. При этом последовательно возникают комбинации

сплел слссс-спсслслссс-спсплсЛССС-СПСПССЛССС-СПСПСПЛССССПСПСПСССС, т.е. переход i-й ячейки памяти 1.4 из состояния С в состояние П происходит, если ячейки памяти 1.3 и 1.5 находятся в состояниях С и Л соответственно.

Управление сдвигом осуществляется из крайней левой ячейки памяти регистра. Сдвиг вправо вплотную сближает ячейки, хранящие информацию в состояниях Л и П соответственно, а сдвиг влево, наоборот, увеличивает зазор Между ячейками, хранящими информацию, с одной до двух ячеек, в которых информация стерта (находящихся в состоянии С). Эти изменения распространяются по регистру слева направо по мере осуществления сдвига информации в ячейках памяти.

Буферные свойства регистра обеспечиваются тем, что как только i-я ячейка памяти 1.4 выполняет операцию сдвига (в нее записывается информация справа или слева) и между этой ячейкой и следующей, хранящей информацию, устанавливается зазор С, i-я ячейка памяти 1.4 готова к следующей операции. При этом сдвиг вправо подготавливает ячейку памяти 1.4 к выполнению сдвига влево (устанавливает ее в состояние Л), а сдвиг влево подготавливает ячейку к сдвигу вправо (устанавливает ее в П).

Возможны четыре случая: а) два подряд сдвига вправо; б) сдвиг вправо следует за сдвигом влево; в) сдвиг влево следует за сдвигом вправо г) два подряд сдвига влево. Во всех случаях первой вьшолняется операция Б ячейках памяти, расположенных правее.

Таким образом, для случая «а имеет место последовательность следующих комбинаций состояний: ЛПСЛПС-ЛПСЛПЛЛПСЛСЛ-ЛПСПСЛ-ЛПЛПСЛ-ЛСЛПСЛ... для ССЛПСП-ССЛПЛП-ССЛСЛПСПЛСЛП-СПССЛП..., для случая ЛПССЛСЛ-ЛПСПЛСЛ-ЛПССССЛ-ЛПЛСПССЛ-ЛСЛПССЛ..., для«г : ССЛССЛСЛССЛСПЛСЛ-ССЛСПССЛ-СПССЛСПЛСПССЛСЛС.... Ситуации, возникающие в случаях «а и «б, требуют,чтобы переход i-й ячейки памяти 1.4 из состояния С в состояние Л происходил, когда ячейки памяти 1.5 и 1.6 находятся в состояниях П(С) и С соответственно, а ситуации, возникающие в случаях «в и «г - чтобы переход i-й

ячейки памяти 1.5 состояния С в состояние П происходил, когда ячейки памяти 1.6 и 1.8 находятся в состояниях С. При этом регистр правильно функционирует при любой последовательности сдвигов.

Максимальная информационная емкость п-разрядного регистра Сдвига предлагаемого типа составляет п, однако максимальное быстродействие его обеспечивается при заполнении регистра Дп/2 порциями информации.

При использовании в качестве магазинной памяти регистр сдвига не может быть заполнен более чем на , разрядов, в противном случае из него невозможно считать всю ранее записанную информацию.

Ячейка памяти работает следующим образом.

Состояниям П соответствуют следующие значения на выходах элементов 12-15; 0101 - в ячейке памяти записана логическая «1, 0101-в ячейке памяти записан «О. Состояниям Л соответствуют-1001-в ячейке записана логическая «1, 1010-в ячейке памяти записан логический «О. Состоянию С соответствует набор значений 1100. Переход из состояния С в состояния П (Л) и обратно осуществляется через транзитное состояние 0100 (1000), а переход из состояния 11 в состояние Л и обратно - через 0001 или 0010 в зависимости от информации, записан ной в ячейке. Заметим, что коды устойчивых состояний ячейки памяти характеризуются наличием двух единиц, тогда как в транзитных состояниях - только одна. Вследствие этого пятистабильный триггер на элементах 12-15, обрузующий i-ю ячейку памяти регистра сдвига, переходит из одного устойчивого состояния в другое только при устойчивых состояниях соседних ячеек памяти, к числу которых относятся ячейки памяти 1.2, 1.3, 1.5, 1.6 и 1.8. В свою очередь, транзистные состояния i-й ячейки и памяти 1.4 блокируют из.менение устойчивых состояний всех ее соседей, что и обеспечивает правильное функционирование регистра сдвига.

В предполагаемом реверсивном буферном регистре сдвига, так же как и в известном, сдвиг информации на один разряд производится, за 6t; где тг-задержка одного элемента И-ИЛИ-НЕ. Однако благодаря тому, что зазор между ячейками памяти, хранящими информацию, в предлагаемом ре гистре сдвига составляет только одну ячейку памяти в состоянии С против двух ячеек памяти в состоянии С в известном, сдвиг того же количества порций информации в предлагаемом регистре сдвига производится быстрее в 1,5 раза, чем в известном при одинаковой частоте выполнения операции сдвига, равной l/3tt Таким образом, предлагаемое техническое рещение позволяет в 1,5 раза сократить количество ячеек, необходимое для построения реверсивного буферного регистра и в такое же количество раз повысить его быстродействие.

Формула изобретения

i-ой ячейки памяти подключен к выходу (i + 1)-ой ячейки памяти, выход- i-ой ячейки памяти соединен с первыми входа1 1И (1 + 1)-ой и (i -I- 2)-ой ячеек памяти, выход (i + 2)-ой ячейки памяти подсоединен к

0 первым входам (1 + 3)-ой и (i -f 4)-ой ячеек памяти, вторые входь (i + 2)-ой и (i + 4)-ой соединены с выходом (1 -ь6)-ой ячейки памяти, вторые входы (i + 1)-ой и (1 -f 2)-ой соединены с выходом (i + 3)-ой ячейки памяти.

5 2. Регистр сдвига по п. I, отличающийся тем, что каждая ячейка памяти содержит четыре элемента И-ИЛИ-НЕ, выход первого из которых соединен с первыми входами второго, третьего и четвертого элементов И-ИЛИ-НЕ, выход второго элемента И-ИЛИ НЕ подключен к первому входу первого элемента И-ИЛИ-НЕ и ко вторым входам третьего и четвертого элементов И-ИЛИ-НЕ, вторые входы первого и второго элементов И-ИЛИ-НЕ и третий вход третьего элемента И-ИЛИ-НЕ соединены с выходом четвертого элемента И-ИЛИ-НЕ, третьи входы первого, второго и четвертого элементов И-ИЛИ НЕ подключены к выходу третьего элемента И-ИЛИ-НЕ.

Источники информации,

принятые во внимание при. экспертизе

I I I I I

Фиг. 1

Авторы

Даты

1981-06-23—Публикация

1979-09-12—Подача