Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при построении приемников информации в последовательных каналах.

Цель предлагаемого изобретения - расширение области применения асинхронно- то последовательного регистра типа pipeline за счет обеспечения параллельного считьг вания информации из этого регистра.

В-предложенном устройстве, как и в устройстве - прототипе 2,. сдвиг информации в регистре осуществляется асинхронно, в режиме запрос-ответ по реальным задержкам элементов регистра и как только (п-1)-й разряд сдвигаемого кода попадает в соответствующую ему позицию - 21-ю ячейку памяти, он через дополнительную (2п+1)-ю ячейку памяти поступает на параллельные информационные выходы до тех пор, пока

последний разряд сдвигаемого кода не попадает через (Зп-1)-ю ячейку памяти на соответствующий параллельный информационный выход регистра, после чего появится сигнал на разрешение считывания на выходе регистра, перевод же регистра в исходное состояние индицируется подачей соответствующего сигнала на вход стирания регистра. Таким образом, введенные отличительные признаки позволяют осуществить параллельное считывание информации в асинхронном последовательном регистре типа pipeline, т.е. расширяет область применения последнего.

Сказанное подтверждает существенность отличий предложенного технического решения.

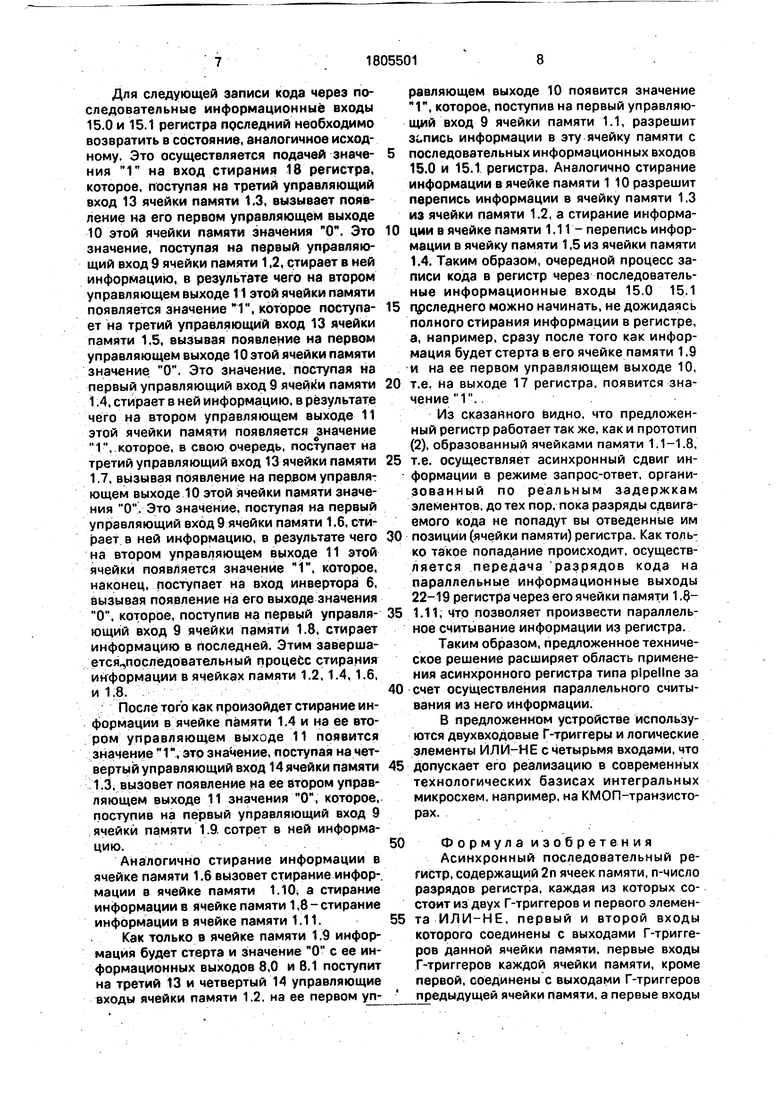

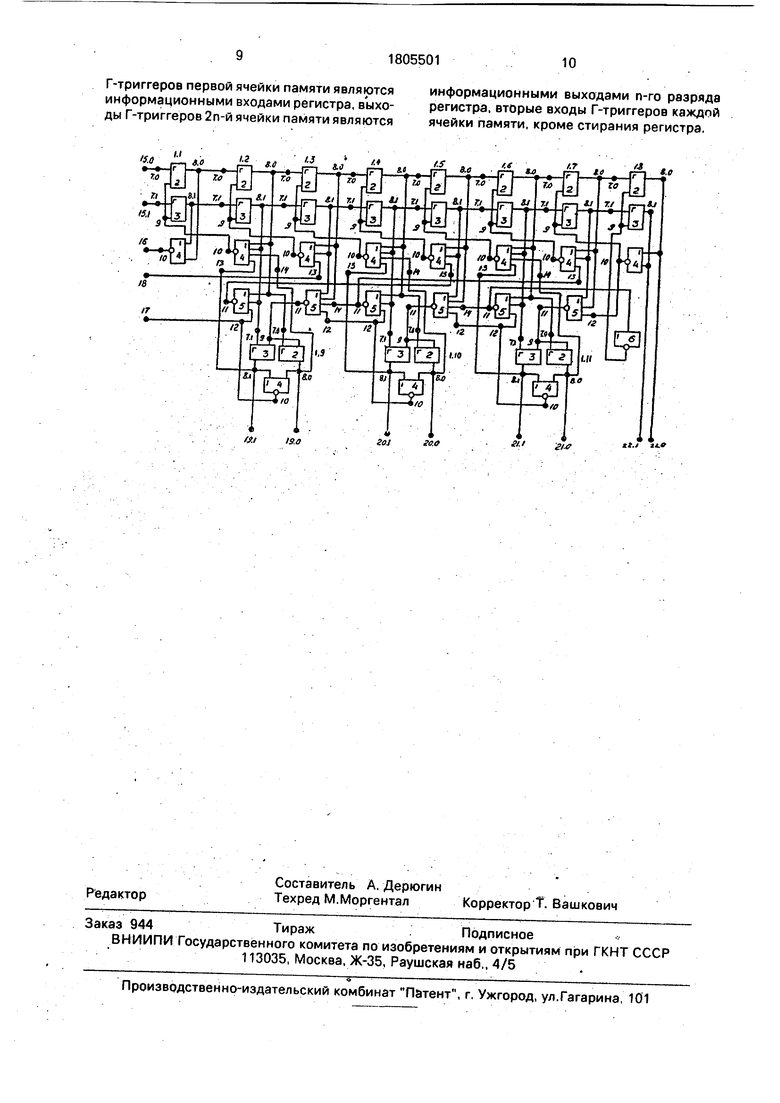

На чертеже представлена функциональная схема четырехразрядного регистра.

Регистр содержит ячейки памяти 1.1- 1.8, каждая из которых состоит из Т-тригге00

о ел ел о

ров 2 и 3 первого элемента И-НЕ 4, ячейки памяти 1.2-1.7 и второго элемента ИЛЙ-НЕ 5, и инвертор 6.

В ячейке памяти информационные входы 7.0 и 7.1 и выходы 8.0 и 8.1 соединены соответственно с первыми входами и выходами ее Г-триггеров 2 и 3, вторые входы которых соединены с первым управляющим входом 9 ячейки памяти, первый 10 и второй 11 управляющие выходы которой соединены с выводами элементов И Л И-НЕ 4 и 5, первый и второй входы которых соединены с выходами Г-триггеров 2 и 3 этой ячейки памяти, третьи входы - с третьим 13 и вторым 12 управляющими входами этой ячейки памяти, а четвёртые входы элементов ИЛИ- НЕ 4 в ячейках памяти 1,2, 1.4 и 1.6. и 5 - в ячейках памяти 1.3 и. 1.5 соединены с четвертым 14 управляющим входом данной ячейки памяти. Последовательные информационные входы 15.0 и 15.1 регистра соединены соответственно с информационными входами 7.0 и 7.1 ячейки памяти 1.1. первый управляющий выход 10 которой является выходом разрешения записи 16 регистра, выход разрешения считывания 17 которого соединен с первым управляющим выходом 10 ячейки памяти 1.9, вход стирания 18 регистра соединен с третьим 13 управляющим входом ячейки памяти 1.3. Информационные выходы 8.0 и 8.1 ячеек памяти 1.9,1.10, 1.11 и 1.8 являются соответственно параллельными информационными выходами 19.0 и 19.1. 20.0 и 20.1, 21.0 и 21.1 и 22.0 и 22.1 регистра.

Регистр функционирует следующим образом. Пусть в исходном состоянии информация во всех ячейках памяти 1 регистра стерта, т.е Г-триггеры 2 и 3 этих ячеек находятся в нулевом состоянии и на выходах 8.0 и 8.1 ячеек памяти имеется значение О, на первых управляющих выходах 10 этих ячеек памяти - значение 1, на их вторых управляющих выходах 11 - значение О. Соответственно на выходах 16 и 17 регистра имеется значение О и такое же значение установлено на его входе 18.

Это состояние сохраняется до тех пор, пока на одном из последовательных информационных входов 1.5.0 или 15.1 регистра, т.е. на информационных входах 7.0 и или 7.1 ячейки памяти 1.1, не появится значение 1, т.е. на этих входах не будет выставлено значение первого разряда сдвигаемого кода. Как только такое значение появится на указанных входах регистра, соответствующий Г-триггер 2 или 3 ячейки памяти 1.1 перейдёт в единичное состояние и на ее информационном выходе 8.0 или 8.1 появится .значение Т, а на ее первом управляющем выходе 10, т.е. на выходе 16 регистра, появится значение О. Теперь значение 1 имеется уже на одном из информационных входов 7.0 или 7.1 ячейки памяти 1.2 и в

последней произойдет переключение, аналогичное рассмотренному переключению ячейки памяти 1.1. После этого переключится ячейка памяти 1.3 и т.д. до тех пор, пока не переключится ячейка памяти 1,8 и на ее

0 информационном выходе 8.0 или 8.1 т.е. на параллельном выходе 22.0 или 22.1 регистра, не появится значение 1 - первый разряд сдвигаемого кода достиг отведенной ему позиции регистра.

5 Одновременно с этим процессом продвижения первого разряда сдвигаемого кода по ячейкам памяти регистра после того, как на выходе 16 регистра появится значение О, что свидетельствует о записи информа0 ции с последовательных информационных входов 15.0 и 15.1 в ячейку памяти 1.1, на этих входах может быть выставлено значение О, т.е. информация с них может быть снята; Это состояние последовательных информа5 ционных входов 15.0 и 15.1 регистра, т.е. информационных входов 7.0 и 7.1 ячейки памяти 1.1, приводит к тому, что как только информация с ее информационных выходов 8.0 и 8.1 перепишется в ячейку памяти 1.2 и

0 на первом управляющем входе 19 последнего появится значение О, информация в ячейке памяти 1.1 будет стерта и на ее информационных выходах 8.0 и 8.1 появится значение О. Теперь значения О имеются

5 на информационных входах 7.0 и 7.1 ячейки памяти 1.2 и после того, как информация с информационных выходов 8.0 и 8.1 последней перепишется в ячейку памяти 1.3 и на ее первом управляющем выходе 10 появит0 ся значение О, информация в ячейке памяти 1.2 будет стерта так же, как и в ячейке памяти 1.1. Далее произойдет стирание информации в ячейке памяти 1.3 после того, как информация из нее перепишется в ячей5 ку памяти 1.4, и т.д. до тех пор, пока не произойдет стирание информации в ячейке памяти 1.7. Стирание.же информации в ячейке памяти 1.8 заблокировано значением 1, которое поступает на ее первый уп0 равляющий вход 9 с выхода инвертора 6.

Одновременно с этим процессом распространения стирания информации в ячейках памяти 1 после того, как на выходе 16 регистра появилось значение 1, чтосвиде5 тельствует о стирании информации в ячейке памяти 1.1, на информационные последовательные входы 15.0 и 15.1 регистра можно выставить значения, соответствующие второму разряду сдвигаемого кода, т.е. установить на одном из этих входов значение 1.

Теперь, как только информация будет стерта в ячейке памяти 1.2 и на ее первом управляющем входе 10 появится значение Г, произойдет запись информации в ячейку памяти 1.1. Процесс продвижения второго разряда по регистру аналогичен рассмотренному выше процессу продвижения первого разряда с той лишь разницей, что второй разряд распространяется только до ячейки памяти 1.6 включительно, поскольку запись информации в ячейку памяти 1.7 заблокирована значение О, поступающим с первого управляющего выхода 10 ячейки памяти 1.8 на первый управляющий вход 9 ячейки памяти 1.7. Более того, в процессе распространения второго разряда сдвигаемого кода по ячейкам памяти 1 регистра его будет отделять от продвигающегося перёд ним первого разряда сдвигаемого кода как минимум одна ячейка памяти 1, в которой информация стерта.

После того как второй разряд сдвигаемого кода будет записан в ячейку памяти 1.1 и на ее первом управляющем выходе 10, т.е. на выходе 16 регистра, появится значе- ние О, на его последовательных информационных входах 15.0 и 15.1 снова может быть выставлено значение О, что инициирует распространение стирания информации в ячейках памяти 1; которое достигнет в этот раз ячейки памяти 1.6,

Далее через последовательные информационные входы 15.0 и 15.1 регистра в него может быть послан третий разряд сдвигаемого кода, который достигнет ячей- ки памяти 1.4, затем снова инициирован процесс стирания, который распространится до ячейки памяти 1.3 включительно и, наконец, записан четвертый (последний) разряд сдвигаемого кода, который достиг- нет ячейки памяти 1.2, после чего в ячейке памяти 1.1 информация может быть стерта.

Таким образом, чередуя запись и стирание информации через последовательные информационные входы 15.0 и 15.1 регист- ра, достигается максимально плотное его заполнение информацией, при котором ячейки памяти 1.8, 1.6, 1.4 и 1.2, в которых записаны последовательно с первого по четвертый разряды сдвигаемого кода, чере- дуются с ячейками памяти 1.7, 1.5, 1.3, и 1.1, в которых информация стерта.

Очевидно, что когда в ячейке памяти 1.8 оказывается информация, то это может быть только первый разряд сдвигаемого ко- да, который и передается с ее информационных выходов 8,0 и 8.1 на параллельные информационнее выходы 22.0 и 22.1 регистра, признаком чего является появление значения О на первом управляющем выходе 10 ячейки памяти 1.8, которое поступает на второй управляющий вход 12 ячейки памяти 1.7. Если теперь оказывается, что информация в ячейке памяти 1.7 стерта, признаком чего является появление значения 1 на ее втором управляющем выходе 11, а в ячейке памяти 1.6 записана информация, то это может быть только второй разряд сдвигаемого кода и значение Г со второго управляющего выхода 11 ячейки памяти 1.7, поступая на первый управляющий вход 9 ячейки памяти 1.11, разрешает перепись в последнюю этого второго разряда из ячейки памяти 1.6. Признаком того, что в ячейке памяти 1.11 записан второй разряд, который с ее информационных выходов 8.0 и 8.1 поступает на параллельные информационные выходы 21.0 и 21.1 регистра, является появление значения Q на ее первом управляющем выходе 10. Это значение, в свою очередь, поступает на второй управляющий вход 12 ячейки памяти 1.5, и когда информация в последней будет стерта, на ее втором управляющем выходе 11 появится значение 1, которое, поступая на первый управляющий вход 9 ячейки памяти 1.10, разрешит перепись в эту ячейку памяти третьего разряда сдвигаемого кода из ячейки памяти 1.4, 8 которой в данной ситуации может появиться только этот третий разряд, Признаком того, что третий разряд сдвигаемого кода поступил на параллельные информационные выходы 20.0 и 20.1 регистра, т.е. на информационные выходы 8.0 и 8.1 его ячейки памяти 1.10, является появление значения О на ее первом управляющем выходе 10, которое поступает на второй управляющий вход 12 ячейки памяти 1.3. Если информация в последней стерта, то на ее втором управляющем выходе 11 появляется значение 1, которое, поступая на первый управ- ляющий.вход 9 ячейки памяти 1.9, разрешит перепись в нее четвертого разряда сдвигаемого кода из ячейки памяти 1.2, в которой в данной ситуаций может появиться только этот четвертый разряд, Признаком появления четвертого разряда сдвигаемого кода на информационных выходах 8.0 и 8.1 ячейки памяти 1.9, т.е. на параллельных информационных выходах 19.0 и 19.1 регистра, является появление значения О на первом управляющем выходе 10 этой ячейки памяти, а поскольку четвертый разряд сдвигаемого кода является последним и последним появляется на параллельных информационных выходах 19.0-и 19,1 регистра, это значение, поступая на выход 17 регистра, разрешает съем с его параллельных информационных выходов 19-22 параллельного кода.

Для следующей записи кода через последовательные информационные входы 15.0 и 15.1 регистра последний необходимо возвратить в состояние, аналогичное исходному. Это осуществляется подачей значе- ния 1 на вход стирания 18 регистра, которое, поступая на третий управляющий вход 13 ячейки памяти 1.3, вызывает появление на его первом управляющем выходе 10 этой ячейки памяти значения О. Это значение, поступая на первый управляющий вход 9 ячейки памяти 1,2, стирает в ней информацию, в результате чего на втором управляющем выходе 11 этой ячейки памяти появляется значение Г. которое поступа- ет на третий управляющий вход 13 ячейки памяти 1,5, вызывая появление на первом управляющем выходе 10 этой ячейки памяти значение О. Это значение, поступая на первый управляющий вход 9 ячейки памяти 1.4, стирает в ней информацию, в результате чего на втором управляющем выходе 11 этой ячейки памяти появляется значение 1, которое, в свою очередь, поступает на третий управляющий вход 13 ячейки памяти 1.7, вызывая появление на первом управляющем выходе 10 этой ячейки памяти значения О. Это значение, поступая на первый управляющий вход 9 ячейки памяти 1.6, стирает в ней информацию, в результате чего на втором управляющем выходе 11 этой ячейки появляется значение Г, которое, наконец, поступает на вход инвертора 6, вызывая появление на его выходе значения О, которое, поступив на первый управля- ющий вход 9 ячейки памяти 1.8, стирает информацию в последней. Этим заверша- етс5цпоелёдовательный процесс стирания информации в ячейках памяти 1.2,1.4, 1.6, и 1.8.

После того как произойдет стирание информации в ячейке памяти 1.4 и на ее втором управляющем выходе 11 появится значение 1, это значение, поступая на четвертый управляющий вход 14 ячейки памяти 1.5, вызовет появление на ее втором управляющем выходе 11 значения О, которое, поступив на первый управляющий вход 9 ячейки памяти 1.9. сотрет в ней информацию.

Аналогично стирание информации в ячейке памяти 1.6 вызовет стирание информации в ячейке памяти 1.10, а стирание информации в ячейке памяти 1,8-стирание информации в ячейке памяти 1.11.

Как только в ячейке памяти 1.9 информация будет стерта и значение О с ее информационных выходов 8,0 и 8.1 поступит на третий 13 и четвертый 14 управляющие входы ячейки памяти 1.2, на ее первом уп-

равляющем выходе 10 появится значение 1, которое, поступив на первый управляющий вход 9 ячейки памяти 1.1, разрешит запись информации в эту ячейку памяти с последовательных информационных входов 15.0 и 15.1 регистра. Аналогично стирание информации в ячейке памяти 110 разрешит перепись информации в ячейку памяти 1.3 из ячейки памяти 1.2, а стирание информации в ячейке памяти 1.11 - перепись информации в ячейку памяти 1,5 из ячейки памяти 1.4. Таким образом, очередной процесс записи кода в регистр через последовательные информационные входы 15.0 15.1 последнего можно начинать, не дожидаясь полного стирания информации в регистре, а, например, сразу после того как информация будет стерта в его ячейке памяти 1.9 и на ее первом управляющем выходе 10, т.е. на выходе 17 регистра, появится значение. .

Из сказанного видно, что предложенный регистр работает так же, как и прототип (2), образованный ячейками памяти 1.1-1.8, т.е. осуществляет асинхронный сдвиг информации в режиме запрос-ответ, организованный по реальным задержкам элементов, до тех пор, пока разряды сдвигаемого кода не попадут вы отведенные им позиции (ячейки памяти) регистра. Как только такое попадание происходит, осуществляется передача разрядов кода на параллельные информационные выходы 22-19 регистра через его ячейки памяти 1.8- 1.11; что позволяет произвести параллельное считывание информации из регистра.

Таким образом, предложенное техническое решение расширяет область применения асинхронного регистра типа pipeline за счет осуществления параллельного считывания из него информации.

В предложенном устройстве используются двухвходовые Г-триггеры и логические элементы ЙЛЙ-НЕ с четырьмя входами, что допускает его реализацию в современных технологических базисах интегральных микросхем, например, на КМОП-транзисто- рах.

Формула изобретения Асинхронный последовательный регистр, содержащий 2п ячеек памяти, п-число разрядов регистра, каждая из которых состоит из двух Г-триггеров и первого элемента ИЛИ-НЕ, первый и второй входы которого соединены с выходами Г-триггеров данной ячейки памяти, первые входы Г-триггеров каждой ячейки памяти, кроме первой, соединены с выходами Г-триггеров предыдущей ячейки памяти, а первые входы

Г-триггеров первой ячейки памяти являются информационными входами регистра, выходы Г-триггеров 2п-й ячейки памяти являются

информационными выходами n-го разряда регистра, вторые входы Г-триггеров каждой ячейки памяти, кроме стирания регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный регистр сдвига | 1984 |

|

SU1184012A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| Сдвиговый регистр | 1983 |

|

SU1624528A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1259337A1 |

| Регистр сдвига | 1978 |

|

SU809383A1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Параллельный логический мультиконтроллер | 2016 |

|

RU2634199C1 |

Изобретение относится к вычислительной технике и может быть использовано для преобразования последовательного кода в параллельный. Цель изобретения - расширение области применения асинхронного последовательного регистра путем обеспечения параллельного считывания из него информации. Регистр содержит Зп-1 ячеек памяти, каждая из которых состоит из двух Г-триггеров и элемента ИЛИ-НЕ, где ri - число разрядов сдвигаемого кода, и инвертор, при этом ячейки памяти со второй по (2п-1)-ю содержат г элемент ИЛИ-НЕ, а выходы последних п ячеек памяти соединены с параллельными информационными выходами регистра. Поставленная цель достига-. ется введением в регистр ячеек с (2п+1)-й по (Зп-1)-ю, с помощью которых индицируется завершение процесса записи информации в регистр. 1 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ячейка памяти для буферногоРЕгиСТРА | 1979 |

|

SU799010A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Апериодические автоматы /Под ред | |||

| В.И.Варшавского | |||

| - М.:Наука, 1976, с.308, рис, 4.33,6). | |||

Авторы

Даты

1993-03-30—Публикация

1990-07-16—Подача